# **Original Paper**

Received February 19, 2025; accepted May 14, 2025; Date of publication May 27, 2025. The review of this paper was arranged by Associate Editor Francisco D. Freijedo and Editor-in-Chief Heverton A. Pereira Divital Object Identifier http://doi.org/10.18618/REP.e202538

# Single-Phase Rectifier with Cascaded-Transformer to Supply a Three-Phase Induction Motor with Open-End Windings

Antonio D. D. Almeida<sup>1</sup>, Bruna S. Gehrke<sup>2</sup>, Nady Rocha<sup>2,\*</sup>, Edgard L. L. Fabricio<sup>3</sup>, Carolina A. Caldeira<sup>4</sup>, Gleice M. S. Rodrigues<sup>5</sup>, Isaac S. de Freitas<sup>2</sup>

<sup>1</sup>Federal Institute of Education, Science and Technology of Bahia (IFBA) - Feira de Santana - BA - Brazil

<sup>2</sup>Federal University of Paraíba (UFPB) - João Pessoa - PB - Brazil

<sup>3</sup>Federal Institute of Paraíba (IFPB) - João Pessoa - PB - Brazil

<sup>4</sup>Federal Institute of Education, Science and Technology of Sergipe (IFS) - Nossa Sra. do Socorro - SE - Brazil

<sup>5</sup>EDP Espírito Santo Energy Distribution SA - Vitória- ES - Brazil

e-mail: antonio.dutra@ifba.edu.br, bruna.gehrke@cear.ufpb.br, nadyrocha@cear.ufpb.br\*, edgard.fabricio@ifpb.edu.br, carolina.caldeira@ifs.edu.br, gleicem.rodrigues@edp.com, isaacfreitas@cear.ufpb.br \* Corresponding author.

**ABSTRACT** This paper presents a single-phase to three-phase AC-DC-AC step-down converter with a symmetrical DC-link voltage ratio. The proposed converter architecture is well-suited for rural distribution grid applications, where a high-voltage single-phase grid is required to transmit energy over long distances while minimizing conduction losses. The converter consists of two cascaded H-bridge converters connected via transformers and two three-phase inverters supplying an open-end winding induction motor (OEWIM). The level-shifted pulse-width modulation (LSPWM) strategy is employed to synthesize the converter voltages. A proportional-integral (PI) controller regulates the overall DC-link voltages, while a hysteresis controller maintains the balance of the individual DC-link voltages. Additionally, a resonant PI controller ensures a sinusoidal grid current, and a Phase-Locked Loop (PLL) is used to achieve a high power factor in the grid. Compared to a conventional two-level leg topology, the proposed configuration reduces harmonic distortion and semiconductor power losses while ensuring a high power factor. Simulation and experimental results validate the effectiveness of the PWM and control strategies.

**KEYWORDS** AC-DC-AC multilevel converters, cascaded-transformers converter, open-end winding induction motor, single-phase to three-phase.

# I. INTRODUCTION

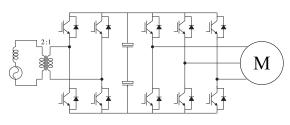

Most electrical grids in the countryside are not three-phase but single-phase, which requires power electronic devices to supply three-phase loads. Three-phase loads are widely used in farms and industrial plants. They present better dynamic performance and can achieve high power levels. On the other hand, single-phase to three-phase converters appear as a possibility to overcome the lack of a three-phase grid. Hence, AC-DC-AC conversion has been the object of study for several years in applications such as three-phase motor drive [1]–[4], uninterrupted power supply (UPS) [5], distributed generation system [6] and power quality conditioner [7] and [8]. The conventional single-phase to three-phase AC-DC-AC converter is presented in Fig. 1.

In high-power medium-voltage drives, the AC-DC-AC multilevel converters have been widely applied as a viable solution to overcome current and voltage limitations of power switches. These converters can generate output voltage waveforms with a large number of levels by using multiple power sources and employing switching

devices with lower voltage ratings. In addition, the harmonic distortion, the rate of change of voltage over time (dv/dt), which affects the stress on power switches, the electromagnetic interference (EMI), and the switching losses are reduced [9]. Overall, multilevel converters seek better energy quality from the grid to the loads. In this context, topologies derived from basic module series connections are optimal solutions for high-voltage applications. Among these, the most popular topology is the series H-bridge, implemented with cascaded transformers [10]–[12] and without cascaded transformers [13]–[15]. Additionally, the open-end winding (OEW) concept also appears as an option to achieve multilevel features through series-connection of three-phase converters [16], [17].

Modern applications are increasingly using power electronics devices with stricter requirements regarding the performance of electrical machines. The open-end winding induction machine (OEWIM) is increasingly becoming an interesting alternative due to its advantages over the conventional single-inverter induction motor: 1) multilevel

FIGURE 1. Conventional single-phase to three-phase converter.

voltage, enabling a more effective current control, and consequently less torque ripple; 2) greater reliability, since it is capable to operate in the occurrence of faults [18], [19]. The OEWIM can be classified into three types based on the DC power supply configuration of the inverters. The first type uses a single power source supplying both inverters, offering a simple and cost-effective solution. However, this configuration allows zero-sequence current circulation, which does not contribute to torque production and results in additional losses. The second type employs a hybrid approach, where one inverter is powered by a dedicated DC source while the other operates with a floating capacitor. This solution eliminates zero-sequence current but introduces low-frequency harmonic components. The third type utilizes isolated DC sources for each inverter, effectively eliminating zero-sequence current and enhancing system reliability in case of inverter failure. However, this approach increases system costs due to the need for an additional DC source, which can be a limiting factor [20].

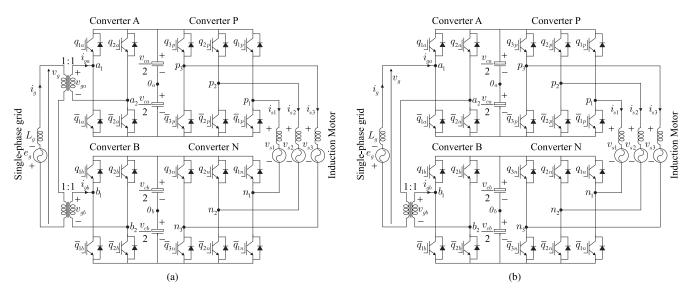

This paper proposes an AC-DC-AC topology that resolves the aforementioned issues by incorporating multilevel features while supplying a three-phase open-ended load from a single-phase grid. The rectifier side comprises two series-connected transformers on the primary side, supplying two H-bridge converters through a single-phase grid. On the other hand, the inverter side is composed of two three-phase VSI converters supplying an OEWIM, as shown in Fig. 2. Although the proposed converter has a higher number of power switches compared to conventional converters, it offers a suitable solution for applications where only a single-phase grid is available, such as in rural areas. Since the voltage rating of the switches is reduced, conduction and switching losses can also be minimized.

Overall, the proposed converter provides multilevel features on both the rectifier and inverter sides with galvanic isolation, thereby avoiding circulating current. Despite the presence of a common-mode voltage, zero-sequence current cannot flow because the inverters are supplied by isolated DC sources. This configuration effectively eliminates the common-mode voltage from the actual voltage applied to the motor windings [21], [22]. Additionally, this topology ensures a high power factor close to unity, DC-link voltage control, and controlled output voltages.

The low-frequency transformers (LFTs) may be used to step down the voltage level and provide galvanic isolation between the converters, enabling multilevel voltage operation at both the input and output of the system. The topology can be modified by removing one of the transformers while still maintaining insulation between the DC links. However, to achieve the high input voltage, additional series-connected converters may be necessary. For this reason, in remote rural areas where size and weight are less critical, the version of the converter using two LFT is considered the most suitable solution. However, if the voltage level is compatible with the converter's ratings and galvanic isolation is not required, one transformer can be safely removed, as illustrated in Fig. 2(b). This configuration allows H-bridge converters to interface with a single-phase grid. On the output side, the system includes two three-phase voltage source inverters (VSIs), which supply an open-end winding induction motor (OEWIM), as depicted in Fig. 2. This arrangement can contribute to improved overall system efficiency.

The contributions of the proposed solution include improved power quality on both the grid and load sides. On the grid side, multilevel voltage is utilized to maintain Total Harmonic Distortion (THD) within standard limits while ensuring a high power factor. On the load side, the OEWIM motor drive benefits from reduced torque ripple, elimination of common-mode voltage in the motor windings, and the use of multilevel voltage. Furthermore, an efficient and straightforward DC-link balancing control is implemented, enhancing overall system performance.

The first version of this paper was presented in [23]. This current version includes all content from the original, with the following additions:

- New analysis and results, including a novel Level-shift PWM (LSPWM) approach and its correlation with single-carrier-based PWM.

- 2) A DC-link balance control method based on the selection of switching states.

- A comparative analysis of harmonic distortion and semiconductor losses, demonstrating reduced harmonic distortions and power losses.

- 4) New simulation and experimental results.

In this way, this paper is organized as follows the proposed structure and its main equations are presented in Section II; the LSPWM strategy for grid and load sides is presented in Section III; a suitable control strategy is presented in Section IV to balance the DC-link voltage by choosing proper switching states, and to ensure sinusoidal grid current, high power factor, and controlled output voltages; analysis in terms of harmonic distortion and semiconductor losses are discussed in Section V; simulation and experimental results under same conditions are presented in Section VI and VII, respectively. Finally, overall conclusions are summarized in Section VIII.

# **II. SYSTEM MODEL**

The proposed topology, illustrated in Fig. 2, is composed of two cascaded H-bridge rectifiers (Converters A and

FIGURE 2. Proposed single-phase to three-phase converter with two DC links. (a) With two cascaded transformers. (b) With one cascaded transformer.

B), isolated by two transformers ( $T_a$  and  $T_b$ ), and two three-phase inverters feeding an OEWIM. The transformers ensure galvanic isolation between the grid and power converter, which is required in high-voltage applications, allowing connections of many motor drive systems at the secondary as needed. The system model equations of the input side, referred to the transformer's primary side, are

$$e_g = r_g i_g + l'_g \frac{di_g}{dt} + v_g \tag{1}$$

$$l'_g = l_g + 2l_t \tag{2}$$

$$i_{gk} = ni_g \tag{3}$$

$$v_g = n(v_{ga} + v_{gb}) \tag{4}$$

$$v_{gk} = v_{k10_k} - v_{k20_k} \tag{5}$$

where k = a, b denotes the two converters on the rectifier side;  $e_g$  is the grid voltage;  $i_g$  is the grid current;  $i_{gk}$  are the rectifier currents; and n is the transformer turns ratio (with n = 1). The variables  $v_{gk}$  represent the rectifier output voltages, while  $v_{k10_k}$  and  $v_{k20_k}$  are the rectifier pole voltages. The impedance  $L_g$  comprises the resistance  $r_g$  and the inductance  $l'_g$ , which includes the leakage inductance  $l_t$  of each transformer (referred to the grid side) and the equivalent input inductance  $l_g$ .

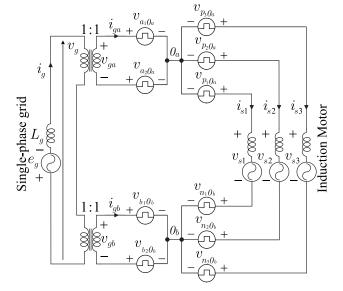

The converters P and N are feeding an OEWIM. As shown in Fig. 3, the voltages applied to the machine terminals are denoted as  $v_{sj}$ , with j = 1, 2, 3. Thus, the converter output voltages can be written as:

$$v_{sj} = v_{pj0_a} - v_{nj0_b} - v_{0_a0_b} \tag{6}$$

where  $v_{pj0_a}$  and  $v_{nj0_b}$  are the pole voltages of converters P and N, respectively.

$$v_{0_a 0_b} = \frac{1}{3} \sum_{j=1}^{3} (v_{pj0_a} - v_{nj0_b})$$

(7)

FIGURE 3. Equivalent circuit of the proposed converter.

where  $v_{0_a 0_b}$  is the voltage between the DC-link midpoints  $0_a$  and  $0_b$ .

#### **III. PWM STRATEGY**

#### A. PWM Strategy of Converters A and B

A level-shifted PWM (LSPWM) strategy is used to define the switching states of the rectifiers (converters A and B) in the proposed converter. The grid-side converter voltage,  $v_g^*$ , is modulated to be synthesized by the two rectifiers. The number of synthesized voltage levels and the required carrier signals depend on the DC-link voltage ratio. In this paper, the DC-link voltage ratio is 1:1, so the proposed converter can synthesize up to five voltage levels. These levels are  $v_g =$  $[-v_{cT}^*, -v_{cT}^*/2, 0, v_{cT}^*/2 \text{ and } v_{cT}^*]$ , where  $v_{cT} = v_{ca} + v_{cb}$ . Table 1 summarizes all the possible switching states and

Eletrônica de Potência, Rio de Janeiro, v. 30, e202538, 2025.

| Voltage             | $q_{1a}q_{2a}q_{1b}q_{2b}$ | $i_g \ge 0$  |              | $i_g < 0$    |              |

|---------------------|----------------------------|--------------|--------------|--------------|--------------|

|                     |                            | $v_{ca}$     | $v_{cb}$     | $v_{ca}$     | $v_{cb}$     |

| $v_{cT}$            | 1010                       | $\uparrow$   | $\uparrow$   | $\downarrow$ | $\downarrow$ |

|                     | 0010                       | _            | $\uparrow$   | _            | $\downarrow$ |

| $\frac{v_{cT}}{2}$  | 1000                       | 1            | _            | $\downarrow$ | _            |

| 2                   | 1011                       | 1            | _            | $\downarrow$ | _            |

|                     | 1110                       | -            | $\uparrow$   |              | $\downarrow$ |

|                     | 0000                       | -            | -            | -            | -            |

| 0                   | 0011                       | _            | _            | _            | _            |

|                     | 0110                       | $\downarrow$ | $\uparrow$   | $\uparrow$   | $\downarrow$ |

|                     | 1001                       | 1            | $\downarrow$ | $\downarrow$ | $\uparrow$   |

|                     | 1100                       | _            | _            | _            | _            |

|                     | 1111                       | _            | _            | _            | _            |

| $-\frac{v_{cT}}{2}$ | 0001                       | _            | $\downarrow$ | _            | 1            |

|                     | 0100                       | $\downarrow$ | _            | $\uparrow$   | _            |

|                     | 0111                       | $\downarrow$ | _            | $\uparrow$   | -            |

|                     | 1101                       | _            | $\downarrow$ | _            | 1            |

| $-v_{cT}$           | 0101                       | 1            | 1            | $\downarrow$ | 4            |

TABLE 1. Generated grid voltage, switching states, and their effect on the DC-link voltages depending on the polarity of the current  $i_q$ .

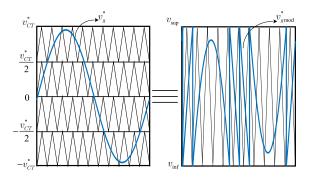

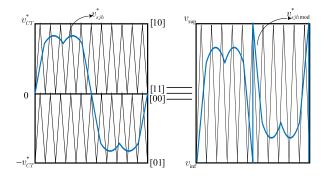

their output voltages. In addition, to generate  $v_g$  with the maximum number of levels, four triangular carriers are required, as shown in Fig. 4. Each carrier is placed between two nearest voltage levels, forming a region known as a sector.

Generally, to generate N levels, N-1 triangular carriers are required. However, most microcontrollers do not support multiple level-shifted carriers. As an alternative, an emulated single-carrier PWM strategy is proposed in [24]. This approach utilizes a single-carrier PWM operating between the limits  $v_{sup}$  and  $v_{inf}$ , where normally  $v_{sup} = v_{cT}^*/2$  and  $v_{inf} = 0$ . The modulating waveform  $(v_g^*)$  is modified  $(v_{gmod}^*)$ according to the sector, i.e.:

$$v_{gmod}^* = |v_g^*| - V_{off-set} \tag{8}$$

where  $V_{off-set}$  is a constant offset. For instance, if  $v_{cT}^*/2 < v_g^* \le v_{cT}^*$  (see Fig. 4), the  $V_{off-set} = v_{cT}^*/2$  and if  $v_{cT}^*/2 \le v_g^* < 0$ , the  $V_{off-set} = 0$  and so on. Then, a single carrier is compared with the modified modulating waveform  $v_{gmod}^*$  to select the proper switching states. All possible switching states are shown in Table 1. These states are shown following the sequence  $[q_{1a}q_{2a}q_{1b}q_{2b}]$ .

#### B. PWM Strategy of Converters P and N

The LSPWM is also applied to converters at the load side. Given the three-phase reference output voltages  $v_{sj}^*$ , j = 1, 2, 3, an auxiliary voltage is introduced as common mode reference  $v_h^*$ . Thus obtaining the new reference voltage  $v_{sjh}^*$

$$v_{sjh}^* = v_{sj}^* + v_h^* \tag{9}$$

The auxiliary voltage  $(v_h^*)$  is normalized in function of  $(\mu)$  between its maximum  $v_{hmax}^*$  and minimum  $v_{hmin}^*$  possible

FIGURE 4. Grid side level-shifted PWM Strategy and its equivalent single-carrier modulation.

values, as presented in [25],

$$v_h^* = \mu v_{hmax} + (1 - \mu) v_{hmin}$$

(10)

$$v_{hmax} = \frac{v_{cT}}{2} - \max(v_{s1}^*, v_{s2}^*, v_{s3}^*)$$

(11)

$$v_{hmin} = -\frac{v_{cT}}{2} - \min(v_{s1}^*, v_{s2}^*, v_{s3}^*)$$

(12)

The reference voltages  $(v_{sjh}^*)$  are applied in the LSPWM strategy to define the switching states of converters P and N. The output converter's voltages generate up to three voltage levels using this technique, which would mean two triangular carriers per phase, as shown in Fig. 5. The modulating approach can be emulated using a single-carrier per phase, as implemented for the grid side. The switching states for each level are also shown in these figures.

FIGURE 5. Load side level-shifted PWM Strategy and its equivalent single-carrier modulation.

# **IV. CONTROL STRATEGIES**

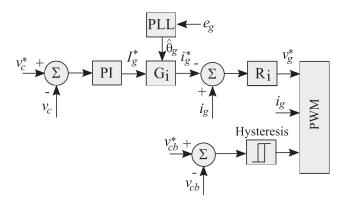

Fig. 6 presents the control block diagram of the proposed configuration. Initially, the two DC-link voltages are controlled through the average DC-link voltage  $[v_c = (v_{ca} + v_{cb})/2]$ . The voltage  $v_c$  is adjusted to its reference value  $v_c^*$  using a proportional-integral (PI) controller. This controller determines the amplitude of the reference grid current  $(I_g^*)$ , located on the primary side of the transformer. The reference current  $(i_g^*)$  is synchronized with the grid voltage  $(e_g)$  using a Phase Locked-Loop (PLL). This ensures a high power factor on the grid side. In addition, a resonant PI controller  $(R_i)$  [26] is used to control the grid current. The output of

4

this controller is the reference voltage  $v_g^*$ , which is used in the PWM strategy.

Once the average DC-link voltage is controlled, an individual control is applied to one of the DC links to ensure that both are properly regulated. Since different switching states can generate the same voltage vector, each with a distinct effect on the DC-link currents, these redundancies can be utilized to balance the DC-link voltages effectively. This can be observed by the DC-link currents, which are given by

$$i_{ca} = q_{1a}i_{ga} - q_{2a}i_{ga} - q_{3p}i_{s3} - q_{2p}i_{s2} - q_{1p}i_{s1}$$

(13)

$$i_{cb} = q_{1b}i_{gb} - q_{2b}i_{gb} + q_{3n}i_{s3} + q_{2n}i_{s2} + q_{1n}i_{s1}$$

(14)

Each switching state of converters A and B can increase or decrease the energy transferred from the grid to the load. When the energy transferred from the grid is bigger than the load energy, the capacitor voltage rises (i.e.,  $i_{ck} > 0$  with k = a, b); otherwise, the capacitor voltage decreases. The effect of each switching state on the DC-link voltage is summarized in Table 1. The hysteresis control continuously monitors one of the DC-link voltages and adjusts it when it reaches the specified upper or lower limit. When the lower limit is reached, specific switching states are applied during the PWM period to charge the DC-link; otherwise, when the upper limit is reached, switching states are selected to discharge the DC-link. The specified limits form the hysteresis band, ensuring that the controlled voltage fluctuates within the allowed range,  $\Delta v_{cb}$ .

To maintain  $v_{cb}$  between the hysteresis band, the voltage vectors are chosen as follows:

- 1) if  $v_{cb} v_{cb}^* > \Delta_{vcb}$  a voltage vector is selected to decrease  $v_{cb}$  or to increase  $v_{ca}$ .

- 2) if  $v_{cb} v_{cb}^* < -\Delta_{vcb}$  a voltage vector is selected to increase  $v_{cb}$  or to decrease  $v_{ca}$ .

For example, if  $0 < v_g^* < \frac{v_{cT}}{2}$  and the grid current is positive. In this case, the voltage vectors 0010 and 1110 increase the voltage  $v_{cb}$ , while the vectors 1000 and 1011 increase the voltage  $v_{ca}$ .

FIGURE 6. System block control diagram of proposed configuration.

# V. COMPARATIVE ANALYSIS

The conventional and proposed topologies are analyzed and compared regarding harmonic distortions and semiconductor losses. All analyses are performed under steady-state open-loop simulations considering the same operation conditions, as detailed in Table 2.

Two voltage levels are investigated while keeping the same power in both cases. In the first scenario (lower voltage), the grid voltage is 220 V and the output voltage is 110 V. In the second scenario (higher voltage), the grid voltage is 440 V and the output voltage is 220 V. In addition, the topologies are investigated: (*i*) operating with the same carrier frequency ( $f_c$ ), and (*ii*) with different carrier frequencies to achieve the same grid current THD.

TABLE 2. Simulation parameters for comparative analysis.

| Parameter         |       | Value                 |

|-------------------|-------|-----------------------|

| Grid voltage      | $e_g$ | 220 V and 440 V (RMS) |

| Grid impedance    | $Z_g$ | 5%                    |

| Load voltage      | $v_l$ | 110 V and 220 V (RMS) |

| Grid frequency    | $f_g$ | 60 Hz                 |

| Carrier frequency | $f_c$ | 10 kHz                |

| $3\phi$ load      | $P_l$ | 5 kW                  |

| PF load           | PF    | 0.8                   |

# A. Number of Components and Voltage Levels

A comparison of different single-phase to three-phase topologies with the proposed topology, in terms of power devices and generated voltage levels, is presented in Table 3. All the analyzed topologies have the same number of power switches.

| TABLE 3. Comparison | n of different single-phase | to three-phase topologies. |

|---------------------|-----------------------------|----------------------------|

|---------------------|-----------------------------|----------------------------|

|                | Deserved | Single-carrier/     | Neutral-Point |

|----------------|----------|---------------------|---------------|

|                | Proposed | Double-carrier [27] | Clamped (NPC) |

| Diodes         | -        | -                   | 10            |

| Inductors      | 1        | 4                   | 1             |

| Switches       | 20       | 20                  | 20            |

| DC links       | 2        | 2                   | 1             |

| Low-frequency  | 2.*      | 1                   | 1             |

| transformers   | 2        | 1                   | I             |

| Input          | 5        | 3                   | 5             |

| voltage levels | 5        | 5                   | 5             |

| Output         | 9        | 5/7                 | 9             |

| voltage levels | 9        | 577                 | 2             |

<sup>\*</sup> can be reduced to one.

The topology presented in [27] has a transformer with its secondary side powering the rectifiers in parallel, which allows current circulation and requires four filter inductors. Moreover, this topology generates multilevel output voltages with fewer and unevenly distributed levels. Another topology that can be considered is an NPC topology with a configuration identical to the one shown in Fig. 1. This topology would generate the same number of voltage levels as the proposed one. However, this topology has ten clamping diodes, and the transformer processes 100 % of the total power. On the other hand, the proposed converter uses two transformers, each processing only half of the total power (see Fig. 2(a)). Alternatively, a single transformer with a center tap on the secondary can be used to supply the rectifiers in isolation. In addition, as shown in Fig. 2(b), one transformer can be removed if the grid voltage level is compatible with the converter's voltage.

The following comparison is done between the proposed topology (see Fig. 2(a)) and the conventional topology (see Fig. 1).

#### B. Harmonic Distortions

The total harmonic distortion (THD) and weighted total harmonic distortion (WTHD) are used to evaluate the quality of the grid current and load voltage waveforms, respectively. The results were obtained using the equations presented in [28] and are summarized in Table 4.

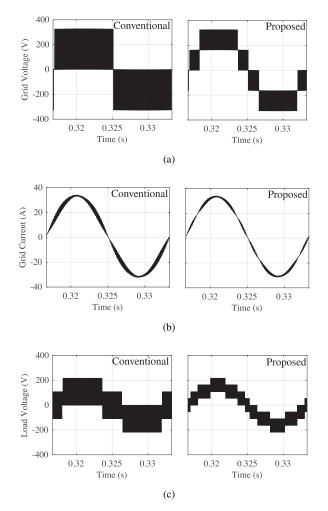

The simulated waveforms of the proposed and conventional configurations operating with the same carrier frequency ( $f_c = 10$  kHz) and in the first scenario (lower voltage) are shown in Fig. 7. The topologies present a THD of 5% and 2.68%, for conventional and proposed topologies, respectively. In addition, the output voltage WTHD values are 0.28% and 0.12%, respectively. Thus, the proposed topology achieves a 46.4% reduction in THD and a 57% reduction in WTHD compared to the conventional one. Similar results were observed in the second scenario (higher voltage).

| TABLE 4. | Harmonic | distortion | analysis. |

|----------|----------|------------|-----------|

|----------|----------|------------|-----------|

|                                 | Conventional | Proposed |

|---------------------------------|--------------|----------|

| THD ( $f_c = 10 \text{ kHz}$ )  | 5 %          | 2.68 %   |

| WTHD ( $f_c = 10 \text{ kHz}$ ) | 0.28 %       | 0.12 %   |

| $f_c \; (\text{THD} = 5\%)$     | 10 kHz       | 5.5 kHz  |

The results of the proposed configuration can be attributed to the higher number of voltage levels on both the grid and load sides (see Fig. 7). The proposed topology generates five levels on the grid side and nine on the load side, whereas the conventional topology generates three levels on the grid side and five levels on the load side. In this way, the proposed topology can be designed with smaller passive filters or can operate with a lower carrier frequency to achieve the same performance as the conventional topology. The first option may result in a reduction in manufacturing costs, while the second option leads to reduced power losses, which can translate to a longer lifespan for the power switches and energy savings. Table 4 shows the carrier frequencies for each topology operating with 5% of THD. It is noteworthy that the proposed converter can reduce the

FIGURE 7. Simulated waveforms comparing the conventional and proposed converters. (a) Grid voltage. (b) Grid current. (c) Load voltage.

switching frequency, resulting in a frequency 45% lower than that of the conventional topology.

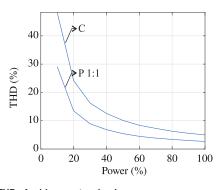

At last, the THD of grid current is evaluated over a range of load power, as shown in Fig. 8. For this analysis, the grid impedance is kept constant. As can be seen, the proposed topology demonstrates better performance across the entire power range.

FIGURE 8. THD of grid current vs load power.

#### C. Semiconductor losses analysis

The semiconductor losses include both conduction and switching losses of the transistor and its anti-parallel diode. The results were obtained using PSIM, with the switch model developed based on the Littelfuse MG0675S-BN4MM datasheet [29]. This device was chosen to support the analyzed voltage and current levels, with a maximum rating of 600 V and 75 A.

Conduction and switching losses on the switches can be found by applying (15) and (16), respectively [30].

$$P_{COND} = V_{CEO}I_{AVG} + R_c I_{RMS}^2 \tag{15}$$

$$P_{SW} = \frac{1}{2\pi} \int_0^{2\pi} W(\omega t) d(\omega t) \tag{16}$$

where  $V_{CEO}$  is the IGBT on-state zero current collector-emitter voltage drop,  $R_c$  is the collector-emitter on-state resistance, W is the switching loss energy shown in (17).

$$W(\omega t) = k_0 + k_1 i(\omega t) + k_2 i(\omega t)^2$$

(17)

where  $k_0$ ,  $k_1$  and  $k_2$  are coefficients that represent the contributions of energy loss by switching (turn on and turn off). These coefficients can be obtained with linear regression through a second-order polynomial from the datasheet energy curves provided by the manufacturer.

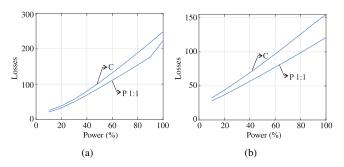

Fig. 9 presents the semiconductor losses for the conventional (C) and proposed (P 1:1) topologies. The losses are categorized into conduction and switching losses for both the rectifier and inverter, as indicated by the labels. As mentioned earlier, two sets of voltages levels were investigated, the first with lower voltage, as shown Figs. 9(a) and 9(b), and the second for higher voltage, as shown in Figs. 9(c) and 9(d). The losses are normalized based on conventional losses, representing 285 W for the first case and 160 W for the second case.

Two scenarios are investigated for the two sets of voltages:

- Scenario *i* topologies operating with the same carrier frequency, i.e., *f<sub>c</sub>* = 10kHz. This scenario is presented in Figs. 9(a) and 9(c);

- Scenario *ii* topologies operating with the same THD = 5%, which means different carrier frequencies per topology. These frequencies are shown in Table 4. This scenario is presented in Figs. 9(b) and 9(d).

In both scenarios, the proposed topology presents lower losses than the conventional one, with its efficiency being maximized in scenario *ii*. For lower voltage applications, the P 1:1 reaches 25% lower losses compared to the C topology, considering the same THD (i.e., 5% of THD) (see Fig. 9(b)). On the other hand, for higher the voltage applications, the proposed topology becomes even more efficient, as shown in Fig. 9(d), achieving 30% lower losses than the C topology. As already mentioned, the THD advantage of the proposed topology can be leveraged to reduce switching losses by operating at a lower switching frequency. Furthermore, the

FIGURE 9. Semiconductor losses analysis. (a) and (b)  $V_g$  and  $V_l$  equal to 220V and 110V, respectively. (c) and (d)  $V_g$  and  $V_l$  equal to 440V and 220V. (a) and (c) Topologies operating with the same carrier frequency  $f_c = 10$  kHz (scenario *i*). (b) and (d) Topologies operating with the same THD = 5% (scenario *ii*).

proposed topology becomes even more attractive for higher voltages and lower current applications.

Semiconductor power losses are illustrated in Fig. 10 for a power range of 10% to 100% of nominal load power (5 kW). The results indicate that the proposed topology is consistently more efficient than the conventional one at all power levels, with an efficiency advantage for higher power. For this analysis, the carrier frequency was maintained at 10 kHz to ensure optimal THD performance, as shown in Fig. 8.

FIGURE 10. Semiconductor losses for different load power. (a) For 220/110 V. (b) For 440/220 V.

Eletrônica de Potência, Rio de Janeiro, v. 30, e202538, 2025.

#### **VI. SIMULATION RESULTS**

Computer simulations were carried out using PSIM software. The circuit parameters are detailed in Table 5. The system supplies an RL load rated at 460 W with a power factor of 0.8, connected with open terminals.

TABLE 5. Parameters used in the simulated and experimental results.

| Parameter               |       | Value        |

|-------------------------|-------|--------------|

| Grid voltage            | $e_g$ | 127 V (RMS)  |

| Grid inductance         | $l_g$ | 6.7 mH       |

| Grid resistance         | $r_g$ | 0.1 Ω        |

| Grid frequency          | $f_g$ | 60 Hz        |

| Transformers turn ratio | n     | 1:1          |

| Load voltage            | $v_l$ | 77.7 V (RMS) |

| Load frequency          | $f_l$ | 60 Hz        |

| DC-link capacitance     | C     | 2200 µF      |

| Carrier frequency       | $f_c$ | 10 kHz       |

| DC-link Voltage         | $v_c$ | 210 V        |

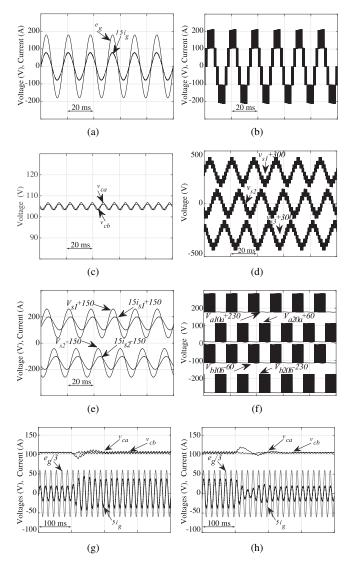

The simulation results are presented in Fig. 11 for the proposed topology. Fig. 11(a) shows waveforms of the grid voltage  $(e_g)$  and current  $(i_g)$ , which are in phase, resulting in a power factor close to unity. The grid voltage is 127 V and the grid current is 3.62 A. The current THD achieved 3.18 %, thus demonstrating the current control's correct operation. The results indicate that the grid current THD was lower than that specified by the standard. Fig. 11(b) shows the converter input voltage waveforms, which have five voltage levels. The DC-link voltages  $v_{ca}$  and  $v_{cb}$  are well regulated to 105 V (see Fig. 11(c)).

Fig. 11(d) shows the output converter voltages  $(v_{s1}, v_{s2}$  and  $v_{s3}$ ). These voltages present nine levels, as expected. Fig 11(e) shows the output converter currents  $(i_{s1} \text{ and } i_{s2})$  with 2.3 A and their corresponding average output voltage. The output currents THD was 0.45 %. The average switching frequencies  $f_{sw}$  per leg can be obtained from pole voltages. Fig 11(f) shows them  $(v_{a10a}, v_{a20a}, v_{b10b} \text{ and } v_{b20b})$ , all power switches operate during half circle which means  $f_{sw} = 5 \text{kHz}$ .

Figs. 11(g) and 11(h) illustrate the simulated waveforms during a load transient. To evaluate the dynamical performance of the system, a step change was applied in the load, varying from 50  $\Omega$  to 37.5  $\Omega$ , and vice versa. As can be seen, the voltages  $v_{ca}$  and  $v_{cb}$  were well regulated, remaining at half of the DC-link voltage, i.e, 105 V. These results demonstrate the proper operation of the implemented control strategy.

# **VII. EXPERIMENTAL RESULTS**

The proposed topology was implemented in the laboratory using the same simulation parameters to validate the results. Due to equipment and component limitations, the experiments were conducted at reduced voltage and current levels. The experimental setup was based on a digital

FIGURE 11. Simulation results. (a) Grid's voltage  $(e_g)$  and current  $(i_g)$ . (b) Input voltage  $(v_g)$ . (c) Voltages  $v_{ca}$  and  $v_{cb}$ . (d) Load voltages  $(v_{s1}$  and  $v_{s2}$ ). (e) Average load voltages  $(v_{s1}$  and  $v_{s2})$  and currents  $(i_{s1}$  and  $i_{s2})$ . (f) Rectifier pole voltages  $(v_{a10a}, v_{a20a}, v_{b10b}$  and  $v_{b20b}$ ). (g) Transient response of  $v_{ca}$  and  $v_{cb}$ ,  $e_g$  and  $i_g$ , for load increasing. (h) Transient response of  $v_{ca}$  and  $v_{cb}$ ,  $e_g$  and  $i_g$ , for load decreasing.

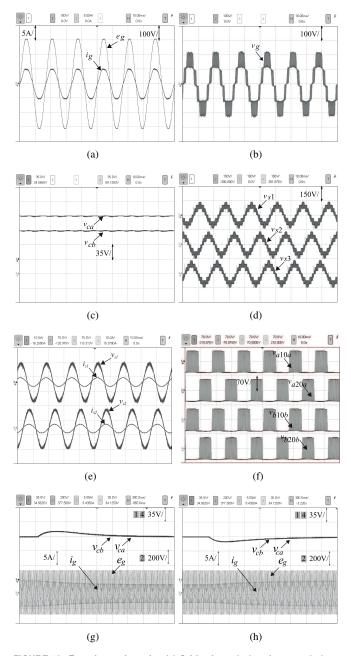

signal processor (DSP), model TMS320F28379D, with a microcomputer equipped with plug-in boards and sensors. The converters use power switches model SKM50GB123D with drivers SKHI-23. The loads resistance and inductance were 50  $\Omega$  and 7 mH. The experimental waveforms for the proposed topology are shown in Fig. 12.

Fig. 12(a) shows the grid voltage  $(e_g)$  and current  $(i_g)$ . As can be observed, the current is sinusoidal and in phase with  $e_g$ , ensuring a unity power factor. Fig. 12(b) shows the converter voltage at the grid side  $(v_g)$ , which generates five voltage levels. Fig. 12(c) illustrates the DC-link voltages  $v_{ca}$  and  $v_{cb}$ . The two DC-link voltages are regulated and balanced to their reference values, i.e, both voltages are around 105 V. These voltages present a low-frequency

FIGURE 12. Experimental results. (a) Grid voltage  $(e_g)$  and current  $(i_g)$ . (b) Input voltage  $(v_g)$ . (c) Voltages  $v_{ca}$  and  $v_{cb}$ . (d) Load voltages  $(v_{s1}$  and  $v_{s2}$ ). (e) Average load voltages  $(v_{s1}$  and  $v_{s2})$  and currents  $(i_{s1}$  and  $i_{s2})$ . (f) Rectifiers' pole voltages  $(v_{a10a}, v_{a20a}, v_{b10b}$  and  $v_{b20b}$ ). (g) Transient response of  $v_{ca}$ ,  $v_{cb}$ ,  $e_g$ , and  $i_g$ , for load decreasing. (h) Transient response of  $v_{ca}$ ,  $v_{cb}$ ,  $e_g$ , and  $i_g$ , for load increasing.

component (twice grid frequency), an intrinsic condition of single-phase systems.

The converter output voltages  $(v_{s1}, v_{s2} \text{ and } v_{s3})$  that supply the three-phase open-ended load are shown in Fig. 12(d). These voltages have nine levels. Their average values and load currents  $(i_{s1} \text{ and } i_{s2})$  are shown in Fig. 12(e). Fig. 12(e) shows the rectifiers' pole voltages on the grid-side converters, which alternate between  $-v_{ca}/2$  and  $v_{ca}/2$ . To test the control response to load variations, the resistive part of the load is changed from 37.5  $\Omega$  to 50  $\Omega$  for Fig. 12(f) and the opposite in Fig. 12(g). These results show the dynamical response of the DC-link voltages ( $v_{ca}$  and  $v_{cb}$ ), the grid voltage ( $e_g$ ) and the grid current ( $i_g$ ). It can be observed that the voltages and currents remain stable in both load variations. These results show the proper functioning of the applied controls. Therefore, experimental results are entirely consistent with the simulation results.

#### VIII. CONCLUSIONS

This paper has proposed a new topology for step-down applications, where converters on the grid side are cascaded connected, and the three-phase load is open-ended connected. The system's symmetric operation has been investigated, and the corresponding system model, LSPWM strategy, and control approach have been described. The proposed topology was compared with the conventional one in terms of THD (for grid current), WTHD (for load voltage), and semiconductor losses under two specific scenarios: (i) all topologies operating at the same THD, which implies different carrier frequencies. Regarding the semiconductor losses, in both scenarios, the proposed topology demonstrated better performance, achieving up to 30% lower losses.

The proposed topology provides multilevel voltages at both the grid and load sides, resulting in improved waveform quality compared to the conventional topology. This led to reductions of 46.4% in THD and 57% in WTHD. These enhancements can be leveraged to reduce either the size of passive filters or the switching frequency. A reduction in passive filters means lower manufacturing costs, while a lower switching frequency leads to reduced semiconductor losses and improved energy efficiency. Simulation and experimental results under steady-state and transient-state have shown the effectiveness of the PWM strategy and control algorithm. The proposed topology appears to be a good option for applications where only a single-phase grid is available, such as in rural areas.

# ACKNOWLEDGEMENTS

This study was financed in part by the Paraíba State Research Foundation (FAPESQ), the Coordination of Higher Education Personnel Improvement (CAPES) – Finance Code 001, and the National Council for Scientific and Technological Development (CNPq) 423752/2018-9 process.

# AUTHOR'S CONTRIBUTIONS

A.D.D.ALMEIDA: Formal Analysis, Investigation, Validation, Writing – Original Draft. B.S.GEHRKE: Investigation, Validation, Writing – Review & Editing. N.ROCHA: Conceptualization, Formal Analysis, Supervision. E.L.L.FABRICIO: Conceptualization, Investigation, Supervision. C.A.CALDEIRA: Writing - Review & Editing. G.M.S.RODRIGUES: Writing -Review & Editing. I.S.FREITAS: Writing - Review & Editing.

#### PLAGIARISM POLICY

This article was submitted to the similarity system provided by Crossref and powered by iThenticate - Similarity Check.

#### REFERENCES

- [1] A. K. Adapa, V. John, "Active-Phase Converter for Operation of Three-Phase Induction Motors on Single-Phase Grid", IEEE Transactions on Industry Applications, vol. 53, no. 6, pp. 5668-5675, Nov 2017, doi:10.1109/TIA.2017.2737398.

- [2] V. Verma, A. Kumar, "Cascaded Multilevel Active Rectifier Fed Three-Phase Smart Pump Load on Single-Phase Rural Feeder", IEEE Transactions on Power Electronics, vol. 32, no. 7, pp. 5398-5410, July 2017, doi:10.1109/TPEL.2016.2605005.

- [3] N. B. de Freitas, C. B. Jacobina, A. C. N. Maia, A. C. Oliveira, "Six-Leg Single-Phase to Three-Phase Converter", IEEE Transactions on Industry Applications, vol. 53, no. 6, pp. 5527-5538, Nov 2017, doi:10.1109/TIA.2017.2720138.

- [4] R. d. C. Ferreira, S. M. A. Dias, N. Rocha, E. R. Cabral da Silva, V. F. M. B. Melo, "Predictive Control for a Single-Phase to Three-Phase Converter with Two-Parallel Single-Phase Rectifiers", Eletrônica de Potência, vol. 28, no. 4, p. 324-336, Dec. 2023, doi:10.18618/REP.2023.4.0024.

- [5] R. Q. Machado, S. Buso, J. A. Pomilio, "A Line-Interactive Single-Phase to Three-Phase Converter System", IEEE Transactions on Power Electronics, vol. 21, no. 6, pp. 1628-1636, Nov 2006, doi:10.1109/TPEL.2006.882963.

- [6] E. C. D. Santos, C. B. Jacobina, N. Rocha, J. A. A. Dias, M. B. R. Correa, "Single-phase to three-phase four-leg converter applied to distributed generation system", IET Power Electronics, vol. 3, no. 6, pp. 892-903, Nov 2010, doi:10.1049/iet-pel.2009.0240.

- [7] E. C. dos Santos, C. B. Jacobina, J. A. A. Dias, N. Rocha, "Single-Phase to Three-Phase Universal Active Power Filter", IEEE Transactions on Power Delivery, vol. 26, no. 3, pp. 1361-1371, July 2011, doi:10.1109/TPWRD.2011.2108321.

- [8] S. A. O. da Silva, F. A. Negrão, "Single-Phase to Three-Phase Unified Power Quality Conditioner Applied in Single-Wire Earth Return Electric Power Distribution Grids", IEEE Transactions on Power Electronics, vol. 33, no. 5, pp. 3950-3960, May 2018, doi:10.1109/TPEL.2017.2723573.

- [9] S. Sau, S. Karmakar, B. G. Fernandes, "Modular Transformer-Based Regenerative-Cascaded Multicell Converter for Drives With Multilevel Voltage Operation at Both Input and Output Sides", IEEE Transactions on Industrial Electronics, vol. 65, no. 7, pp. 5313-5323, July 2018, doi:10.1109/TIE.2017.2774733.

- [10] Y. Suresh, A. K. Panda, "Research on a cascaded multilevel inverter by employing three-phase transformers", IET Power Electronics, vol. 5, no. 5, pp. 561-570, May 2012, doi:10.1049/iet-pel.2011.0150.

- [11] M. R. Banaei, H. Khounjahan, E. Salary, "Single-source cascaded transformers multilevel inverter with reduced number of switches", IET Power Electronics, vol. 5, no. 9, pp. 1748-1753, November 2012, doi:10.1049/iet-pel.2011.0431.

- [12] B. S. Gehrke, C. B. Jacobina, N. B. de Freitas, I. R. F. M. P. da Silva, R. P. R. de Sousa, "Asymmetric Cascaded Transformer Multilevel AC-DC Converter", IEEE Transactions on Industry Applications, vol. 60, no. 2, pp. 3373-3382, 2024, doi:10.1109/TIA.2023.3344416.

- [13] F. V. Amaral, T. M. Parreiras, G. C. Lobato, A. A. P. Machado, I. A. Pires, B. de Jesus Cardoso Filho, "Operation of a Grid-Tied Cascaded Multilevel Converter Based on a Forward Solid-State Transformer Under Unbalanced PV Power Generation", IEEE Transactions on Industry Applications, vol. 54, no. 5, pp. 5493-5503, Sep. 2018, doi:10.1109/TIA.2018.2827002.

- [14] J. Shi, W. Gou, H. Yuan, T. Zhao, A. Q. Huang, "Research on voltage and power balance control for cascaded modular solid-state transformer", IEEE Transactions on Power Electronics, vol. 26, no. 4, pp. 1154-1166, April 2011, doi:10.1109/TPEL.2011.2106803.

- [15] M. Najjar, A. Moeini, M. K. Bakhshizadeh, F. Blaabjerg, S. Farhangi, "Optimal Selective Harmonic Mitigation Technique on Variable DC Link Cascaded H-Bridge Converter to Meet Power Quality Standards", IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 4, no. 3, pp. 1107-1116, Sep. 2016, doi:10.1109/JESTPE.2016.2555995.

- [16] E. G. Shivakumar, K. Gopakumar, S. K. Sinha, A. Pittet, V. T. Ranganathan, "Space vector PWM control of dual inverter fed open-end winding induction motor drive", in APEC 2001. Sixteenth Annual IEEE Applied Power Electronics Conference and Exposition (Cat. No.01CH37181), vol. 1, pp. 399-405 vol.1, March 2001, doi:10.1109/APEC.2001.911678.

- [17] X. Zhang, H. Zhang, K. Yan, "Hybrid Vector Model Predictive Control for Open-Winding PMSM Drives", IEEE Transactions on Transportation Electrification, vol. 10, no. 2, pp. 4322-4333, 2024, doi:10.1109/TTE.2023.3308570.

- [18] Y. Jia, N. Xu, L. Chu, Y. Zhang, Z. Xu, Y. Li, Z. Yang, "Control Strategy for an Open-End Winding Induction Motor Drive System for Dual-Power Electric Vehicles", IEEE Access, vol. 8, pp. 8844-8860, 2020, doi:10.1109/ACCESS.2020.2964105.

- [19] N. Bodo, E. Levi, M. Jones, "Investigation of Carrier-Based PWM Techniques for a Five-Phase Open-End Winding Drive Topology", IEEE Transactions on Industrial Electronics, vol. 60, no. 5, pp. 2054-2065, 2013, doi:10.1109/TIE.2012.2196013.

- [20] X. Sun, Z. Liu, D. Jiang, W. Kong, "Multiphase Open-End Winding Induction Machine Drive With the Floating Capacitor", IEEE Transactions on Industry Applications, vol. 56, no. 5, pp. 5013-5022, 2020, doi:10.1109/TIA.2020.3009955.

- [21] B. Venugopal Reddy, V. T. Somasekhar, Y. Kalyan, "Decoupled Space-Vector PWM Strategies for a Four-Level Asymmetrical Open-End Winding Induction Motor Drive With Waveform Symmetries", IEEE Transactions on Industrial Electronics, vol. 58, no. 11, pp. 5130-5141, 2011, doi:10.1109/TIE.2011.2116759.

- [22] R. Baranwal, K. Basu, N. Mohan, "Carrier-Based Implementation of SVPWM for Dual Two-Level VSI and Dual Matrix Converter With Zero Common-Mode Voltage", IEEE Transactions on Power Electronics, vol. 30, no. 3, pp. 1471-1487, 2015, doi:10.1109/TPEL.2014.2316528.

- [23] A. D. D. Almeida, N. Rocha, E. L. L. Fabricio, C. A. Caldeira, G. M. S. Rodrigues, I. S. Freitas, "Single-phase to three-phase ac-dc-ac converter based on cascaded transformers rectifier and open-end winding induction motor", in 2019 IEEE 15th Brazilian Power Electronics Conference and 5th IEEE Southern Power Electronics Conference (COBEP/SPEC), pp. 1-6, 2019, doi:10.1109/COBEP/SPEC44138.2019.9065412.

- [24] P. M. Lingom, J. Song-Manguelle, R. C. C. Flesch, T. Jin, "A Generalized Single-Carrier PWM Scheme for Multilevel Converters". IEEE Transactions on Power Electronics, vol. 36, no. 10, pp. 12112-12126, 2021, doi:10.1109/TPEL.2021.3073748.

- [25] C. B. Jacobina, A. M. Nogueira Lima, E. R. C. da Silva, R. N. C. Alves, P. F. Seixas, "Digital scalar pulse-width modulation: a simple approach to introduce nonsinusoidal modulating waveforms", IEEE Transactions on Power Electronics, vol. 16, no. 3, pp. 351-359, May 2001, doi:10.1109/63.923767.

- [26] C. Jacobina, M. Correa, T. Oliveiro, A. Lima, E. da Silva, "Current control of unbalanced electrical systems", IEEE Transactions on Industrial Electronics, vol. 48, no. 3, pp. 517-525, 2001, doi:10.1109/41.925578.

- [27] C. B. a. Jacobina, E. C. dos Santos, N. Rocha, B. de Sa Gouveia, E. R. C. da Silva, "Reversible AC Drive Systems Based on Parallel AC-AC DC-Link Converters", IEEE Transactions on Industry Applications, vol. 46, no. 4, pp. 1456-1467, July 2010, doi:10.1109/TIA.2010.2049724.

- [28] D. G. Holmes, T. A. Lipo, Harmonic Distortion, IEEE, 2003, doi:10.1109/9780470546284.ch2, URL: https://ieeexplore.ieee.org/ document/5311959.

- [29] "Littelfuse, Inc", "Power Module", 2015, URL: https://bitlybr.com/ Hq4aqOA, "Revised:05/19/15".

- L. H. S. C. Barreto, G. A. L. Henn, P. P. Praça, R. N. A. L. Silva, D. S. [30] Oliveira, E. R. C. da Silva, "Carrier-based PWM modulation for THD and losses reduction on multilevel inverters", in 2012 Twenty-Seventh Annual IEEE Applied Power Electronics Conference and Exposition (APEC), pp. 2436-2441, 2012, doi:10.1109/APEC.2012.6166163.

#### BIOGRAPHIES

Antonio D. D. Almeida received his bachelor's degree in Electrical Engineering from the Federal Institute of Education, Science and Technology of Paraíba in 2018, and completed his master's degree in the same field at the Federal University of Paraíba in 2020. He is currently working toward his Ph.D. degree at the Federal University of Pernambuco. Since 2024, he has been working as a professor of Basic, Technical, and Technological Education in the field of Electrical Engineering at the Federal Institute of Education, Science and Technology of Bahia. His research interests include power electronic converters for application in energy storage for electric vehicles.

**Bruna Seibel Gehrke** was born in Ijuí, Rio Grande do Sul, Brazil, in 1992. She received the B.S. degree in electrical engineering from the Regional University of Northeast of Rio Grande do Sul (UNIJUÍ), in 2016, and the M.S. and D.Sc. degrees in electrical engineering from the Federal University of Campina Grande, in 2019 and 2023, respectively. She is currently a Postdoctoral Researcher at the Federal University of Paraíba. Her research interests include multilevel converters, electrical drives, and modulation techniques.

**Nady Rocha** was born in São Gabriel, Bahia, Brazil, in 1982. He received the B.S., M.S., and Ph.D. degrees in electrical engineering from the Federal University of Campina Grande, Campina Grande, Brazil, in 2006, 2008, and 2010, respectively. Since 2011, he has been with the Department of Electrical Engineering, Federal University of Paraíba, João Pessoa, where he is currently an Associate Professor of Electrical Engineering. His research interests include power electronics, renewable energy sources and electrical drives.

**Edgard Luiz Lopes Fabricio** was born in João Pessoa, Paraíba, Brazil, in 1986. He received the B.S., M.S., and Ph.D. degrees in electrical engineering from the Federal University of Campina Grande, Campina Grande, Brazil, in 2010, 2011, and 2015, respectively. Since March 2012, he has been with the Academic Unity of Control and Industrial Processes, Federal Institute of Paraíba, João Pessoa, Brazil, where he is currently a Professor of electrical engineering. His research interests include power electronics, energy systems, active power filter, and electrical drives.

**Carolina A. Caldeira** received her bachelor's degree in Electrical Engineering from the Federal Institute of Education, Science and Technology of Paraíba in 2018, and completed her master's degree in the same field at the Federal University of Paraíba in 2020. She is currently working toward the Ph.D. in Electrical Engineering at the Federal University of Pernambuco. Since 2025, she has been working as a professor of Basic, Technical, and Technological Education in the field of Electrical Engineering at the Federal Institute of Education, Science and Technology of Sergipe. Her research interests include DC-DC and DC-AC converters applied to renewable energy systems.

**Gleice M. S. Rodrigues** was born in Macapá, Amapá, Brazil, in 1992. She received the B.S. degree in electrical engineering from the Federal University of Amapá, Macapá, Brazil and the M.S. degree in electrical engineering from the Federal University of Paraíba, João Pessoa, Brazil, in 2018 and 2021, respectively. She is currently working as an expansion planning engineer for EDP Espírito Santo Energy Distribution SA, Espírito Santo, Brazil. Her research interests include energy distribution systems and renewable energy.

Isaac Soares de Freitas was born in Itaporanga, Brazil, in 1982. He earned his B.S., M.S., and Ph.D. degrees in Electrical Engineering from the Federal University of Campina Grande (UFCG), Campina Grande, Brazil, in 2004, 2005, and 2007, respectively. From 2006 to 2007, he was a Visiting Scholar at the Electric Machines and Power Electronics Laboratory at Texas A&M University, College Station, USA. Between February and May 2008, he served as a professor at the Federal Center for Technological Education of Petrolina, Brazil. Later, from May to December 2008, he worked in the Department of Mechanical Engineering at the Federal University of Paraíba (UFPB), João Pessoa, Brazil. Since December 2008, he has been a faculty member in the Department of Electrical Engineering at the Federal University of Paraíba (UFPB), João Pessoa, Brazil, where he currently holds the position of Full Professor. His research focuses on power electronics and electrical drives. He is a member of the IEEE Power Electronics Society, IEEE Industrial Electronics Society, SBA - Brazilian Society of Automatics, and SOBRAEP - Brazilian Power Electronics Society.