Received March 19, 2025; accepted June 25, 2025; Date of publication July 16, 2025 The review of this paper was arranged by Associate Editor Montiê A. Vitorino and Editor-in-Chief Heverton A. Pereira

# Minimização dos efeitos de elementos parasitas em circuitos de Double Pulse Test para GaN HEMT

Fabiano M. Ribeiro<sup>1</sup>, Rodrigo Heinrich<sup>1</sup>, Yales R. Novaes<sup>1</sup>

<sup>1</sup>Universidade do Estado de Santa Catarina, Joinville – SC, Brasil Núcleo de Processamento de Energia

e-mail: fabianor.doc@gmail.com, rodrigoheinrich1995@gmail.com, novaes@ieee.org

RESUMO O presente trabalho busca apresentar pontos críticos existentes no desenvolvimento de protótipos Double Pulse Test (DPT) para caracterização de interruptores de GaN. O estado da arte é abordado com foco na exposição dos tipos do interruptor de GaN e suas características físicas. É explicado o funcionamento do circuito DPT e a forma como ele é utilizado para os testes do interruptor. O layout da primeira versão do protótipo é desenvolvido e os componentes são selecionados visando minimizar elementos parasitas. A partir dos resultados do primeiro protótipo, um segundo circuito DPT mais compacto é desenvolvido para reduzir indutâncias das trilhas e quantidade de componentes. Essas melhorias impactam no sinal de sobretensão e oscilações do interruptor de GaN sob teste. Uma terceira versão, mais compacta do circuito DPT é desenvolvida em configuração Meia Ponte, substituindo o diodo de roda livre de SiC por um interruptor de GaN, com as mesmas características do dispositivo sob teste, para comparação com os protótipos anteriores. Detalhes experimentais dos três protótipos são apresentados. E evidenciado o impacto nas transições turn-off e turn-on para os níveis de tensão de 200 V e corrente de 10 A, bem como o tempo de transição durante as comutações para as três implementações de circuito DPT, com correntes de 1 a 10 A e tensões de 100 V, 200 V e 275 V. Também é detalhado o modo de condução reversa do protótipo DPT Meia Ponte para 10 A e 100 V.

PALAVRAS-CHAVE Teste de pulso duplo, DPT, banda larga, WBG, efeitos parasitas, transistores de GaN.

### Minimizing the effects of parasitc elements in Double Pulse Test circuits for **GaN HEMT**

**ABSTRACT** The present work aims to highlight critical points in the development of Double Pulse Test (DPT) prototypes for characterizing GaN switches. The state of the art is discussed with a focus on the types of GaN switches and their physical characteristics. The operation of the DPT circuit and its use in testing the switches is explained. The layout of the first prototype version is developed, and components are selected to minimize parasitic elements. Based on the results of the first prototype, a more compact second DPT circuit is developed to reduce pcb stray inductances and the number of components. These improvements impact the overvoltage signal and oscillations of the GaN switch under test. A third, more compact version of the DPT circuit is developed in a Half-Bridge configuration, replacing the SiC freewheeling diode with a GaN switch with the same characteristics as the device under test, for comparison with the previous prototypes. Experimental details of the three prototypes are presented. The impact on turn-off and turn-on transitions for voltage levels of 200 V and current of 10 A is highlighted, as well as the transition time during switching for the three DPT circuit implementations, with currents from 1 to 10 A and voltages of 100 V, 200 V and 275 V. The reverse conduction mode of the Half-Bridge DPT prototype for 10 A and 100 V is also detailed.

**KEYWORDS** Double pulse test, DPT, wide bandgap, WBG, parasitic effects, GaN transistors.

# INTRODUÇÃO

O Transistor de Nitreto de Gálio de Alta Mobilidade de Elétrons (do inglês Gallium Nitride High Electron Mobility Transistor - GaN HEMT) tem sido amplamente estudado e vários dispositivos têm sido criados para estudo e comercialização, buscando-se aprimorar a tecnologia de interruptores baseados no fenômeno de alta mobilidade de elétrons, cujo efeito já foi descrito em 1975 [1]. Atualmente, há vários fabricantes e é crescente o número de modelos disponíveis GaN transistores pesquisas/comercializações, alguns fabricantes Infineon, EPC, GS, TI, Panasonic, Navitas, entre outros. A estrutura do dispositivo de GaN HEMT e as suas propriedades piezoelétricas, permitem o surgimento de uma região com valor muito elevado de condutividade elétrica denominada de two-dimensional electron gas (2DEG) [1], alavancando o crescimento desta tecnologia.

A fabricação e a caracterização estática da heterojunção AlGaN/GaN da estrutura de depleção foi inicialmente

apresentada em [2] e a estrutura de intensificação em [3]. A partir desses, pesquisas foram apresentadas na busca de dispositivos de intensificação, com base em alterações das dimensões e das densidades de dopagens, são elas: redução na espessura do material de AlGaN somente sob a região de gate, denominada de Recessed-Gate [4], tratamento de "plasma fluoreto" para incorporar íons negativos de flúor no material AlGaN [5] e a estrutura gate injection transistor ou transistor de injeção de gate (GIT), que é composta de uma camada dopada do tipo P na região de gate [6] com possibilidade de modulação de corrente de gate [7]. Em [8] são abordados detalhes das estruturas, com auxílio de diagramas de banda de energia. Recursos de simulações computacionais para auxiliar na avaliação do desempenho das estruturas foram apresentadas em [9].

Na estrutura GIT, diferentemente das demais formas citadas para transformar uma estrutura de depleção em intensificação, a condutividade do canal não é afetada e é possível operar em níveis maiores de tensão de threshold para dar início a condução (no estudo em [10] são avaliados os níveis de tensão de threshold de dispositivos e há efeito de redução do nível em função do aumento da temperatura de junção). A estrutura GIT conta ainda com o efeito de segundo pico de transcondutância [7]. Um parâmetro de importância na avaliação de interruptores é a resistência de condução, característica de impacto na avaliação de perdas de condução. O parâmetro se apresenta variável em função da temperatura da junção, conforme o aumento do valor da temperatura da junção há um aumento da resistência Rds(on) [10]. Na caracterização da resistência Rds(on) pode ser verificada a presença de efeito dinâmico [11], denominado de efeito de colapso de corrente que ocorre durante o início da condução do dispositivo [12], onde o valor inicial da resistência é maior e demora certo tempo para atingir o valor estático, dependendo principalmente da tensão de bloqueio, do tempo que o interruptor permanence sem conduzir e da temperature da junção [13], [14] e [15]. A partir da modificação da estrutura GIT, tem-se a estrutura denominada de Hybrid-Drain-embedded Gate Injection Transistor (HD-GIT) com a inserção de uma nova região pGaN, a qual é adicionada entre os terminais de gate e drain [16]. Na estrutura há praticamente inexistência do efeito dinâmico na resistência de condução, conforme a demonstração apresentada em [12].

Os interruptores de GaN HEMT são capazes de conduzir corrente reversamente pelo mesmo canal de condução direta, isso oferece duas vantagens, dispensa o uso de um diodo antiparalelo e aproveita o canal de alta condutância 2DEG. Em [17] pode ser observada uma característica de recuperação reversa muito mais rápida e eficiente do que as existentes em diodos a base de sílicio.

Com a popularização de transistores GaN com diferentes características surge a necessidade de metodologias para análise do desempenho desses componentes para auxiliar na escolha do que mais condiz com a aplicação. Para o caso da investigação das características de comutação é utilizado um circuito que aplica a técnica denominada de teste de pulso duplo (double pulse test - DPT) [18], onde são obtidos os valores de corrente e tensão no interruptor durante as transições de turn-on e turn-off. Conforme a tecnologia do interruptor, o circuito DPT sofre adaptações visando avaliação das características adicionais do componente.

Pode-se verificar, por exemplo, o estudo apresentado em [18] para a caracterização do componente de tecnologia MOSFET de SiC e o estudo apresentado em [19] para caracterização do componente de tecnologia Cascode de GaN.

Por se tratar de um componente com elevada derivada para entrada em bloqueio e condução, elementos parasitas existentes nos componentes adjacentes ou na placa de circuito impresso afetam de forma mais relevante o comportamento do interruptor GaN [20], por isso há necessidade de dimensionar o circuito impresso e seus respectivos componentes com cautela para que as formas de onda obtidas via o DPT representem o mais fielmente possível o componente sob teste.

O desenvolvimento do presente trabalho visa construir um protótipo com a possibilidade de execução de vários testes para conhecimento da tecnologia GaN HEMT, mas mantendo uma simplicidade funcional que possibilita o reaproveitamento em futuros estudos envolvendo a tecnologia. Os testes são selecionados baseados no circuito DPT apresentado em [21] e no circuito auxiliar em [14].

As versões do DPT exploradas são apresentadas na seção II, os protótipos e os resultados experimentais na seção III e as conclusões obtidas na seção IV.

#### **TESTE DE DUPLO PULSO (DPT)** II.

### Operação do DPT

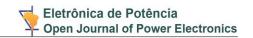

As etapas de operação aqui denominadas de etapas de teste e os principais instantes de tempo de análise, com base no circuito da Figura 1.a estão descritos na Figura 1.b, c. As principais formas de onda estão apresentadas na Figura 1.d.

FIGURA 1. Circuito DPT: (a) intervalo de 0 a t<sub>0</sub>; (b) intervalo t<sub>0</sub> a t<sub>1</sub>; (c) intervalo t<sub>1</sub> a t<sub>2</sub>; (d) formas de onda da operação.

Primeira etapa (0 - t<sub>0</sub>): representa o intervalo de tempo antes do início do teste, com o interruptor bloqueado e o valor de corrente no indutor igual a zero. O circuito deste intervalo está apresentado na Figura 1.a.

Segunda etapa (to - t<sub>1</sub>): o instante t<sub>0</sub> define o início do teste, a partir do qual o dispositivo sob teste (device under test - DUT) é habilitado a conduzir. A partir de uma fonte de tensão CC (C<sub>ENT</sub>), o valor da corrente no indutor L<sub>1</sub> (e no DUT) incrementa linearmente em função do tempo. No momento t<sub>1</sub>, a corrente no indutor atinge o valor da corrente

de teste. De acordo com ajuste do intervalo de tempo entre to e t<sub>1</sub>, escolhe-se o valor da corrente de teste, conforme (1).

$$i_{L_1} = i_{t_0} + \frac{V_{C_{ENT}}}{L_1} (t_1 - t_0)$$

(1)

O circuito em condução deste intervalo está apresentado na Figura 1.b.

Transição turn-off  $(t_1)$ : o instante de tempo  $t_1$  representa o primeiro ponto de teste ou aquisição de dados, refere-se à transição turn-off.

Terceira etapa (t1 a t2): o DUT é desabilitado no instante de tempo t<sub>1</sub>, desta forma, o diodo D<sub>1</sub> assume a condução da corrente do indutor e o valor de corrente no DUT se torna zero. O valor da tensão no DUT se torna aproximadamente de C<sub>ENT</sub>. O valor da corrente em L<sub>1</sub> se mantém praticamente constante durante todo o intervalo (visto que é ajustado para um intervalo de tempo bastante curto, 4 µs), sendo mantido igual para todos os testes realizados. O circuito em condução deste intervalo está apresentado na Figura 1.c.

Transição turn-on (t2): o instante de tempo t2 representa o segundo ponto de teste, refere-se à transição turn-on.

Quarta etapa (t<sub>2</sub> a t<sub>3</sub>): o instante t<sub>2</sub> define o reinício da condução através do DUT, portanto o intervalo é similar ao intervalo t<sub>0</sub> a t<sub>1</sub>, a diferença é que a corrente em L<sub>1</sub> não está em zero no momento t2, mas já se encontra com o valor da corrente de teste. O valor da corrente em L<sub>1</sub> incrementa linearmente em função do tempo, sendo que o intervalo é mantido igual para todos os testes realizados. O circuito em condução deste intervalo está apresentado na Figura 1.b.

Quinta etapa (após t<sub>3</sub>): o instante t<sub>3</sub> define o fim do teste, o DUT é desabilitado, desta forma D1 reinicia a condução, sendo o intervalo similar ao intervalo t<sub>1</sub> a t<sub>2</sub>. D<sub>1</sub> assume a condução da corrente de L1 e o valor da corrente no DUT se torna zero. O valor da tensão no DUT se torna aproximadamente o valor da tensão do C<sub>ENT</sub>. O valor da corrente em L<sub>1</sub> se mantém praticamente constante e é necessário um longo tempo de desmagnetização para ela se tornar nula, o que ocorre com o auxílio das não idealidades existentes nos componentes. O circuito em condução desse intervalo está apresentado na Figura 1.c.

#### В. DPT versão 1 (DPT-1)

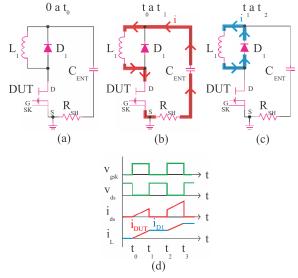

O estágio de potência do protótipo de DPT-1 é composto pelos componentes: DUT, indutor L<sub>1</sub>, diodo D<sub>1</sub>, capacitor CENT e sensor de corrente resistivo RSH, conforme apresentado na Figura 2.

FIGURA 2. Principais componentes do circuito de potência empregados no DPT-1.

O modelo de interruptor de GaN HEMT utilizado no presente trabalho é denominado de IGOT60R070 fabricado pela empresa Infineon. O modelo é uma estrutura de intensificação destinado para as aplicações com valores máximos de operação de tensão de bloqueio de 600 V e corrente de pulso de 60 A.

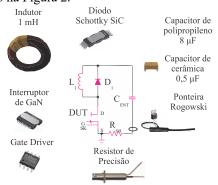

O sensor de corrente empregado foi o SDN-414-10 da empresa T&M Research, com resistência de 0,1  $\Omega$ . O resistor foi submetido a teste no equipamento de análise de impedância na faixa de 40 Hz a 110 MHz. Uma visão geral da impedância do sensor de corrente resultante do teste está apresentada na Figura 3. O resultado apresenta a impedância de aproximadamente 0,1  $\Omega$  para a faixa de frequência abaixo de 1 MHz, o que representa uma faixa com característica resistiva. Para as frequências superiores a 1 MHz foi detectado um aumento do valor de impedância de acordo com o aumento da frequência, verificando-se uma faixa com uma parcela de característica indutiva no componente. A indutância do componente obtida no teste, por exemplo em 1 MHz, foi de 32 nH e a resistência foi de 77 m $\Omega$ .

FIGURA 3. Curva de impedância em função da frequência do sensor de corrente obtida experimentalmente.

Para a avaliação dos componentes parasitas do layout foram utilizados recursos do programa computacional Q3D Extractor da Ansys. O layout da placa foi resumido para realizar a análise, permitindo a obtenção de um modelo mais simplificado, com objetivo de facilitar a convergência no programa computacional. As trilhas da malha de potência foram mantidas e foram excluídas as trilhas de sinal conectadas diferentes potenciais elétricos. componentes inseridos sobre a placa também foram excluídos. Detalhes como as vias e os furos metalizados provendo a conexão entre os dois lados da placa foram mantidos. Ajustes dos materiais como as propriedades eletromagnéticas do cobre que compõem as trilhas são obtidos diretamente com os fabricantes dos materiais.

É realizada a atribuição da excitação (source e sink) definindo-se as superfícies que receberiam a excitação, por exemplo, a entrada do sinal em um primeiro ponto de uma trilha definido como ponto inicial e a saída do sinal em um segundo ponto de uma trilha definido como o ponto final (referenciado como Boundaries and Excitations). Os ajustes da resolução foram mantidos no modo automático (referenciado como Mesh Operations), com o método da configuração de análise (referenciado como Analisys Setup) conforme ajustado a solução desejada *Resistance/inductance,* Capacitance/conductance Resistance/inductance). Algumas análises foram realizadas com auxílio da ferramenta de variação de passo, como a variação da frequência (referenciado como sweep analysis).

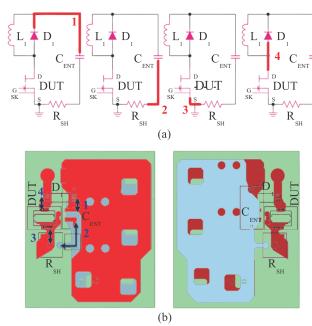

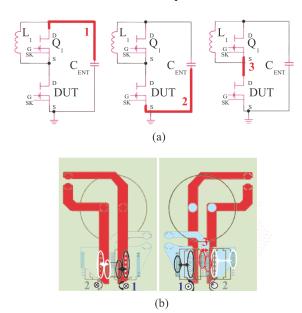

O resultado da avaliação empregando o programa computacional está apresentado na forma de valores de resistência e indutância. Os valores foram obtidos entre os pontos de conexão, de 1 a 4 no layout da placa, conforme apresentado na Figura 4. Também foi possível obter o valor total da malha de potência. As verificações ocorreram para as operações com as frequências de 100 kHz e 100 MHz.

FIGURA 4. Trechos do circuito de potência avaliados no DPT-1 na forma de: (a) circuito eletrônico; (b) layout da placa.

Com análise em 100 kHz, no trecho denominado de 1 que interliga os pontos positivo do capacitor C<sub>ENT(+)</sub> e catodo do diodo  $D_{1(K)}$ , tem-se o valor de indutância de 1,5 nH. No trecho 2 que interliga os pontos negativo do capacitor C<sub>ENT(-)</sub> e resistor R<sub>SH(+)</sub>, tem-se o valor de indutância de 10,8 nH. Na situação exposta, o valor de indutância do trecho 2 é 7,2 vezes maior que do trecho 1. A diferença está relacionada com a maior distância e a forma de interligação que possui uma via adicional no trecho 2. Para o trecho 3 que interliga os pontos negativo do resistor R<sub>SH(-)</sub> e source do DUT<sub>(S)</sub> foi obtido o valor de indutância de 3,2 nH. Já para o trecho 4 que interliga o anodo do diodo D<sub>1(A)</sub> e o drain do DUT<sub>(D)</sub> foi obtido o valor de indutância de 2,3 nH. A partir dos valores obtidos dos trechos de 1 a 4, ou seja, 1,5 nH, 10,8 nH, 3,2 nH e 2,3 nH, obteve-se o valor total da indutância da malha de potência, sendo da situação citada de 17,8 nH.

#### C. DPT versão 2 (DPT-2)

Ao se comparar o DPT-1 com o DPT-2, algumas simplificações foram implementadas para o DPT-2, como a remoção do sensor de corrente resistivo Rsh, a remoção de pontos de medição para a ponteira Rogowski (para os resultados a serem apresentados, a corrente é mensurada através do indutor, para a situação de avaliação de energias pode ser adicionado pontos envoltos no DUT mantendo o mesmo *layout*), a redução da quantidade de capacitores eletrolíticos de alumínio e a remoção dos capacitores de filme de polipropileno. As simplificações realizadas possibilitaram um projeto de layout otimizado, com redução comprimento de trilhas e melhor posicionamento de

componentes, portanto uma redução nos componentes parasitas do layout da placa. O resistor shunt é extraído da placa devido a sua faixa de indutância parasita em frequências superiores a 1 MHz. O circuito da malha de potência do DPT-2 está apresentado na Figura 5.a.

Com a definição do circuito e a listagem dos principais componentes da malha de potência do DPT-2, elaborou-se o layout da placa. A malha de potência foi elaborada com o caminho de retorno da corrente principal (corrente de source Is) no lado oposto da placa (plano oposto), diferentemente do DPT-1 que devido aos componentes foi projetado com o caminho de retorno da corrente principal de forma lateral na placa (no mesmo plano), conforme apresentado na Figura 4.b.

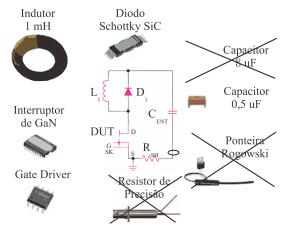

O estágio de potência do protótipo DPT-2 é composto pelos componentes: DUT, indutor L<sub>1</sub>, diodo D<sub>1</sub> e capacitor C<sub>1</sub>, conforme apresentado na Figura 5.

FIGURA 5. Principais componentes do circuito de potência empregados no DPT-2.

A avaliação dos componentes parasitas do DPT-2 é realizada de forma similar ao do DPT-1 para comparação, conforme apresentado na Figura 6. Os valores foram obtidos entre os pontos de conexão de 1 a 3 no layout da placa e o valor total da malha de potência.

FIGURA 6. Trechos do circuito de potência avaliados no DPT-2 na forma de: (a) circuito eletrônico; (b) layout da placa.

Com a análise em 100 kHz, pode-se comparar os trechos do DPT-1 com os do DPT-2. Para o trecho 1 que interliga os pontos positivo do capacitor C<sub>ENT(+)</sub> e catodo do diodo D<sub>1(K)</sub>, o valor de indutância do trecho 1 obtido no DPT-1 foi de 1,5 nH. Já no DPT-2 foi de 0,5 nH, uma redução de 3 vezes. Outros trechos também apresentaram reduções no valor de indutância, como do DPT-1 do acúmulo dos trechos 2 e 3 de 14 nH (10,8 nH + 3,2 nH) para o DPT-2 do trecho 2 de 0,5 nH. E o trecho 4 do DPT-1 de 2,3 nH para o trecho 3 do DPT-2 de 0,6 nH. A soma dos trechos do DPT-1 na verificação foi de 17,8 nH, já no DPT-2 foi de 1,6 nH, o que representa uma redução de 11 vezes na indutância total da malha de potência.

#### D. DPT versão Meia Ponte (DPT-MP)

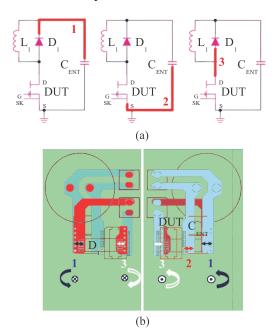

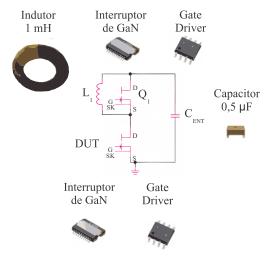

O terceiro protótipo tem como objetivo avaliar a operação envolvendo dois interruptores, de modo a observar comparativos, foi denominado para referência no presente trabalho como DPT-MP. O layout DPT-MP é similar ao DPT-2, sendo a principal diferença, a substituição do diodo de roda livre por um segundo interruptor de GaN, de mesmo modelo que o DUT. O estágio de potência do protótipo de DPT-MP é composto pelos componentes: DUT, interruptor complementar Q<sub>1</sub>, indutor L<sub>1</sub>, capacitores C<sub>ENT</sub>, conforme apresentado na Figura 7.

FIGURA 7. Principais componentes do circuito de potência empregados no DPT-MP.

De forma similar ao realizado para os protótipos DPT-1 e DPT-2, avaliou-se o DPT-MP para obter os componentes parasitas entre os pontos de conexão de 1 a 3 do layout da placa e o valor total da malha de potência. Os trechos da malha de potência do DPT-MP no circuito e no layout da placa estão apresentados na Figura 8.a e na Figura 8.b.

Com a análise em 100 kHz, no trecho denominado de 1 que interliga os pontos positivo do capacitor C<sub>ENT(+)</sub> e drain do DUT<sub>(D)</sub>, obteve-se o valor de indutância de 1,9 nH. No trecho 2 que interliga os pontos negativo do capacitor C<sub>ENT(-)</sub> e source do interruptor Q<sub>2(S)</sub>, obteve-se o valor de indutância de 3,1 nH. Para o trecho 3 que interliga os pontos source do interruptor DUT<sub>(S)</sub> e *drain* do interruptor Q<sub>2(D)</sub> foi obtido 0,1 nH. Na situação exposta, o valor de indutância obtido do trecho 3 foi muito menor do que os demais trechos, a diferença está relacionada com a menor distância e a forma de interligação que possui uma conexão direta no trecho 3. O valor total da indutância da malha de potência do DPT Meia

Ponte pode ser obtido a partir dos valores obtidos dos trechos de 1 a 3, ou seja, 1,9 nH, 3,1 nH e 0,1 nH, sendo o total de 5,1 nH. O valor pode ser comparado com os outros protótipos, sendo no DPT 1 o valor de 17,8 nH e no DPT 2 o valor de 1,6 nH. Uma redução de 3,5 vezes na indutância total da malha de potência quando comparado ao DPT-1 e um aumento de 3,2 vezes quando comparado ao DPT-2, devido à disposição dos componentes no layout acarretar em alterações nas distâncias de conexão entre os componentes.

FIGURA 8. Trechos do circuito de potência avaliados no DPT-MP na forma de: (a) circuito eletrônico; (b) layout da placa.

Os valores obtidos dos componentes parasitas nos trechos do *layout* da placa nos três protótipos com 100 kHz e 1 MHz (onde se percebe uma redução nas indutâncias e um aumento nas resistências parasitas) podem ser observados na Tabela 1.

TABELA 1. Valores Obtidos de Indutância e Resistência em 100 kHz e 1 MHz

| DPT                                       | DPT-1          |     |       | DPT-2 |           | DPT-MP         |                |                |

|-------------------------------------------|----------------|-----|-------|-------|-----------|----------------|----------------|----------------|

|                                           | $L^1$          |     | $L^2$ |       | $L^1$     | $L^2$          | $L^1$          | $L^2$          |

| D1                                        | nН             |     | nН    |       | nΗ        | nН             | nΗ             | nΗ             |

| Parcelas                                  | R <sup>1</sup> |     | $R^2$ |       | $R^1$     | R <sup>2</sup> | $\mathbb{R}^1$ | $\mathbb{R}^2$ |

|                                           | $m\Omega$      |     | mΩ    |       | $m\Omega$ | mΩ             | $m\Omega$      | mΩ             |

| $C_{1}(+):D_{(K)}$                        | 1,5            |     | 1,2   |       | 0,5       | 0,4            | 1,9            | 1,7            |

| $C_{1(+)}:Q_{1(D)}$                       | 0,6            |     | 5,2   |       | 0,3       | 2,1            | 0,5            | 4,4            |

| C <sub>1 (-)</sub><br>:DUT <sub>(S)</sub> | 10,8           | 3,2 | 9,8   | 2,9   | 0,5       | 0,4            | 3,1            | 2,8            |

| $C_{1(-)}$<br>:DUT <sub>(S)</sub>         | 2,9            | 1,1 | 24,9  | 8,1   | 0,3       | 1,8            | 0,6            | 6,7            |

| D <sub>(A)</sub> :Q <sub>(D)</sub>        | 2,3            |     | 1,9   |       | 0,6       | 0,5            | 0,1            | 0,1            |

| $Q_{1(S)}$ :<br>$DUT_{(D)}$               | 1,2            |     | 9,1   |       | 0,3       | 2,3            | 0,2            | 0,7            |

| Total L                                   | 17,8           |     | 15,8  |       | 1,6       | 1,3            | 5,1            | 4,6            |

| Total R                                   | 5,8            |     | 47,3  |       | 0,9       | 6,2            | 1,3            | 11,9           |

Nota: (1) 100 kHz; (2) 1 MHz.

#### III. **RESULTADOS EXPERIMENTAIS**

Os resultados experimentais são obtidos com o osciloscópio 4054B-3 e ponteiras de tensão 4 x P6139B. Na avaliação das 4 ponteiras de tensão do modelo P6139B, o tempo de atraso entre elas é menor que 0,1 ns (avaliado com forma de onda quadrada de 10 MHz e 200 V obtida com auxílio do

protótipo). Em todas versões de protótipos DPT, a medição de corrente é realizada com a ponteira Rogowski no indutor para determinar as correntes de teste, turn-on e turn-off.

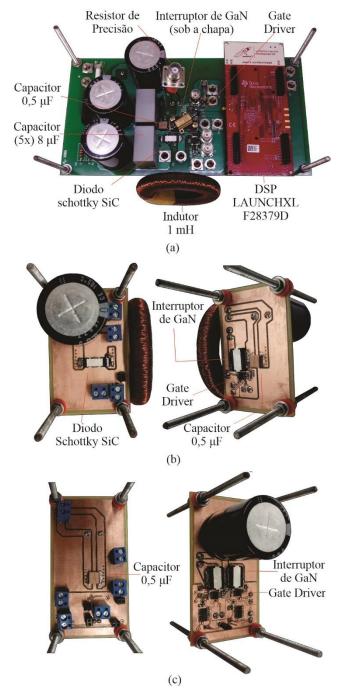

Os protótipos DPT-1, DPT-2 e DPT-MP estão apresentados na Figura 9.

FIGURA 9. Protótipo: (a) DPT-1; (b) DPT-2; (c) DPT-MP.

Os principais equipamentos utilizados no presente trabalho estão apresentados na Tabela 2 e os resultados experimentais estão apresentados na sequência.

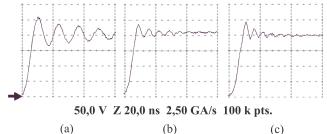

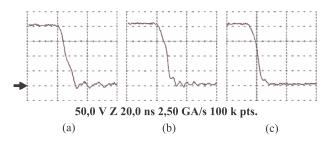

Na avaliação do DPT-1 na Figura 10.a, para a transição da tensão Vds no turn-off com 200 V e 10 A, verificou-se o valor máximo de sobressinal de 256 V. O valor de corrente antes da ocorrência da transição acarreta em acúmulo de energia na indutância parasita presente na malha de potência, sendo essa energia posteriormente transferida à capacitância do interruptor durante a transição turn-off. O mesmo ocorre no DPT-2, sendo constatado com 233 V conforme Figura 10.b.

TABELA 2. Principais equipamentos

| Equipamento               | Informações Gerais                 |  |  |  |  |

|---------------------------|------------------------------------|--|--|--|--|

| Osciloscópio              | 4054B-3 500 MHz 2,5 GS/s           |  |  |  |  |

| 4 x Ponteira de Tensão    | P6139B Tektronix 500 MHz 10X/10    |  |  |  |  |

| 4 x Foiliella de Telisão  | MΩ/8 pF 300 V                      |  |  |  |  |

| 1 x Ponteira de Corrente  | PEM CWT Ultra mini 30 MHz 70 kA/μs |  |  |  |  |

| Fonte de Tensão CC 5-12 V | Politerm POL 16E 0-32 V 0-5 A      |  |  |  |  |

| Fonte de Tensão CC 1000 V | Magna Power Electronics TDS1000-   |  |  |  |  |

| Fonte de Tensão CC 1000 V | 25/380+HS                          |  |  |  |  |

Outro aspecto é a frequência no sinal de tensão Vds na transição turn-off, sendo no DPT-1, a frequência de oscilação constatada de 78 MHz (12,8 ns) e no DPT-2 de 157 MHz (6,38 ns). As alterações de máximo sobressinal e frequência de oscilação que foram verificadas estão diretamente relacionadas com a redução da indutância parasita da malha de potência.

Na Figura 10.c para o DPT Meia Ponte foram verificados os valores de 242 V de sobressinal e 167 MHz (6,0 ns) de frequência de oscilação.

FIGURA 10. Transição do DUT no turn-off com 10 A e 200 V: (a) Formas de onda da tensão Vds no DPT-1; (b) DPT-2; (c) DPT-MP.

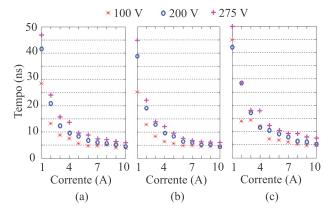

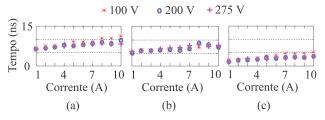

O tempo de subida nas transições *turn-off* que representa o acúmulo de cargas nas capacitâncias parasitas do interruptor também foi analisado. Para valores maiores de corrente Id antecedendo a ocorrência da transição turn-off, mais rapidamente ocorre o acúmulo de cargas e menor é o tempo da transição. Para o teste com valor de corrente de 10 A, no DPT-1 foi verificado 5,30 ns e no DPT-2 de 5,46 ns. O tempo de transição de subida está avaliado de 10 a 90% da tensão sobre o DPT, para os níveis de corrente de 1 a 10 A e tensão de 100, 200 e 275 V, conforme apresentados na Figura 11.

FIGURA 11. Tempo de transição Vds no turn-off em função do nível de corrente ld de 1 a 10 A para tensão Vds de 100, 200 e 275 V: (a) DPT-1; (b) DPT-2; (c) DPT-MP.

Na avaliação do DPT-1, para a transição da tensão Vds no turn-on com 200 V e 10 A, verificou-se a oscilação no sinal de 100 MHz (10 ns) e no DPT-2 de 217 MHz (4,6 ns). A

diferença na oscilação entre as versões também está diretamente relacionada com a redução da indutância parasita presente na malha de potência, o qual interfere na oscilação juntamente com a capacitância parasita do diodo. A alteração no valor representa um aprimoramento do protótipo DPT-1 para o DPT-2. As transições estão apresentadas na Figura 12.

FIGURA 12. Transição do DUT no turn-on com 10 A e 200 V: (a) Formas de onda da tensão Vds no DPT-1; (b) DPT-2; (c) DPT-MP.

O tempo de descida nas transições dos sinais durante o turn-on também foram avaliados, sendo de 90 a 10% da tensão sobre o DPT. Por exemplo, para o teste de corrente de 10 A, no DPT-1 foi verificado o tempo de 8,46 ns e no DPT-2 de 8,97 ns. Resultados avaliados com os níveis de corrente de 1 a 10 A e tensão de 100, 200 e 275 V estão apresentados na Figura 13.

FIGURA 13. Tempo de transição no turn-on em função do nível de corrente Id de 1 a 10 A e tensão Vds de 100, 200 e 275 V, para a: (a) tensão Vds do DPT-1; (b) tensão Vds no DPT-2; (c) tensão Vds no DPT-MP.

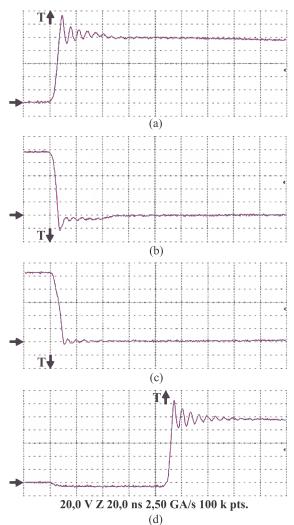

O comportamento do circuito de potência do DPT Meia Ponte expõe o detalhe da condução no modo reverso do interruptor Q<sub>1</sub>. Na Figura 14 estão apresentadas as tensões Vds durante as transições de turn-off e turn-on, nos interruptores DUT e complementar.

O DUT inicia no estado de condução e o interruptor Q<sub>1</sub> no estado de bloqueio. O valor da tensão Vds do DUT é o valor da tensão em condução, aproximadamente zero e o do interruptor Q<sub>1</sub> é aproximadamente 100 V, visto que se encontra no estado de bloqueio. A etapa é mantida até a corrente no indutor L<sub>1</sub> atingir o valor pré-definido para o teste de 10 A através do indutor  $L_1$ .

No instante de tempo em que ocorre o processo de comutação turn-off do DUT, devido ao bloqueio do mesmo, o valor da tensão Vds do DUT é incrementado para 100 V, conforme pode ser verificado na Figura 14.a. Já no interruptor Q<sub>1</sub>, o valor da tensão Vds é decrementado para zero, conforme a Figura 14.b. Como no circuito de acionamento dos interruptores é implementado um intervalo de tempo (tempo morto) entre as ações de comando dos interruptores, ao desabilitar o DUT, há um intervalo de tempo de aproximadamente 60 ns em que o interruptor Q1 não está acionado para condução pelo siste ma de comando, portanto conduz de forma reversa, sem a ação de comando. O valor médio maior que 100 V pode ser observado na tensão Vds do DUT na Figura 14.a durante o intervalo entre as ações de comando. E na tensão Vds do interruptor O<sub>1</sub> na Figura 14.b é notável o valor de tensão de condução reversa de aproximadamente -5,8 V. Na tensão Vds do DUT, verificouse o tempo de subida de 4,24 ns, derivada de 18,92 kV/μs, sobressinal de 133 % e uma oscilação de 158 MHz.

No processo de comutação turn-on, primeiramente o interruptor Q<sub>1</sub> é desabilitado e durante um intervalo de tempo (tempo morto), o interruptor O<sub>1</sub> assume a condução de forma reversa, sem ação de comando e pode ser observado o valor de tensão de condução reversa de aproximadamente -5,8 V na Figura 14.d. Após, o DUT é habilitado e o valor da tensão Vds é decrementado para zero, conforme em Figura 14.c, e no interruptor Q1, o valor da tensão Vds é incrementado para 100 V, conforme na Figura 14.d. Na tensão Vds do DUT verificou-se um tempo de descida de 6,11 ns, derivada de -13,08 kV/µs e uma oscilação de 168 MHz.

FIGURA 14. Forma de onda da tensão Vds no DPT meia Ponte para 10 A e 100 V durante as transições: (a) turn-off do DUT; (b) turn-on do interruptor Q<sub>1</sub>; (c) turn-on do DUT; (d) turn-off do interruptor Q1 com defasagem (90 ns) em relação ao DUT, para destacar a condução reversa.

### IV. CONCLUSÕES

O presente trabalho abordou o projeto e desenvolvimento de um circuito DPT destinado ao estudo e caracterização do interruptor de GaN HEMT. Os principais tipos de

interruptores de GaN HEMT são destacados permitindo uma introdução física da tecnologia. Na sequência, o protótipo DPT-1 é projetado e construído. A partir dos resultados experimentais prévios, verificou-se grandes valores de sobressinal nas comutações e indicativos de possíveis melhorias. Um estudo para aprimoramento de *lavout* de placa é realizado para obtenção do DPT-2. Por fim, o protótipo DPT-MP foi projetado e construído e os efeitos parasitas dos três circuitos foram avaliados experimentalmente.

A malha de potência do DPT-1 foi projetada com o caminho da corrente principal percorrendo por completo no mesmo lado da placa (cancelamento horizontal). Já no DPT-2, a malha de potência foi projetada com o caminho de retorno da corrente principal (corrente Is) percorrendo no lado oposto da placa (cancelamento vertical), sendo possível obter o cancelamento do campo eletromagnético no interior da malha de potência. Algumas melhorias foram implementadas como a remoção de itens que incrementavam componentes parasitas ao longo da malha de potência, como o sensor de corrente resistivo, os locais para medição com a ponteira Rogowski, 3 capacitores eletrolíticos de aluminío de 220 µF e 5 capacitores de filme de polipropileno 8 µF (mantendo-se somente 1 capacitor eletrolítico de alumínio 220 µF, em conjunto com 1 capacitor de cerâmica de 0,5 µF). As adaptações tornaram possível a obtenção de um projeto de layout de placa mais compacto com redução dos comprimentos de trilhas. O sensor de corrente resistivo apesar de ser de alta tecnologia, contribui significativamente para o aumento dos elementos parasitas. Isso demonstra que a medição de corrente de comutação desse tipo de dispositivo não é algo trivial devido a sua velocidade. Conforme análise de impedância em função da frequência, o valor da resistência de aproximadamente 0,1  $\Omega$  para a faixa de frequência abaixo de 1 MHz e uma indutância de 32 nH e resistência de 77 m $\Omega$ para acima de 1 MHz.

A partir dos recursos do programa computacional Q3D extractor foi possível verificar os principais componentes parasitas presentes na malha de potência dos layouts das placas dos protótipos. Em análise específica de 100 kHz foi possível verificar uma indutância total das trilhas da malha de potência de 17,8 nH no DPT-1 e somente 1,6 nH no DPT-2, a diferença representa uma redução de 11 vezes. Com auxílio da ferramenta computacional é possível concluir que a malha de potência deve ser cuidadosamente avaliada para minimizar os impactos dos efeitos parasitas em testes com tecnologias de maior velocidade de comutação. Conclui-se o aprimoramento do protótipo diretamente pela redução da indutância parasita da malha de potência em função da diferença verificada na oscilação do sinal Vds, pois tem dependência direta com a relação entre a indutância parasita ao longo da malha de potência e a capacitância parasita do interruptor. Na situação específica da comutação turn-off com 10 A e 200 V, na medição da tensão Vds, verificou-se o sobressinal de 256 V (128%) no DPT 1 e 233 V (116%) no DPT 2. A frequência de oscilação foi verificada de 78 MHz (12,80 ns) no DPT-1 e 157 MHz (6,38 ns) no DPT-2.

No protótipo do DPT Meia Ponte foi possível verificar o funcionamento do interruptor de forma eficaz na forma de conexão Meia Ponte. No teste com 100 V e 10 A, o sobressinal no DUT foi verificado como 133%, a oscilação de 158 MHz presente após a comutação turn-off, o tempo de subida de 4,24 ns e a derivada de 18,92 kV/μs. E no interruptor Q1 durante o turn-on, verificou-se a oscilação de 168 MHz, o tempo de descida de 6,11 ns e a derivada de -13,08 kV/µs. Também no interruptor Q<sub>1</sub>, verificou-se a atuação da condução reversa, com o valor negativo de tensão Vds de aproximadamente -5,8 V.

Os protótipos foram avaliados para as operações com níveis de tensão de 100, 200 V e 275 e corrente de 1 a 10 A, para verificar as transições turn-off e turn-on para diferentes situações.

Nos diferentes testes efetuados, o interruptor não apresentou qualquer tipo de falha ou anormalidade que pudesse ser observada, atendendo todas as expectativas quanto ao emprego da tecnologia do dispositivo. O desafio para a utilização da tecnologia está relacionado com a obtenção de um layout de placa. Os programas computacionais mostram-se essenciais nesse processo de desenvolvimento.

### **AGRADECIMENTOS**

Este trabalho foi parcialmente apoiado pela Fundação de Amparo à Pesquisa e Inovação do Estado de Santa Catarina (FAPESC), sob o Termo de Outorga FAPESC 2023TR000924; pela CAPES/AUXPE 2910/2023, Processo nº 88881.919326/2023-01- PDPG-CONSOLIDACAO-3-4. PPGEEL/UDESC; pela Nidec Global Appliance/Fapesc, sob o Convênio 2017TR1563 e pelo Conselho Nacional de Desenvolvimento Científico e Tecnológico (CNPq), Brasil, processos 402175/2022-0 e 200163/2022-1.

### **CONTRIBUIÇÕES DOS AUTORES**

F.M.RIBEIRO: Conceitualização, Curadoria de dados, Análise de dados, Recebimento de financiamento, Pesquisa, Metodologia, Administração do projeto, Disponibilização de ferramentas, Desenvolvimento, implementação e teste de software, Supervisão, Validação de dados e experimentos, Design da apresentação de dados, Redação do manuscrito original, Redação - revisão e edição. R.HEINRICH: Redação do manuscrito original, Redação - revisão e edição. Y.R.NOVAES: Conceitualização, Administração do projeto, Disponibilização de ferramentas, Supervisão, Redação revisão e edição.

### PLÁGIO E SIMILARIDADE

O artigo foi submetido para verificação de similaridade no sistema Crossref Similarity Check (iThenticate).

## **DISPONIBILIDADE DE DADOS**

Os dados utilizados nesta pesquisa estão disponíveis no corpo do documento.

# **REFERÊNCIAS**

A. Lidow, J. Strydom, M. Rooij, and D. Reusch, "GaN Transistors for Efficient Power Conversion". 20 ed. California, USA, 2015.

- [2] M. Asif Khan, A. Bhattarai, J. N. Kuznia, and D. T. Olson, "High electron mobility transistor based on a GaN-AlxGa1-xN heterojunction,", Applied Physics Letters, vol. 63, no. 9, pp. 1214-1215, 1993. Doi: 10.1063/1.109775

- [3] M. Asif Khan, Q. Chen, C. J. Sun, J. W. Yang, M. Blasingame, M. S. Shur, and H. Park, "Enhancement and depletion mode GaN/AlGaN heterostructure field effect transistors", Applied Physics Letters, vol. 68, no. 4, pp. 514-516, 1996. Doi: 10.1063/1.116384

- W. Saito, Y. Takada, M. Kuraguchi, K. Tsuda, and I. Omura, "Recessed-gate structure approach toward normally off highvoltage AlGaN/GaN HEMT for power electronics applications", IEEE Transactions on Electron Devices, vol. 53, no. 2, pp. 356-362, 2006. Doi: 10.1109/TED.2005.862708

- Y. Cai, Y. Zhou, K. J. Chen, and K. M. Lau, "High-Performance Enhancement-Mode AlGaN/GaN HEMTs Using Fluoride-Based Plasma Treatment", IEEE Electron Device Letters, vol. 26, no. 7, pp. 435-437, 2005. Doi: 10.1109/LED.2005.851122

- X. Hu, G. Simin, J. Yang, M. Asif Khan, R. Gaska, and M. S. Shur, "Enhancement mode AlGaN/GaN HFET with selectively grown pn junction gate", IEEE Electronics Letters, vol. 36, no. 8, pp. 753-754, 2000. Doi: 10.1049/el:20000557

- Y. Uemoto, M. Hikita, H. Ueno, H. Matsuo, H. Ishida, M. Yanagihara, T. Ueda, T. Tanaka, and D. Ueda, "Gate Injection Transistor (GIT)—A Normally-Off AlGaN/GaN Power Transistor Using Conductivity Modulation", IEEE Transactions on Electron Devices, vol. 54, no. 12, pp. 3393- 3399, 2007. Doi: 10.1109/TED.2007.908601

- [8] L. Efthymiou, G. Longobardi, G. Camuso, T. Chien, M. Chien, and F. Udrea, "On the physical operation and optimization of the p-GaN gate in normally-off GaN HEMT devices", Applied Physics Letters, vol. 110, no. 12, pp. 1-5, 2017. Doi: 10.1063/1.4978690

- M. R. Hontz, R. Chu, R. Khanna, "TCAD modeling of a lateral GaN HEMT using empirical data", IEEE Applied Power Electronics Conference and Exposition, vol. Mar, pp. 244-248, 2018. Doi: 10.1109/APEC.2018.8341017

- [10] H. Li, C. Yao, C. Han, J. A. Brothers, X. Zhang, and J. Wang, "Evaluation of 600 V GaN Based Gate Injection Transistors for High Temperature and High Efficiency Applications", IEEE 3rd Workshop on Wide Bandgap Power Devices and Applications (WiPDA), pp.85-91, 2015. Doi: 10.1109/WiPDA.2015.7369300

- [11] K. Li, P. Evans, and M. Johnson, "Characterisation and Modelling of Gallium Nitride Power Semiconductor Devices Dynamic Onstate Resistance", IEEE Transactions on Power Electronics, vol. 6, 5262-5273, 2018. no. 10.1109/TPEL.2017.2730260

- [12] K. Tanaka, T. Morita, H. Umeda, S. Tamura, H. Ishida, M. Ishida, and T. Ueda, "Mechanism of Current-Collapse-Free Operation in E-Mode GaN Gate Injection Transistors Employed for Efficient Power Conversion", IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), pp.1-4, 2016. 10.1109/CSICS.2016.7751053

- [13] K. Tanaka, H. Umeda, H. Ishida, M. Ishida, and T. Ueda, "Effects of hole traps on the temperature dependence of current collapse in a normally-OFF gate-injection transistor Effects of hole traps on the temperature dependence of current collapse in a normally-OFF gate injection transistor", Japanese Journal of Applied Physics, vol. 054101, no. 55, pp. 1–8, 2016. Doi: 10.7567/JJAP.55.054101

- [14] R. Li, X. Wu, S. Yang, K. Sheng, and K. Sheng, "Dynamic Onstate Resistance Test and Evaluation of GaN Power Devices under Hard and Soft Switching Conditions by Double and Multiple Pulses", IEEE Transactions on Power Electronics, vol. 34, no. 2, pp. 1044-1053, 2019. Doi: 10.1109/TPEL.2018.2844302

- [15] T. Cappello, A. Santarelli, and C. Florian,"Dynamic RON Characterization Technique for the Evaluation of Thermal and Off-State Voltage Stress of GaN Switches", IEEE Transactions on Power Electronics, vol. 33, no. 4, pp. 3386-3398, 2018. Doi: 10.1109/TPEL.2017.2710281

- [16] K. Tanaka, T. Morita, H. Umeda, S. Kaneko, M. Kuroda, A. Ikoshi, H. Yamagiwa, H. Okita, M. Hikita, M. Yanagihara, Y. Uemoto, S. Takahashi, H. Ueno, H. Ishida, M. Ishida, and T. Ueda, "Suppression of current collapse by hole injection from drain in a normally-off GaN-based hybrid-drain-embedded gate injection transistor", Applied Physics Letters, vol. 107, pp. 163502-1-163502-5, 2015. Doi: 10.1063/1.4934184

- T. Morita, M. Yanagihara, H. Ishida, M. Hikita, K. Kaibara, H. Matsuo, Y. Uemoto, T. Ueda, T. Tanaka, and D. Ueda, "650V 3.1 mΩcm<sup>2</sup> GaN-based Monolithic Bidirectional Switch Using Normally-off Gate Injection Transistor", IEEE International Electron Devices Meeting, pp. 865-868, 2007. Doi: 10.1109/IEDM.2007.4419086

- [18] S. S. Ahmad, and G. Narayanan, "Double pulse test based switching characterization of SiC MOSFET. National Power Electronics Conference (NPEC), pp. 319-324, 2017. Doi: 10.1109/NPEC.2017.8310478

- [19] T. Yao, and R. Ayyanar, "A Multifunctional Double Pulse Tester for Cascode GaN Devices" IEEE Transactions on Industrial Electronics, vol. 64, no. 11, pp. 9023-9031, 2017. Doi: 10.1109/TIE.2017.2694381

- [20] E. A. Jones, F. Wang, D. Costinett, "Review of commercial GaN Power Devices and GaN Based converter design challenges". IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 4, no. 3, pp.707-719, 2016. Doi: 10.1109/JESTPE.2016.2582685

- [21] H. Huang, Y. C. Liang, G. S. Samudra, T. Chang, and C. Huang, "Effects of Gate Field Plates on the Surface State Related Current Collapse in AlGaN/GaN HEMTs" IEEE Transactions on Power Electronics, vol. 29, no. 5, pp. 2164-2173, 2014. Doi: 10.1109/TPEL.2013.2288644

# DADOS BIOGRÁFICOS

Fabiano Mendes Ribeiro, nascido em Jaraguá do Sul/SC, em 1992. Recebeu o título de engenheiro eletricista do Centro Universitário Católica de Santa Catarina, Campus Jaraguá do Sul (CATOLICA-SC) em 2015, concluiu o mestrado em Eletrônica de Potência pela Universidade do Estado de Santa Catarina (UDESC) em 2020. Áreas de interesse: processamento de energia elétrica, retificadores com elevado fator de potência, sistemas de geração de energia elétrica e sistema eletrônicos microcontrolados.

Rodrigo Heinrich, nascido em Rio do Sul/SC, em 1995. Possui metrado na área de Sistemas Eletroeletrônicos com foco em Eletrônica de Potência pela Universidade do Estado de Santa Catarina (UDESC-CCT, 2018-2020) e graduação em Engenharia Elétrica nessa mesma instituição (UDESC-CCT, 2013-2017). Atuou como pesquisador no projeto "Controles eletrônicos avançados aplicados a sistemas de refrigeração" com a empresa EMBRACO (UDESC/EMBRACO, 2018/2020). Doutorado em andamento na Universidade do Estado de Santa Catarina (UDESC-CCT, 2021-). É engenheiro eletricista na CELESC Distribuição. Atua principalmente nos seguintes temas: retificadores para correção de fator de potência, elementos magnéticos para conversores estáticos e conversores CC-CC.

Yales Rômulo de Novaes, nascido em Indaial/SC, em 1974. Recebeu o título de engenheiro eletricista da FURB em 1999, concluiu mestrado em Eletrônica de Potência pela Universidade Federal de Santa Catarina (UFSC-INEP) em 2000, atuou como pesquisador em 2001 junto ao INEP-UFSC e concluiu o doutorado em Eletrônica de Potência em 2006 nessa mesma instituição. De 2006 a 2008 realizou Pós-doutorado na EPFL-Universidade Federal de Lausanne - Suíça (LEI). De 2008 a 2010 atuou como pesquisador em sistemas de Eletrônica de Potência na empresa ABB Corporate Research Switzerland. Áreas de interesse: processamento de energia solar fotovoltaica, conversores modulares multiníveis (MMC), retificadores com elevado fator de potência e conversores de elevado ganho. Atualmente é professor titular no departamento de engenharia elétrica da UDESC em que atua desde 2010. Em 2022/23 realizou estágio pós-doutoral no PEM da UoN - Universidade de Nottingham, Inglaterra.