# CONVERSOR CC-CC DE ALTO GANHO OBTIDO PELA COMBINAÇÃO ENTRE REDES DE INDUTOR E DE CAPACITOR CHAVEADOS

Marcos A. Salvador, Thamires P. Horn, Telles B. Lazzarin, Roberto F. Coelho Universidade Federal de Santa Catarina - UFSC, Instituto de Eletrônica de Potência – INEP, Florianópolis – SC, Brasil e-mail: msal.salvador@gmail.com, thamireshorn@gmail.com, telles@inep.ufsc.br, roberto@inep.ufsc.br

Resumo – Este artigo apresenta um conversor CC-CC elevador não isolado, obtido a partir da combinação de uma rede ativa de indutores chaveados com uma rede passiva de capacitores chaveados. O conversor proposto pode alcançar ganhos de tensão elevados (>10) e caracteriza-se por apresentar reduzido número de componentes e baixos esforços de tensão interruptores. O artigo apresenta o princípio de operação do conversor em modo de condução contínua e suas principais formas equacionamento considerando parâmetros parasitas e análise comparativa com outros conversores de similar ganho, previamente publicados na literatura. A validação experimental do conversor proposto é alcançada por meio de um protótipo com potência nominal de 200 W, tensão de entrada de 20 V, tensão de saída de 260 V, frequência de comutação de 50 kHz e rendimento nominal de 94,27%.

Palavras-Chave – Capacitor Chaveado, Conversor CC-CC Elevador de Alto Ganho, Indutor Chaveado.

# HIGH GAIN DC-DC CONVERTER OBTAINED BY COMBINING SWITCHED INDUCTOR AND SWITCHED CAPACITOR CELLS

Abstract – This paper presents a non-isolated dc-dc converter obtained from the combination of a switched inductor active network and a passive switched capacitor cell. The proposed converter can achieve high voltage gains (>10) and is characterized to present reduced number of components and low voltage stresses in the switches. The paper presents the converter operation in continuous and discontinuous conduction modes, its main waveforms, equation considering parasitic elements and a comparative analysis with other converters with similar gain and previously published in the literature. The experimental validation of the proposed converter is carried out by a prototype with nominal power of 200 W, input voltage of 20 V, output voltage of 260 V, switching frequency of 50 kHz and rated efficiency of 94.27%.

*Keywords* — High Step-up DC-DC Converter, Switched Capacitor, Switched Inductor.

Artigo submetido em 21/08/2017. Primeira revisão em 25/09/2017. Aceito para publicação em 14/11/2017 por recomendação do Editor Marcelo Cabral Cavalcanti.

# I. INTRODUÇÃO

Conversores CC-CC elevadores de alto ganho (>10) são utilizados para adaptar baixos níveis de tensão a patamares elevados. Teoricamente, o conversor *Boost* convencional aparece como um candidato adequado para essas aplicações. No entanto, na prática, quando sua razão cíclica de operação se aproxima da unidade, seu ganho de tensão e sua eficiência são drasticamente reduzidos devido ao aumento das perdas por condução [1].

Nesse contexto, considerando o ajuste da relação de espiras dos transformadores, conversores CC-CC isolados podem ser identificados como opções viáveis para elevação do ganho de tensão [2], [3]. Entretanto, nesses conversores, a indutância de dispersão do transformador pode produzir picos de tensão sobre os interruptores, requerendo o uso de grampeadores [4], [5], fato que aumenta o custo e a complexidade e reduz a eficiência do conversor.

Como solução, conversores CC-CC não isolados que utilizem técnicas para promover o ganho de tensão têm sido amplamente abordados em várias aplicações que envolvem fontes de energia renováveis de baixa potência, devido à simplicidade, volume, custo e boa eficiência que apresentam quando comparados com topologias isoladas [2], [3], [6].

Tais conversores são frequentemente classificados com base na presença ou não de elementos magneticamente acoplados – indutores acoplados. Em conversores que fazem uso de indutores acoplados, o elevado ganho de tensão pode ser alcançado pelo ajuste da relação de espiras deste componente. Nesse caso, a indutância de dispersão também pode causar picos de tensão sobre interruptores, assim como nos conversores isolados [7], [8], demandando o emprego de circuitos de grampeamento passivos ou ativos para reduzir esse efeito [8], [9].

Conversores de alto ganho que não empregam indutores acoplados baseiam-se na utilização de conexões em cascata [10]-[12] ou de células multiplicadoras de tensão que, por sua vez, fazem uso de indutores ou de capacitores chaveados [13]-[15]. As células de multiplicação são capazes de ampliar o ganho de tensão dos conversores, porém a eficiência global pode ser degradada em virtude do grande número de componentes, principalmente quando várias células são aplicadas [16].

Diante das possibilidades apresentadas, [17] propôs um conversor simétrico híbrido que emprega uma rede ativa [18] e uma célula passiva [15] de indutores chaveados (Symmetrical Hybrid Switched Inductor Converter – SH-SLC). Durante o intervalo em que os interruptores deste conversor estão conduzindo, a energia é armazenada em

quatro indutores conectados em paralelo (existem seis interruptores no caminho da corrente nesse intervalo). No intervalo complementar, estes indutores descarregam-se em série (existem três interruptores no caminho da corrente durante este intervalo). Apesar de empregar uma quantidade considerável de componentes, sobretudo diodos (sete deles), o conversor provém ganho de tensão elevado e uma eficiência aproximada de 92% na potência nominal.

Utilizando-se da mesma premissa, neste artigo apresentase um novo conversor elevador de alto ganho sem empregar indutor acoplado. Tal conversor combina uma rede passiva de capacitor chaveado (*Passive Switched Capacitor – PSC*), também denominada em [15] como *step-up* 2 *cell* (SU2C), com uma rede ativa de indutor chaveado (*Active Switched Inductor – ASL*) [18], resultando no conversor ASL-SU2C.

Embora ambos os conversores, SH-SLC [17] e ASL-SU2C (proposto neste artigo), apresentem o mesmo ganho estático, o ASL-SU2C possui algumas vantagens: (i) utiliza menor número de interruptores (cinco diodos a menos); (ii) há somente dois interruptores no caminho da corrente durante os dois estados topológicos; (iii) apresenta menores esforços de tensão nos interruptores; (iv) pode alcançar uma melhor eficiência, como será confirmado por resultados experimentais.

Objetivando explorar adequadamente esse novo conversor, o presente artigo está organizado da seguinte forma: inicialmente, a Seção II apresenta a derivação topológica do conversor ASL-SU2C. Posteriormente, na Seção III, são apresentados os princípios de operação em modo de condução contínua (MCC) e descontínua (MCD) de corrente, bem como as características externas, a influência dos parâmetros parasitas no ganho de tensão e o equacionamento relacionado ao conversor proposto. A Seção IV compara o ganho estático, esforços e o número de componentes do ASL-SU2C com outros conversores. A Seção V apresenta alguns resultados experimentais com o intuito de validar a operação do conversor proposto e, por último, as conclusões são obtidas na Seção VI.

#### II. DERIVAÇÃO DA TOPOLOGIA ASL-SU2C

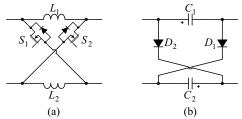

A rede ativa de indutor chaveado (ASL), representada na Figura 1(a), é composta por dois interruptores  $S_1$  e  $S_2$  e dois indutores  $L_1$  e  $L_2$ . Os indutores  $L_1$  e  $L_2$  são carregados em paralelo quando os interruptores estão conduzindo, e descarregados em série quando os interruptores estão bloqueados [18], conforme pode ser observado na Figura 3.

A célula passiva de capacitor chaveado (SU2C), mostrada na Figura 1(b), consiste em dois diodos  $D_1$  e  $D_2$  e dois capacitores  $C_1$  e  $C_2$ . Esses capacitores são carregados em paralelo quando os diodos estão conduzindo e descarregados em série quando os diodos estão bloqueados [15], como pode ser observado na Figura 3.

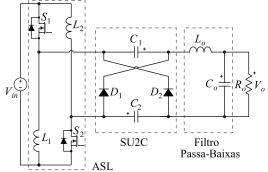

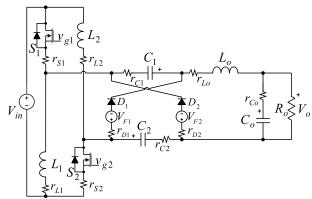

Combinando a rede ASL com a célula SU2C e um filtro *LC* de baixa frequência de saída, o conversor apresentado na Figura 2 é derivado, sendo que os diodos operam de forma complementar aos interruptores.

Fig. 1. (a) Rede ASL [18] e (b) célula SU2C [15].

Fig. 2. Conversor ASL-SU2C proposto.

## III. PRINCÍPIO DE OPERAÇÃO E EQUACIONAMENTO

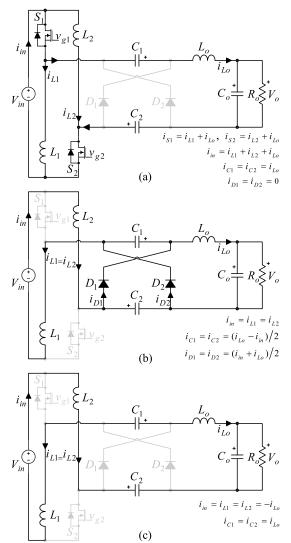

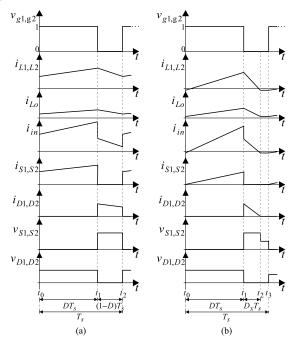

Os estados topológicos relacionados ao conversor ASL-SU2C com componentes ideais são ilustrados na Figura 3, enquanto a Figura 4 apresenta algumas formas de onda típicas obtidas para operação em MCC e MCD.

#### A. Operação em MCC

O ASL-SU2C possui duas etapas de operação em MCC, definidos como etapas 1 e 2, respectivamente descritas pelos circuitos equivalentes apresentados na Figura 3(a) e (b) e pelas formas de onda da Figura 4(a).

• Etapa 1  $(t_0 < t < t_1)$ : na primeira etapa os interruptores  $S_1$  e  $S_2$  são comandados a conduzir simultaneamente. Durante esse intervalo os indutores  $L_1$  e  $L_2$  são carregados em paralelo pela fonte  $V_{in}$  e os capacitores  $C_1$  e  $C_2$  são descarregados em série, enquanto os diodos  $D_1$  e  $D_2$  permanecem bloqueados. A carga é suprida pela fonte e pela energia previamente armazenada nos capacitores  $C_1$  e  $C_2$ . Considerando que idealmente as tensões médias  $V_{C1}$  e  $V_{C2}$  são iguais, a variável  $V_C$  foi adotada para representálas, e assim a tensão aplicada aos indutores é expressa por:

$$V_{L_1} = V_{L_2} = V_{in} \tag{1}$$

$$V_{L_0} = V_{in} + 2V_C - V_o \,. \tag{2}$$

• Etapa 2 ( $t_1 < t < t_2$ ): quando os interruptores  $S_1$  e  $S_2$  são comandados a bloquear, os diodos  $D_1$  e  $D_2$  entram em condução. Assim, os indutores  $L_1$  e  $L_2$  são conectados em série com a fonte de tensão  $V_{in}$  e fornecem energia para carregar os capacitores  $C_1$  e  $C_2$ , conectados em paralelo, e à saída do conversor. Nesta etapa, a tensão aplicada aos indutores pode ser calculada por:

$$V_{L_1} = V_{L_2} = \frac{V_{in} - V_C}{2} \tag{3}$$

$$V_{L_o} = V_C - V_o. (4)$$

Fig. 3. Estados topológicos: (a) interruptores em condução, (b) interruptores bloqueados e (c) interruptores bloqueados em operação MCD.

Fig. 4. Formas de onda típicas para (a) MCC, (b) MCD.

Ao utilizar o princípio de balanço volt-segundo aos indutores, podem-se obter as seguintes expressões usando (1)-(4), sendo a variável *D* correspondente a razão cíclica do conversor:

$$\overline{V_{L_1}} = \overline{V_{L_2}} = V_{in}D + \left(\frac{V_{in} - V_C}{2}\right)(1 - D) = 0$$

(5)

$$\overline{V_{L_o}} = (V_{in} + 2V_C - V_o)D + (V_C - V_o)(1 - D) = 0.$$

(6)

Resolvendo (6), é possível determinar o valor médio da tensão aplicada aos capacitores  $C_1$  e  $C_2$ :

$$V_C = \frac{V_o - V_{in} D}{1 + D}. (7)$$

Substituindo (7) em (5), o ganho de tensão ideal do conversor em MCC é obtido:

$$M_{MCC} = \frac{V_o}{V_{in}} = \frac{1+3D}{1-D}.$$

(8)

#### B. Operação em MCD

O ganho estático ideal na operação em MCD pode ser obtido incluindo-se a terceira etapa de operação na análise, em que todos semicondutores estão bloqueados, conforme retratado na Figura 3(c),

Etapa 1 (t<sub>0</sub> < t < t<sub>1</sub>): essa etapa de operação é ilustrada na Figura 3(a). A tensão aplicada aos indutores é descrita por (1) e (2), enquanto os valores máximos de corrente através destes componentes (I<sub>Lp</sub> e I<sub>Lop</sub>) são expressos por:

$$I_{Lp} = I_{L1p} = I_{L2p} = \frac{V_{in}D}{f_sL} + I_{L(min)}$$

(9)

$$I_{Lop} = \frac{2V_{in}D}{f_S L_o} + I_{Lo(\min)}$$

(10)

onde  $f_S$  representa a frequência de chaveamento do conversor e L representa os indutores de entrada  $L_1$  e  $L_2$ , considerando-os como sendo iguais.

• Etapa 2 ( $t_1 < t < t_2$ ): essa etapa é retratada na Figura 3(b). A tensão aplicada aos indutores é descrita por (3) e (4) e as correntes através deles são expressas por:

$$I_{L(\min)} = I_{L1(\min)} = I_{L2(\min)} = \frac{(V_{in} - V_c)D_x}{2 f_c L} + I_{Lp}$$

(11)

$$I_{Lo(min)} = \frac{(V_c - V_o)D_x}{f_S L_o} + I_{Lop}$$

(12)

onde  $D_x$  corresponde à razão cíclica do intervalo em que as correntes dos indutores decrescem até zero.

• Etapa 3 (t<sub>2</sub> < t < t<sub>3</sub>): durante esse intervalo a corrente através dos diodos torna-se nula, enquanto os interruptores S<sub>1</sub> e S<sub>2</sub> ainda permanecem sem comando, de maneira que todos os semicondutores estejam bloqueados. A corrente que flui através de L<sub>1</sub> e L<sub>2</sub> é constante, como mostrado nas Figuras 3(c) e 4(b). Além disso, a corrente em L<sub>o</sub> é descrita por:

$$I_{Lo(\min)} = -I_{L(\min)}. \tag{13}$$

Combinando (9) e (11), é possível encontrar o intervalo de tempo decorrente entre  $t_1$  e  $t_2$ , associado à razão cíclica  $D_x$ , conforme ilustrado na Figura 4(b), dado por:

$$D_{x} = \frac{2V_{in}D}{V_{C} - V_{in}}. (14)$$

Associando (10), (12) e (14), a tensão  $V_C$  também pode ser obtida:

$$V_C = \frac{1}{2} (V_{in} + V_o). {15}$$

Substituindo-se (15) em (14),  $D_x$  pode ser reescrita em função dos parâmetros D,  $V_o$  e  $V_{in}$ :

$$D_{x} = \frac{4V_{in}D}{V_{o} - V_{in}}.$$

(16)

Durante a terceira etapa de operação, o valor médio da corrente através dos diodos  $D_1$  e  $D_2$  é igual ao valor médio da corrente de saída  $I_o$ , então:

$$I_o = I_{Dp} \frac{D_x}{2} = \frac{V_o}{R}$$

(17)

$$I_{Dp} = I_{D1p} = I_{D2p} = \frac{I_{Lp} + I_{Lop}}{2}.$$

(18)

Combinando-se (9), (10), (17) e (18), encontra-se:

$$I_o = \frac{V_o}{R_o} = \frac{2V_{in}^2 D^2}{f_S L_{eq}(V_o - V_{in})}$$

(19)

onde a indutância equivalente  $L_{eq}$  é definida por:

$$L_{eq} = \frac{1}{\frac{1}{2L} + \frac{1}{L_o}}. (20)$$

Resolvendo-se (19), o ganho de tensão ideal em MCD é obtido:

$$M_{MCD} = \frac{V_o}{V_{in}} = \frac{1}{2} + \frac{1}{2} \sqrt{1 + \frac{8D^2}{K}}$$

(21)

em que, similarmente a [1] e [19], o parâmetro adimensional K é definido por:

$$K = \frac{f_S L_{eq}}{R_o}. (22)$$

#### C. Característica Estática

O conversor proposto pode operar no modo de condução crítica (MCCr), onde os ganhos estáticos em MCC e MCD são equivalentes. Consequentemente, igualando-se (8) e (21), o valor crítico de *K* pode ser obtido:

$$K_{\text{crit}} = \frac{D(1-D)^2}{2(1+3D)} \,. \tag{23}$$

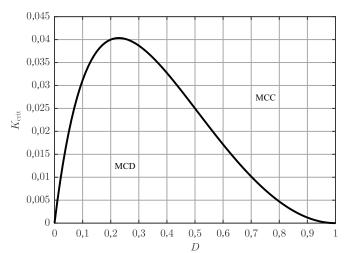

O gráfico de  $K_{\rm crit}$  versus D ilustrado na Figura 5 evidencia que, para  $K > K_{\rm crit}$ , o conversor opera em MCC, caso contrário, em MCD. Adicionalmente, a partir de (19) é possível obter a resistência de carga crítica, dada por:

$$R_{\text{crit}} = \frac{2(1+3D)f_S L_{eq}}{D(1-D)^2}.$$

(24)

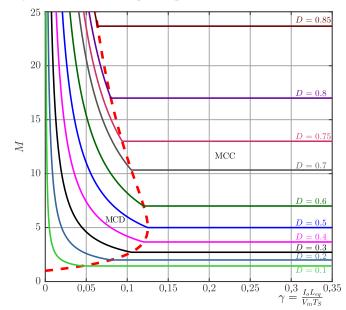

Também se pode definir um parâmetro adimensional  $\gamma$  para representar a corrente parametrizada de saída do conversor [19], dado por:

Fig. 5. Condições limites para a operação do conversor.

Fig. 6. Característica externa do conversor proposto.

$$\gamma = \frac{I_o L_{eq} f_S}{V}.$$

(25)

Substituindo-se (25) em (19), o valor crítico de  $\gamma$  pode ser encontrado:

$$\gamma_{\text{crit}} = \frac{2D^2}{M - 1}.\tag{26}$$

Ademais, isolando-se a razão cíclica D em (8) e substituindo-se o resultado em (26), o valor crítico de  $\gamma$  pode ser expresso em termos do ganho estático, tal como:

$$\gamma_{\text{crit}} = \frac{2(M-1)}{(M+3)^2}.$$

(27)

O valor crítico de  $\gamma$  é graficamente retratado na Figura 6, em que a linha tracejada mostra o limite da operação MCC e MCD.

## D. Influência de Parâmetros Parasitas

Com o intuito de verificar o impacto dos parâmetros parasitas no ganho do conversor, alguns desses parâmetros foram incluídos no modelo analisado. Nessa análise, é considerada a resistência dos enrolamentos do indutor ( $r_{Lo}$  e

$r_{L1}=r_{L2}=r_L$ ), a resistência de condução dos interruptores  $(r_{S1}=r_{S2}=r_S)$ , a queda de tensão direta dos diodos  $(V_{F1}=V_{F2}=V_F)$ , suas respectivas resistências  $(r_{D1}=r_{D2}=r_D)$  e as resistências série equivalentes dos capacitores  $(r_{C1}=r_{C2}=r_C)$ . Os valores numéricos assumidos/medidos para essas grandezas são apresentados na Tabela I, enquanto a estrutura do conversor, incluindo os parâmetros parasitas é apresentada na Figura 7.

Após a inclusão dos parâmetros parasitas, uma nova equação para descrever o ganho estático do conversor pode ser obtida, de acordo com:

$$M'_{CCM} = \frac{\frac{1+3D}{1-D} - \frac{2V_F}{V_{in}}}{1 + \frac{r_L}{R_o} \frac{2(1+D)^2}{(1-D)^2} + \frac{r_S}{R_o} \frac{8D}{(1-D)^2} + \frac{r_D + r_C D}{R_o} \frac{2}{(1-D)} + \frac{r_{Lo}}{R_o}}.(28)$$

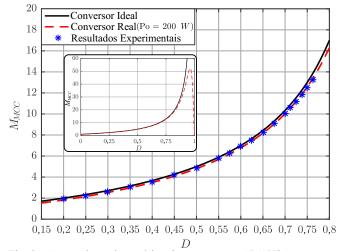

A comparação gráfica entre (8), (28) e alguns pontos experimentais obtidos a partir do ensaio do protótipo descrito na Seção V pode ser feita por meio da Figura 8. Nota-se que resultados experimentais são adequadamente representados pelos modelos, principalmente quando os parâmetros parasitas do conversor são considerados. Pode-se ainda verificar que o ganho estático se aproxima de 16 para razões cíclicas próximas de 0,8, evidenciando a característica de elevação do conversor proposto. Além disso, a imagem detalhada dentro da Figura 8 mostra as curvas de ganho estático para uma completa excursão da razão cíclica, evidenciando a relação entre o comportamento ideal e as limitações reais do conversor.

#### E. Esforços de Tensão e de Corrente

Considerando-se a operação do conversor em MCC, uma análise completa pode ser realizada para obter as principais equações que descrevem os esforços de tensão e de corrente em todos os componentes.

Substituindo-se (15) em (2), encontra-se a tensão aplicada ao indutor durante a primeira etapa de operação, expressa por:

$$v_{Lo} = 2V_{in} = L_o \frac{di_{Lo}}{dt}.$$

(29)

Manipulando-se tal relação, facilmente isola-se  $\Delta I_{Lo}$  ou  $L_o$ , tal como:

$$\Delta I_{Lo} = \frac{2V_{in}D}{f_S L_o} \tag{30}$$

$$L_o = \frac{2V_{in}D}{\Delta I_{Lo}f_S}. (31)$$

Uma vez que o valor médio da corrente no capacitor de saída  $C_o$  é nulo em regime permanente, o valor médio de corrente no indutor de saída  $I_{Lo}$  pode ser considerado igual ao valor médio da corrente de carga  $I_o$ . Portanto, considerando  $P_o = P_{in}$ , pode-se escrever:

$$I_{Lo} = I_o = \frac{1 - D}{1 + 3D} I_{in} \tag{32}$$

$$I_{Lo} = \frac{P_o(1-D)}{V_{in}(1+3D)}. (33)$$

TABELA I Parâmetros Parasitas dos Componentes

| $V_F$ | $r_D$ | $r_L$ | $r_S$ | $r_C$ | $r_{Lo}$ |

|-------|-------|-------|-------|-------|----------|

| 1,7 V | 83 mΩ | 46 mΩ | 15 mΩ | 10 mΩ | 412 mΩ   |

Fig. 7. Conversor ASL-SU2C proposto com parâmetros parasitas.

Fig. 8. Curvas de ganho estático do conversor ASL-SU2C.

Como os indutores de entrada são conectados em paralelo com a fonte  $V_{in}$  durante a primeira etapa de operação, a expressão para determinar as indutâncias de  $L_1$  e  $L_2$  pode ser obtida de maneira similar à descrita para obtenção de  $L_o$ :

$$L = L_1 = L_2 = \frac{V_{in}D}{\Delta I_L f_S}.$$

(34)

A partir da Figura 3(a) e (b) é possível definir uma equação para calcular a corrente de entrada, tal como:

$$I_{in} = (2I_L + I_{Lo})D + I_L(1 - D).$$

(35)

Deste modo, os valores médios das correntes nos indutores de entrada podem ser obtidos isolando-se  $I_L$  em (35) e substituindo-se (33) no resultado encontrado, obtendo-se:

$$I_L = I_{L1} = I_{L2} = \frac{P_o(1+D)}{V_{in}(1+3D)}.$$

(36)

A determinação das capacitâncias  $C=C_1=C_2$  é realizada partindo-se da premissa de que durante a primeira etapa de operação a corrente que flui por estes elementos é a própria corrente  $i_{Lo}$ , que cresce linearmente, partindo de seu valor mínimo  $(I_{Lo}-\Delta I_{Lo}/2)$  até alcançar seu valor máximo  $(I_{Lo}+\Delta I_{Lo}/2)$ , ou seja,

$$i_{Lo} = I_{Lo} - \frac{\Delta I_{Lo}}{2} + \frac{\Delta I_{Lo}}{DT_c} t.$$

(37)

Assim, aplica-se (37) em (38), para obter (39).

$$\Delta V_C = \frac{1}{C} \int_0^{DT_S} i_{Lo} dt \tag{38}$$

$$C = C_1 = C_2 = \frac{P_o D(1 - D)}{V_{in} f_S (1 + 3D) \Delta V_C}$$

(39)

O valor médio da tensão  $V_C$  aplicada aos capacitores foi apresentada em (7). Contudo, a partir da substituição de (8) em (7) pode ser reescrita em função da tensão de entrada:

$$V_C = V_{C1} = V_{C2} = \frac{V_{in}(1+D)}{1-D}.$$

(40)

Como evidenciado na Figura 3(a), a corrente nos capacitores  $C_1$  e  $C_2$  é igual à corrente do indutor de saída durante o primeiro estado topológico. No segundo estado topológico cada capacitor assume metade da diferença entre as correntes dos indutores de entrada e de saída. Consequentemente, o valor eficaz relacionado à corrente dos capacitores pode ser expresso como:

$$i_{C,rms} = \sqrt{\frac{1}{T_s}} \left( \int_0^{DT_s} (i_{Lo})^2 dt + \int_{DT_s}^{T_s} \left( \frac{i_{Lo} - i_L}{2} \right)^2 dt \right)$$

(41)

$$i_{C,rms} = \frac{P_o(1-D)}{V_{in}(1+3D)} \sqrt{\frac{D}{1-D}}.$$

(42)

O valor médio da tensão  $V_{Co}$  aplicada ao capacitor de saída equivale à própria tensão de saída do conversor. Considerando-se que a parcela alternada de  $i_{Lo}$  flui através de  $C_o$ , pode-se escrever:

$$C_o = \frac{V_{in}D}{4L_o\Delta V_{Co}f_S^2}. (43)$$

Para selecionar os diodos  $D_1$  e  $D_2$ , o valor máximo da tensão reversa e o valor médio das correntes a que são submetidos podem ser expressos, respectivamente, por:

$$v_D = \frac{2V_{in}}{1 - D} \tag{44}$$

$$I_D = \frac{P_o(1-D)}{V_{in}(1+3D)} \tag{45}$$

sendo que durante a primeira etapa a tensão  $v_D$  é igual a soma de  $V_{in}$  e  $V_C$  e a corrente  $I_D$  pode ser obtida pelo produto da razão cíclica complementar com a média entre as correntes  $I_L$  e  $I_{Lo}$ , conforme sugere a Figura 3(b).

Os esforços de tensão nos interruptores e seus valores eficazes de corrente podem calculados, respectivamente, por:

$$v_S = \frac{V_{in}}{1 - D} \tag{46}$$

$$i_{S,rms} = \frac{2P_o\sqrt{D}}{V_{in}(1+3D)}$$

(47)

onde  $v_S$  é obtido pela diferença das tensões  $V_{in}$  e  $V_L$  durante a

segunda etapa de operação e  $i_{S,rms}$  pode ser determinada considerando-se a corrente que flui pelos interruptores durante a primeira etapa de operação ( $I_L + I_{IO}$ ).

#### IV. ANÁLISE COMPARATIVA

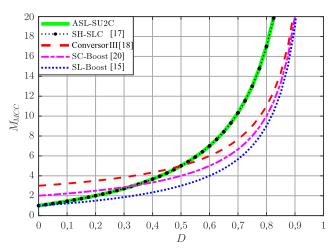

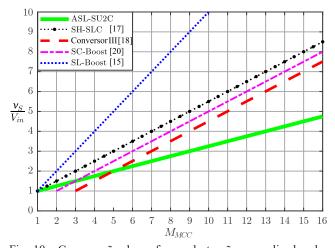

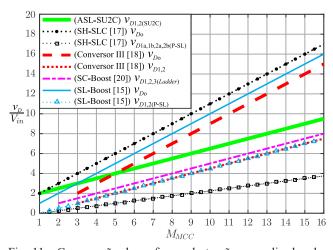

Esta seção compara a topologia proposta com as estruturas não isoladas e não acopladas que também fornecem elevados ganhos de tensão, tal como SL-Boost [15], o SC-Boost [20], o Conversor III de [18] e o SH-SLC [17]. O número de componentes aplicado em cada um dos conversores comparados é apresentado na Tabela II. Ademais, o ganho estático e as equações normalizadas que descrevem os esforços de tensão nos semicondutores para esses conversores estão resumidos na Tabela III e representados graficamente pelas Figuras 9 a 11.

## A. Ganho de Tensão

A partir da Tabela III e da Figura 9 é possível perceber que o maior ganho de tensão ideal é alcançado pelos conversores ASL-SU2C (proposto) e SH-SLC [17]. Todavia, o conversor proposto possui um número significativamente menor de diodos e um indutor a menos. Em contraste, possui apenas dois capacitores adicionais, que podem ser de filme, devido aos baixos valores de capacitância.

TABELA II Comparação entre o Número de Componentes

| Número de     | ASL-<br>SU2C | SH-SLC<br>[17] | Conversor<br>III [18] | SC-<br>Boost<br>[20] | SL-<br>Boost<br>[15] |

|---------------|--------------|----------------|-----------------------|----------------------|----------------------|

| Interruptores | 2            | 2              | 2                     | 1                    | 1                    |

| Diodos        | 2            | 7              | 3                     | 3                    | 4                    |

| Capacitores   | 3            | 1              | 3                     | 3                    | 1                    |

| Indutores     | 3            | 4              | 2                     | 1                    | 2                    |

TABELA III

Comparação do Ganho de Tensão e dos Esforços de

Tensão nos Semicondutores entre o Conversor

Proposto e Topologias sem o Emprego de Indutores

Acoplados

| Tensão                                                                 | ASL-<br>SU2C       | SH-SLC<br>[17]     | Conversor<br>III [18] | SC-<br>Boost<br>[20] | SL-<br>Boost<br>[15] |

|------------------------------------------------------------------------|--------------------|--------------------|-----------------------|----------------------|----------------------|

| Ganho ( $M_{MCC}$ )                                                    | $\frac{1+3D}{1-D}$ | $\frac{1+3D}{1-D}$ | $\frac{3-D}{1-D}$     | $\frac{2}{1-D}$      | $\frac{1+D}{1-D}$    |

| Interruptores $(v_s/V_{in})$                                           | $\frac{M}{1+3D}$   | $\frac{M+1}{2}$    | $\frac{M-1}{2}$       | $\frac{M}{2}$        | M                    |

| Diodos de saída $(v_{Do}/V_{in})$                                      | _                  | M+1                | M-1                   | $\frac{M}{2}$        | M                    |

| Diodos na<br>Célula P-SL<br>$(v_{Da,b}/V_{in})$ e<br>$(v_{Dc}/V_{in})$ | -                  | $\frac{M-1}{4}$    | -                     | -                    | $\frac{M-1}{2}$      |

| Diodos na<br>Célula SC<br>Ladder $(v_D/V_{in})$                        | -                  | -                  | -                     | $\frac{M}{2}$        | -                    |

| Diodos na<br>Célula de<br>elevação de<br>Tensão ( $v_D/V_{in}$ )       | -                  | _                  | $\frac{M-1}{2}$       | -                    | -                    |

| Diodos no SU2C $(v_D/V_{in})$                                          | $\frac{2M}{1+3D}$  | _                  | _                     | _                    | _                    |

#### B. Esforço de Tensão nos Interruptores

As equações apresentadas na Tabela III e as curvas da Figura 10 revelam que o conversor proposto apresenta os menores esforços de tensão nos interruptores, para qualquer ganho de tensão superior a 5.

Fig. 9. Comparação do ganho de tensão.

Fig. 10. Comparação dos esforços de tensão normalizados dos interruptores.

Fig. 11. Comparação dos esforços de tensão normalizados dos diodos.

### C. Esforço de Tensão nos Diodos

Entre os conversores comparados, apenas o conversor proposto não possui diodo de saída. É conveniente relatar que o indutor de saída representa um aumento de custo e de volume, mas também confere característica de fonte de corrente à saída do conversor, o que pode ser vantajoso em algumas aplicações, como, por exemplo, sistemas de recarga de bancos de baterias.

Ao analisar a Tabela III, percebe-se que os diodos de saída podem ser submetidos a níveis expressivos de tensão de bloqueio quando ganhos elevados são requeridos. Além disso, dependendo da célula de ganho aplicada, cada conversor comparado terá diodos adicionais na estrutura. Os esforços de tensão normalizados nos diodos  $(v_D/V_{in})$  para os conversores comparados, são apresentados na Tabela III e graficamente representados na Figura 11. A partir da referida figura, percebe-se que os esforços de tensão nos diodos do conversor proposto são intermediários aos diodos dos demais conversores.

#### V. RESULTADOS EXPERIMENTAIS

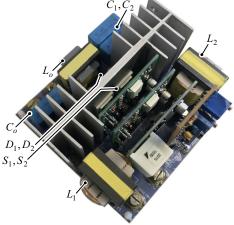

A fim de verificar o desempenho experimental do conversor proposto, o protótipo mostrado na Figura 12 foi construído e testado de acordo com as especificações e componentes apresentados na Tabela IV.

Para alcançar o ganho de tensão desejado (13 vezes), de 20 V para 260 V, foi necessário ajustar a razão cíclica do conversor para D=0.76. As Figuras 12 a 15 apresentam algumas formas de onda experimentais, considerando a

TABELA IV Especificações e Componentes do Conversor Proposto

| Tensão de entrada $(V_{in})$    | 20 V         |

|---------------------------------|--------------|

| Tensão de saída $(V_o)$         | 260 V        |

| Potência nominal $(P_o)$        | 200 W        |

| Frequência de comutação $(f_s)$ | 50 kHz       |

| Drivers comerciais              | DRO100S25A   |

| $S_1$ e $S_2$                   | IRFB4321PbF  |

| $D_1$ e $D_2$                   | SDT10S60     |

| $L_1$ e $L_2$                   | 223 μΗ       |

| $C_1$ , $C_2$ e $C_o$           | 1 μF (filme) |

| $L_o$                           | 2,34 mH      |

Fig. 12. Protótipo de laboratório (100 mm x 100 mm x 50 mm).

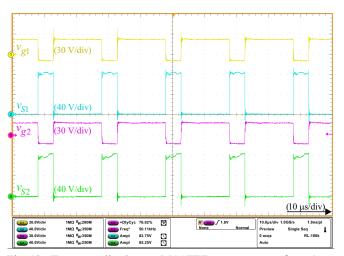

operação do conversor em malha aberta, na potência nominal e com a tensão de entrada fixa em 20 V. A Figura 13 mostra os sinais de comando ( $v_{g1}$  e  $v_{g2}$ ) e destaca o patamar de 80 V de tensão ao qual são submetidos os interruptores ( $v_{S1}$  e  $v_{S2}$ ) durante o bloqueio, conforme previsto por (46).

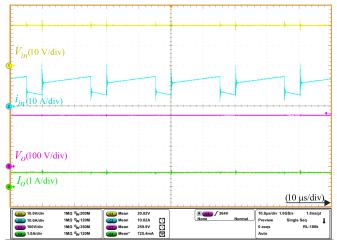

As tensões e correntes de entrada e de saída do conversor são mostradas na Figura 14, evidenciando o elevado ganho de tensão. Pode-se observar que a forma da corrente de entrada indica que o conversor opera em MCC, como na Figura 4(a). A corrente de entrada  $i_{in}$  é igual à soma de  $i_{L1}$ ,  $i_{L2}$  e  $i_{Lo}$  durante o intervalo em que os interruptores estão conduzindo, e igual à corrente dos indutores de entrada, no intervalo complementar, apresentando uma transição que varia entre  $i_L$  e  $2i_L+i_{Lo}$  no instante em que os interruptores entram em condução, e entre  $2i_L+i_{Lo}$  e  $i_L$ , no bloqueio. Em casos em que a fonte de entrada não possa ser submetida a tais variações, é recomendado o emprego de um filtro passabaixas.

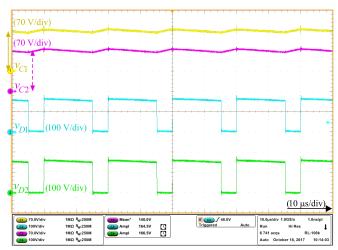

A Figura 15 evidencia que o valor médio da tensão nos capacitores  $C_1$  e  $C_2$  estabelece-se em torno de 140 V, em concordância com (40). Além disso, é observado que as tensões nos diodos foram devidamente previstas por (44).

Fig. 13. Tensões aplicadas aos MOSFETs, entre porta e fonte ( $v_{g1}$  e  $v_{g2}$ ) e entre dreno e fonte ( $v_{SI}$  e  $v_{S2}$ ).

Fig. 14. Tensões de entrada e de saída  $(V_{in} \, {\rm e} \, V_o)$  e correntes de entrada e de saída  $(i_{in} \, {\rm e} \, I_o)$ .

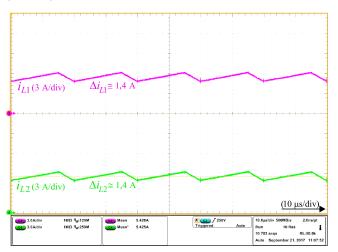

A Figura 16 mostra as formas de onda das correntes nos indutores  $L_1$  e  $L_2$ . O valor médio das correntes mensuradas nos respectivos indutores é de aproximadamente 5,42 A, aproximando-se do valor teórico (5,38 A) estimado por (36). Além disso, como os respectivos indutores foram projetados considerando uma ondulação de corrente ( $\Delta i_L$ ) da ordem de 25% do valor médio nominal, a ondulação experimentalmente obtida (1,4 A) tende ao valor teórico.

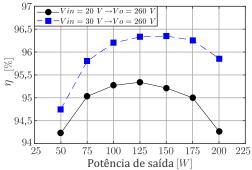

A Figura 17 mostra as curvas de eficiência experimentalmente obtidas a partir do analisador de potência Yokogawa (WT1800). Durante os ensaios, a tensão de saída

Fig. 15. Tensões nos capacitores ( $v_{C1}$  e  $v_{C2}$ ) e tensões nos diodos ( $v_{D1}$  e  $v_{D2}$ ).

Fig. 16. Corrente nos indutores de entrada ( $i_{L1}$  e  $i_{L2}$ ).

Fig. 17. Resultados experimentais: curvas de eficiência em função da potência de saída.

foi mantida em 260 V, enquanto a potência de saída foi variada. A eficiência máxima obtida foi de aproximadamente 96,33%, sendo alcançada com 150 W de potência e 30 V de tensão de entrada. Como pode ser observado na Figura 17 e previamente destacado por [17], a eficiência eleva-se para maiores tensões de entrada, pois a corrente de entrada diminui e, dessa maneira, as perdas por condução nos interruptores e nos indutores tendem a tornarem-se reduzidas.

#### VI. CONCLUSÃO

Este artigo apresentou uma nova topologia de conversor CC-CC não isolado denominado de ASL-SU2C. Resultados experimentais evidenciaram que o conversor proposto pode fornecer um elevado ganho de tensão (13 vezes), utilizandose um número reduzido de semicondutores em uma estrutura simples, que apresenta apenas dois interruptores ou dois diodos no caminho da corrente, dependendo da etapa de operação. Adicionalmente, pelo gráfico da Figura 8 pode-se prever que o conversor é capaz de proporcionar ganhos de até dezesseis vezes, com razão cíclica próxima de 0,8.

Verificou-se, a partir da análise e dos resultados, que as tensões de bloqueio dos interruptores do conversor proposto são reduzidas em comparação às topologias similares, para ganhos de tensão superiores a cinco. Além disso, devido ao uso de uma rede ASL na entrada do conversor, a corrente de entrada é dividida entre os interruptores, assim, as perdas por reduzidas. condução tornam-se ainda mais Como desvantagem, empregam-se dois drivers isolados. evidenciando um custo adicional.

Nas especificações nominais, obteve-se uma eficiência satisfatória de aproximadamente de 94,27%, superior ao desempenho apresentado pelo SH-SLC [17]. Maiores eficiências também podem ser alcançadas quando a tensão de entrada é aumentada para 30 V, como mostrado na Figura 17.

### **AGRADECIMENTOS**

Os autores agradecem a CAPES, ao CNPq e a FINEP pelo apoio financeiro.

## REFERÊNCIAS

- [1] R. W. Erickson, D. Maksimovic, *Fundamentals of Power Electronics*, Kluwer, 2<sup>a</sup> Edição, Norwell, 2001.

- [2] W. Li, X. He, "Review of nonisolated high-step-up dc/dc converters in photovoltaic grid-connected applications," *IEEE Transactions on Industrial Electronics*, vol. 58, no.4, pp. 1239–1250, Abril 2011.

- [3] F. L. Tofoli, D. C. Pereira, W. Josias de Paula, D. S. Oliveira Júnior, "Survey on non-isolated high-voltage step-up dc-dc topologies based on the boost converter," *IET Power Electronics*, vol. 8, no. 10, pp. 2044-2057, Setembro 2015.

- [4] N. P. Papanikolaou, E. C. Tatakis, "Active voltage clamp in flyback converters operating in CCM mode under wide load variation," *IEEE Transactions on Industrial Electronics*, vol. 51, no. 3, pp. 632-640, Junho 2004.

- [5] C. M. Wang, "A novel ZCS-PWM flyback converter with a simple ZCSPWM commutation cell," *IEEE Transactions on Industrial Electronics*, vol. 55, no. 2, pp. 749-757, Fevereiro 2008.

- [6] S.-M. Chen, T.-J. Liang, L.-S. Yang, J.-F. Chen, "A safety enhanced, high step-up DC-DC converter for AC photovoltaic module application," *IEEE Transactions on Power Electronics*, vol. 27, no. 4, pp. 1809–1817, Abril 2012.

- [7] Y. Berkovich, B. Axelrod, "Switched-coupled inductor cell for DC-DC converters with very large conversion ratio," *IET Power Electronics*, vol. 4, no. 3, pp. 309-315, Março 2011.

- [8] Q. Zhao, F. C. Lee, "High-efficiency, high step-up dc-dc converters," *IEEE Transactions on Power Electronics*, vol. 18, no. 1, pp. 65–73, Janeiro 2003.

- [9] T. F. Wu, Y. S. Lai, J. C. Hung, Y. M. Chen, "Boost converter with coupled inductors and buck-boost type of active clamp," *IEEE Transactions on Industrial Electronics*, vol. 55, no. 1, pp. 154–162, Janeiro 2008.

- [10] T.-F. Wu, T.-H. Yu, "Unified approach to developing single-stage power converters," *IEEE Transactions on Aerospace and Electronics Systems*, vol. 34, no. 1, pp. 211–223, Janeiro 1998.

- [11] F. L. Luo, H. Ye, "Positive output cascade boost converters," *IEE Proceedings Electric Power Applications*, vol. 151, no. 5, pp. 590–606, Setembro 2004.

- [12] Y. R. de Novaes, A. Rufer, I. Barbi, "A new quadratic, three level, dc/dc converter suitable for fuel cell applications," *in Proc. of Power Conversion Conference*, pp. 601–607, 2007.

- [13] M. Prudente, L. L. Pfitscher, G. Emmendoerfer, E. F. Romaneli, R. Gules, "Voltage multiplier cells applied to non-isolated dc-dc converters," *IEEE Transactions* on *Power Electronics*, vol. 23, no. 2, pp. 871–887, Março 2008.

- [14] E. H. Ismail, M. A. Al-Saffar, A. J. Sabzali, A. A. Fardoun, "A family of single-switch PWM converter with high step-up conversion ratio," *IEEE Transactions on Circuits and Systems I*, Reg. Papers, vol. 55, no. 4, pp. 1159–1171, Maio 2008.

- [15] B. Axelrod, Y. Berkovich, A. Ioinovici, "Switched-capacitor/switched-inductor structures for getting transformerless hybrid DC–DCPWM converters," *IEEE Transactions on Circuits and Systems I*, Reg. Papers, vol. 55, no. 2, pp. 687–696, Março 2008.

- [16] L. Schmitz, D. C. Martins, R. F. Coelho, "Generalized High Step-Up DC-DC Boost-Based Converter With Gain Cell," *IEEE Transaction on Circuits and Systems I*, Reg. Papers, vol. 64, no. 2, pp. 480-493, Fev. 2017.

- [17] Y. Tang, D. Fu, T. Wang, Z. Xu, "Hybrid Switched-Inductor Converters for High Step-Up Conversion," *IEEE Transactions on Industrial Electronics*, vol. 62, no.3, pp. 1480-1490, Março 2015.

- [18] L. S. Yang, T. J. Liang, J. F. Chen, "Transformerless DC–DC Converters With High Step-Up Voltage Gain," *IEEE Transactions on Industrial Electronics*, vol.56, no.8, pp. 3144-3152, Agosto 2009.

- [19] D. C. Martins, I. Barbi, *Conversores CC-CC Básicos Não Isolados*, 4ª Edição, Florianópolis, 2011.

- [20] J. C. Rosas-Caro, J. M. Ramirez, F. Z. Peng, A. Valderrabano, "A DC-DC multilevel boost converter," IET Power Electronics, vol. 3, no. 1, pp. 129-137, Janeiro 2010.

## DADOS BIOGRÁFICOS

Marcos Antônio Salvador, nascido em junho de 1985 em Blumenau, é Engenheiro Eletricista (2012), e Mestre (2014) pela Fundação Universidade Regional de Blumenau (FURB). Atualmente cursa doutorado na Universidade Federal de Santa Catarina (UFSC) no Instituto de Eletrônica de Potência (INEP). Atuou na indústria eletroeletrônica de 1999 a 2012 e como professor no ensino superior de 2014 a 2016. Suas áreas de interesse incluem modelagem e controle de conversores estáticos, conversores CC-CC de alto ganho, inversores, energias renováveis, armazenamento de energia, processamento digital de sinais. Marcos Antônio Salvador é membro da SOBRAEP.

<u>Thamires Porth Horn</u>, nasceu em São Miguel do Oeste. Atualmente, é graduanda em Engenharia de Controle e Automação na Universidade Federal de Santa Catarina. Suas áreas de interesse incluem estabilidade de microrredes e técnicas de controle aplicadas a conversores estáticos.

Telles Brunelli Lazzarin, nascido em Criciúma, Santa Catarina, Brasil, em 1979. Recebeu o grau de Engenheiro eletricista, mestre e doutor em Engenharia Elétrica pela Universidade Federal de Santa Catarina (UFSC), 2006 e 2010, Florianópolis, Brasil, em 2004, respectivamente. Atualmente é professor adjunto no Departamento de Engenharia Elétrica e Eletrônica da UFSC e pesquisador no Instituto de Eletrônica de Potência (INEP). Suas áreas de interesse incluem processamento de energia renovável (principalmente eólica de pequeno porte), inversores de tensão e conversores estáticos a capacitor chaveado. Prof. Telles é membro da SOBRAEP, PELS, IES

Roberto Francisco Coelho nasceu em Florianópolis, em agosto de 1982. Recebeu o título de Engenheiro Eletricista, Mestre e Doutor em Engenharia Elétrica pela Universidade Federal de Santa Catarina, Florianópolis, SC, Brasil, em 2006, 2008 e 2013, respectivamente. Atualmente é professor do Departamento de Engenharia Elétrica e Eletrônica da mesma instituição, onde desenvolve trabalhos relacionados ao processamento de energia proveniente de fontes renováveis, ao controle e estabilidade de microrredes e a conversores elevadores de alto ganho e de alto rendimento. Prof. Roberto é membro da SOBRAEP e do IEEE.