# RETIFICADOR BOOST BRIDGELESS UNIDIRECIONAL MONOFÁSICO COM CÉLULA DE CAPACITOR CHAVEADO

Julio C. Dias, Telles B. Lazzarin Universidade Federal de Santa Catarina - EEL/INEP, Florianópolis - SC, Brasil e-mail: jcesardias@gmail.com, telles@inep.ufsc.br

Resumo - Este trabalho apresenta a topologia de retificador boost bridgeless híbrido unidirecional monofásico com célula de capacitor chaveado tipo ladder na saída. A estrutura multiplica a tensão de saída e divide os valores de tensão sobre os semicondutores por meio de células de capacitor chaveado. As características da topologia boost convencional integrada à célula de capacitor chaveado proporcionam boa regulação de tensão de saída e de corrente de entrada, desta forma proporciona alto ganho associado com alto fator de potência. Também é apresentada uma estratégia para a modelagem dinâmica de conversores híbridos com capacitor chaveado baseada em um circuito equivalente de ordem reduzida. Um protótipo de 1 kW com tensões de 800 V de saída e 220 V de entrada foi desenvolvido para a validação experimental da estrutura. O conversor apresentou um valor máximo de tensão de 400 V nos semicondutores, pico de rendimento de 97,1 % e fator de potência unitário.

Palavras-chave - Alto Ganho em Tensão, Capacitor Chaveado, Correção de Fator de Potência, Espaço de Estados, Modelagem Dinâmica, Retificador Boost Bridgeless Unidirecional.

## UNIDIRECTIONAL SINGLE-PHASE BRIDGELESS BOOST RECTIFIER WITH SWITCHED CAPACITOR CELL

Abstract – This work presents the hybrid unidirectional single-phase bridgeless boost rectifier topology with a ladder switched-capacitor cell in its output. The structure multiplies the output voltage value through switchedcapacitor cells and divides the voltage stress across the semiconductors. The characteristics of the conventional boost converter integrated to the switched-capacitor technology provide good output voltage and input current regulation, thus it provides high voltage gain associated with high power factor. This work also presents a strategy for the dynamic modeling of hybrid converters that employ the switched-capacitor technology by using an equivalent reduced order circuit. A 1 kW prototype, with an 800 V output and 220 V input voltages was developed for the experimental validation of the structure. The structure presented a maximum 400 V voltage stress on the semiconductors, a 97.1 % peak efficiency and unity power factor.

Artigo submetido em 14/12/2016. Primeira revisão em 05/03/2017. Aceito para publicação em 25/05/2017 por recomendação do Editor Marcelo Cabral Cavalcanti.

Keywords – Dynamic Modeling, High Voltage Gain, Power Factor Correction, State-Space Averaging, Switched-Capacitor, Unidirectional Bridgeless Boost Rectifier.

## I. INTRODUÇÃO

Conversores a capacitor chaveado têm sido amplamente estudados na literatura por apresentar circuitos simples que podem ser utilizados para a multiplicação ou divisão de tensão. Os circuitos a capacitor chaveado possuem a possibilidade de cascateamento das células, o que possibilita a expansão e a generalização do ganho estático. Devido ao princípio de funcionamento, característica discreta de ganho estático e balanço natural da tensão dos capacitores, há pouca variação do ganho em relação a variáveis controladas, como a razão cíclica e a frequência de comutação. Por conseguinte, as células de capacitor chaveado apresentam boa estabilidade e não requerem malhas adicionais de controle [1]. Em certas estruturas, existe também a possibilidade de dividir os valores de tensão entre os capacitores e semicondutores [2],[3].

Embora possuam características favoráveis referentes ao ganho e à estabilidade, os circuitos a capacitor chaveado não apresentam boa regulação de tensão, sendo assim somente capazes de multiplicar ou dividir a tensão de entrada por números inteiros. Além disso, é importante que as células de capacitor chaveado sejam muito bem dimensionadas para evitar picos elevados de corrente. Em circuitos a capacitor chaveado, são as resistências e as indutâncias parasitas dos componentes que limitam as correntes de carga e descarga. Portanto, é necessário considerar as principais resistências intrínsecas nos elementos na análise, pois são elas que definem os tempos de carga e descarga dos capacitores e, consequentemente, os valores eficazes de corrente nos mesmos [4]–[7].

Em aplicações em que se necessita de elevação de tensão e boa regulação, o conversor *boost* é uma das alternativas mais comuns, devido à sua simplicidade e boa regulação de tensão de saída e corrente de entrada. Todavia, quando ganhos muito elevados são exigidos, a estrutura *boost* torna-se inadequada por restrições relacionadas às perdas nos elementos parasitas, à não-linearidade de seu ganho estático, e aos valores de tensão sobre os semicondutores, que equivale ao valor de tensão de saída. Para correção de fator de potência, o alto ganho também prejudica a controlabilidade do conversor, pois reduz a margem de variação na razão cíclica [8]–[14].

Com a finalidade de reduzir os valores de tensão sobre os semicondutores e proporcionar alto ganho em tensão, uma alternativa é a associação células multiplicadoras de tensão a capacitor chaveado aos conversores *boost* convencionais. Isso

permite que o conversor resultante tenha a boa regulação de tensão e corrente no estágio *boost* associada às vantagens dos circuitos a capacitor chaveado [15]–[18].

Neste contexto, este artigo propõe o estudo de um novo conversor CA-CC *boost bridgeless* híbrido. As análises teórica e experimental do conversor são apresentadas. É proposto um circuito equivalente para a obtenção dos modelos dinâmicos com ordem reduzida, visto que os polos da célula de capacitor chaveado possuem frequência significativamente maior que os polos dominantes. A validação do conversor e da análise é realizada a partir de um protótipo de 1 kW com valores de tensão de 800 V na saída e 220 V na entrada.

#### II. ESTRUTURA PROPOSTA

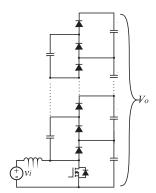

A estrutura proposta é baseada no conversor *boost* híbrido, (também conhecido como conversor *boost* multinível) proposto por [19] (Figura 1), que multiplica o ganho estático do conversor *boost* pelo número de células de capacitor chaveado do tipo *ladder* cascateadas na saída.

A análise do conversor *boost* híbrido como retificador é realizada em [20] e, com base nesse trabalho, foi desenvolvido o retificador híbrido unidirecional *bridgeless* aqui proposto.

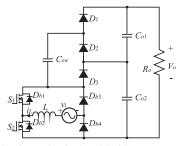

O novo retificador, mostrado na Figura 2, será referenciado como HBBR (*Hybrid bridgeless boost rectifier*). A estrutura tem como vantagens a multiplicação de tensão na saída, correção de fator de potência e redução de valores de tensão nos semicondutores. Em relação à estrutura retificadora anterior [20], o retificador apresenta menos semicondutores e, portanto, menos perdas. Entretanto, o HBBR necessita de dois semicondutores ativos, típico em estruturas do tipo *bridgeless*.

### A. Etapas de Operação

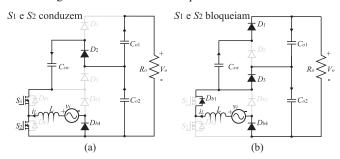

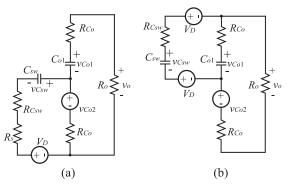

A estrutura proposta apresenta duas etapas de operação para cada semiciclo da rede e as mesmas são descritas pela Figura 3.

Fig. 1. Conversor boost híbrido generalizado.

Fig. 2. Retificador boost bridgeless híbrido.

Na primeira etapa de operação, os interruptores são comandados a conduzir, assim o indutor L e o capacitor chaveado  $C_{sw}$  armazenam energia. Na segunda etapa os interruptores são comandados a bloquear e a transferência de energia de L para  $C_{o2}$  é realizada pelos diodos  $D_{b1}$ ,  $D_{b4}$  e  $D_3$ . Durante a segunda etapa também há transferência de energia de  $C_{sw}$  para  $C_{o1}$ . Os dois interruptores possuem o mesmo sinal de comando para as duas etapas.

A única diferença entre os semiciclos positivo e negativo é referente aos diodos que conduzem na ponte. No semiciclo negativo,  $D_{b2}$  e  $D_{b3}$  conduzem nos momentos em que  $D_{b1}$  e  $D_{b4}$  conduziriam durante o semiciclo positivo.

#### B. Ganho Estático

O ganho estático ideal do conversor é obtido através da análise volts-segundo sobre o indutor (como é feito em conversores com acumulação indutiva). Sendo assim, a relação entre as tensões de entrada e saída  $v_i$  e  $V_o$  é dada por:

$$\frac{V_o}{v_i} = \frac{N+1}{1-d} \tag{1}$$

que depende da razão cíclica d e do número de células de capacitor chaveado cascateadas N.

O conversor proposto permanece com a característica de ganho estático do conversor *boost* convencional, contudo, o ganho é somado ao número de células do estágio a capacitor chaveado [13].

Uma das vantagens de utilizar o estágio multiplicador para obter maior ganho é evitar que o estágio *boost* opere com ganhos elevados, o que causa problemas referentes aos valores de tensão nos componentes e ao controle.

## C. Indutor de Entrada

O indutor de entrada L é calculado para filtrar componentes harmônicas na frequência de comutação  $f_s$  e o cálculo é feito com base na condição em que a ondulação de corrente  $\Delta i_L$  tem seu maior valor, ou seja, D=0,5 (similar ao conversor *boost* convencional) [21]. Desta forma, a indutância de entrada é descrita por:

$$L \ge \frac{V_o}{4\Delta i_L f_s(N+1)}. (2)$$

## D. Capacitor de Saída

O valor dos capacitores de saída é determinado considerando uma capacitância equivalente  $C_o'$  descrita pela associação em série dos dois capacitores de saída. A metodologia usada é a mesma que em retificadores *boost*

Fig. 3. Estados topológicos do HBBR: (a) Armazenamento de energia; (b) transferência de energia.

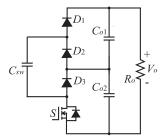

Fig. 4. Célula *ladder* equivalente para aplicações híbridas.

convencionais, ou seja, o capacitor é dimensionado para limitar a ondulação de tensão  $\Delta v_o$  na frequência da rede  $f_g$ . Logo, a capacitância é descrita por:

$$C_o' \ge \frac{P_o}{4\pi f_o V_o \Delta v_o} \tag{3}$$

em que  $P_o$  é a potência de saída.

O valor individual dos capacitores de saída ( $C_{o1}$  e  $C_{o2}$ ) é dado por  $C'_o$  multiplicado pelo número de capacitores na saída.

## III. DIMENSIONAMENTO DO CAPACITOR $C_{sw}$

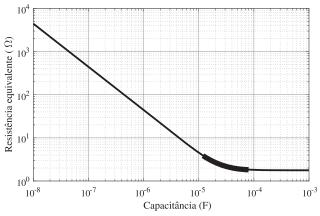

O dimensionamento do capacitor  $C_{sw}$  é realizado de forma diferente dos capacitores de saída, pois ele é utilizado como capacitor intermediário para a transferência de energia em alta frequência entre os capacitores de saída. O capacitor pode operar em três modos, os quais dependem da constante de tempo definida pela capacitância e resistência do caminho. Os modos de carga são: carga total (total charge - TC), parcial (partial charge - PC) ou sem carga (no charge - NC) [4], [22].

A operação em TC faz com que o capacitor se carregue e descarregue completamente em cada período de comutação, o que causa valores elevados de correntes eficazes. O modo NC proporciona pouca carga e descarga do capacitor em cada etapa, havendo assim pouca ondulação de corrente. Valores elevados de capacitância são necessários para tal modo de carga. Deseja-se operar o circuito em PC, o que reduz as perdas em relação ao modo TC e não exige capacitores superdimensionados.

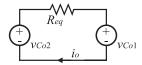

O cálculo de  $C_{sw}$  para uma operação adequada é feito através do modelo de resistência equivalente, obtido mediante análise individual da célula de capacitor chaveado, ilustrada na Figura 4. A metodologia utilizada baseia-se em [1] e consiste em representar a transferência de energia entre os capacitores de saída por um circuito equivalente, ilustrado na Figura 5, em que a resistência equivalente  $R_{eq}$  representa as perdas na célula.

O cálculo da resistência  $R_{eq}$  é feito a partir dos valores de tensão dos capacitores  $C_{o1}$  e  $C_{o2}$  e a corrente  $i_o$ . A tensão  $v_{Co2}$  é dada pela relação de ganho estático do conversor boost convencional. O valor da tensão  $v_{Co1}$  pode ser definida pela análise por espaço de estados, que proporciona o ganho estático não ideal da célula. As equações de estado são

Fig. 5. Circuito equivalente da célula de capacitor chaveado.

descritas por:

$$\begin{cases} \dot{x} = Ax + Bu \\ y = Ex + Fu \end{cases} \tag{4}$$

em que:

$$x = \begin{bmatrix} v_{Csw} \\ v_{Co_1} \end{bmatrix} \quad e \quad u = \begin{bmatrix} V_{Co_2} \\ V_D \end{bmatrix}. \tag{5}$$

As matrizes de estado são obtidas pela análise das etapas de operação. São consideradas as perdas resistivas nos MOSFETs  $R_s$  e capacitores  $R_{Co}$  e  $R_{Csw}$  e também a tensão de polarização dos diodos, como ilustrado na Figura 6.

As matrizes de estado para a primeira etapa são descritas

$$A_{1} = \begin{bmatrix} \frac{R_{Co}(2R_{Co} + R_{o})}{K_{2}C_{sw}R_{Co}} & -\frac{K_{2} - K_{1}(2R_{Co} + R_{o})}{R_{Co}K_{2}C_{sw}} \\ -\frac{R_{Co}}{C_{o1}K_{2}} & -\frac{K_{1}}{C_{o1}K_{2}} \end{bmatrix}$$

(6)

$$A_{1} = \begin{bmatrix} \frac{R_{Co}(2R_{Co} + R_{o})}{K_{2}C_{sw}R_{Co}} & -\frac{K_{2} - K_{1}(2R_{Co} + R_{o})}{R_{Co}K_{2}C_{sw}} \\ -\frac{R_{Co}}{C_{o1}K_{2}} & -\frac{K_{1}}{C_{o1}K_{2}} \end{bmatrix}$$

(6)

$$B_{1} = \begin{bmatrix} \frac{K_{2} - (K_{1} - R_{Co})(2R_{Co} + R_{o})}{K_{2}C_{sw}R_{Co}} & -\frac{R_{Co}(2R_{Co} + R_{o})}{K_{2}C_{sw}R_{Co}} \\ -\frac{K_{1} - R_{Co}}{C_{o1}K_{2}} & -\frac{R_{Co}}{C_{o1}K_{2}} \end{bmatrix}$$

(7)

$$E_1 = \begin{bmatrix} 0 & 1 \end{bmatrix} \quad \text{e} \quad F_1 = \begin{bmatrix} 0 & 1 \end{bmatrix} \tag{8}$$

em que

$$K_1 = R_{Csw} + R_S + R_{Co} (9)$$

$$K_2 = (2R_{Co} + R_o)K_1 - R_{Co}^2. (10)$$

A segunda etapa de operação é descrita por:

$$A_{2} = \begin{bmatrix} -\frac{2R_{Co} + R_{o}}{K_{3}C_{sw}} & \frac{R_{o} - R_{Co}}{K_{3}C_{sw}} \\ \frac{K_{3} - (2R_{Co} + R_{o}]R_{Csw}}{K_{3}R_{Co}C_{o1}} & \frac{R_{Csw}(R_{o} - R_{Co}) - K_{3}}{K_{3}R_{Co}C_{o1}} \end{bmatrix}$$

(11)

$$B_{2} = \begin{bmatrix} \frac{R_{Co}}{K_{3}C_{sw}} & 0\\ \frac{R_{Csw}}{C_{o}K_{3}} & 0 \end{bmatrix}$$

(12)

$$E_1 = \begin{bmatrix} 0 & 1 \end{bmatrix} \quad \text{e} \quad F_1 = \begin{bmatrix} 0 & 1 \end{bmatrix} \tag{13}$$

Fig. 6. Etapas de operação da célula ladder: (a) armazenamento de energia no capacitor  $C_{sw}$ ; (b) transferência de energia para  $C_{o1}$ .

em que:

$$K_3 = (R_{Co} + R_o)R_{Co} + R_{Csw}(2R_{Co} + R_o).$$

(14)

Dado que os capacitores de saída  $C_{o1}$  e  $C_{o2}$  possuem o mesmo valor, os mesmos são representados por  $C_o$  e as resistências série equivalentes por  $R_{Co}$ . A partir das matrizes obtidas, têm-se os valores médios quase instantâneos em um período de comutação, descritos por:

$$\begin{cases}

A = A_1D + A_2(1 - D) \\

B = B_1D + B_2(1 - D) \\

E = E_1 = E_2 \\

F = F_1 = F_2

\end{cases}$$

(15)

A partir das matrizes encontradas, calcula-se o valor de  $V_{Co_1}$  em regime permanente através de:

$$V_{Co_1} = (-EA^{-1}BU + FU) (16)$$

em que U é o valor médio do vetor de entrada.

Para a obtenção da resistência equivalente, ainda é necessário encontrar a corrente de saída, que equivale ao valor médio da corrente na segunda etapa de operação, descrita por:

$$I_o = \frac{C_{sw}}{T_s} \int_{DT_s}^{T_s} \frac{dv_{Csw}}{dt} dt = C_{sw} \Delta v_{Csw} f_s.$$

(17)

A variação de tensão  $\Delta V_{Csw}$  é dada pela subtração dos valores instantâneos de tensão no capacitor  $C_{sw}$  em cada etapa de operação  $v_a$  e  $v_b$ , descritos por:

$$v_{a} = V_{Co_{1}} \frac{R_{Co}}{R_{o}} \left( 1 - e^{-\frac{(1-D)T_{s}}{(R_{Csw} + R_{Co})C_{sw}}} \right) + V_{Co_{1}} \left( -e^{-\frac{(1-D)T_{s}}{(R_{Csw} + R_{Co})C_{sw}}} + 1 - \frac{R_{Co}}{R_{o}} \right) + V_{Co_{1}} \frac{R_{Co}}{R_{o}} e^{-\frac{(1-D)T_{s}}{(R_{Csw} + R_{Co})C_{sw}}} + v_{b}e^{-\frac{(1-D)T_{s}}{(R_{Csw} + R_{Co})C_{sw}}}$$

$$(18)$$

$$V_{Co_{2}} \left[ 1 - \frac{R_{Co}}{R_{o}} - \left( 1 - \frac{R_{Co}}{R_{o}} \right) e^{\frac{-DT_{s}}{K_{1}C_{sw}}} \right]$$

$$+ \frac{V_{Co_{1}} \left[ \frac{R_{Co}}{R_{o}} \left( 1 - e^{-\frac{(1-D)T_{s}}{(R_{Csw} + R_{Co})C_{sw}}} \right) \right] }{-\frac{(1-D)T_{s}}{(R_{Csw} + R_{Co})C_{sw}}}$$

$$-V_{Co_{1}} e^{-\frac{(1-D)T_{s}}{(R_{Csw} + R_{Co})C_{sw}}}$$

$$+ V_{Co_{1}} \frac{R_{Co}}{R_{o}} e^{-\frac{(1-D)T_{s}}{(R_{Csw} + R_{Co})C_{sw}}}$$

$$+ \frac{V_{Co_{1}} \left( +1 - \frac{2R_{Co}}{R_{o}} + \frac{R_{Co}}{R_{o}} e^{\frac{-DT_{s}}{K_{1}C_{sw}}} \right)}{-\frac{(1-D)T_{s}}{(R_{Csw} + R_{Co})C_{sw}}}$$

$$- \frac{V_{D} \left( 1 - e^{\frac{-DT_{s}}{K_{1}C_{sw}}} \right)}{(1-D)T_{s}}$$

$$(19)$$

Fig. 7. Variação da resistência equivalente em relação a  $C_{sw}$ .

Fig. 8. Circuito equivalente do conversor *boost* híbrido.

Os valores instantâneos de tensão são encontrados através da análise da corrente instantânea no início de cada etapa de operação.

Dados os valores de  $v_a$  e  $v_b$ , a resistência equivalente é descrita por:

$$R_{eq} = \frac{V_{Co_2} - V_{Co_1}}{C_{sw}(v_h - v_a)f_s}. (20)$$

O valor ideal de  $C_{sw}$  pode ser obtido através da curva ilustrada pela Figura 7, a qual relaciona a resistência equivalente com a capacitância  $C_{sw}$ . Um bom projeto de circuito deve dar preferência a valores de capacitores dentro da região destacada, pois evita perdas excessivas ou capacitores sobre-dimensionados. A região destacada representa o modo PC e as regiões à direita e à esquerda representam, respectivamente, os modos NC e TC.

#### IV. ANÁLISE DINÂMICA

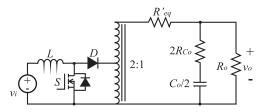

A análise dos modelos dinâmicos é realizada com base no modelo equivalente da célula de capacitor chaveado, proposto por [23] e ilustrado na Figura 8. O circuito utiliza um modelo de autotransformador ideal para valores CC e CA e o valor equivalente do capacitor de saída. Manipulando (16-19), obtém-se o valor de  $R_{eq}'$ :

$$R'_{eq} = \frac{(1-D)(V_{Co_2} - V_{Co_1})}{C_{sw}(v_b - v_a)f_s}.$$

(21)

## A. Circuito Equivalente

As matrizes referentes ao circuito equivalente na primeira etapa de operação são dadas por:

$$A_{1} = \begin{bmatrix} -\frac{R_{L} + 0.5R_{s}}{L} & 0\\ 0 & -\frac{1}{C_{o}'(R_{o} + R_{C_{o}'})} \end{bmatrix}$$

(22)

$$B_1 = \begin{bmatrix} \frac{1}{4L} & 0\\ 0 & 0 \end{bmatrix} \tag{23}$$

Para esta análise, como as etapas são refletidas para o enrolamento secundário do transformador, considera-se:

$$x = \begin{bmatrix} i_L \\ v_{C'o} \end{bmatrix} \qquad u = \begin{bmatrix} 2v_i \\ V_D \end{bmatrix}. \tag{24}$$

A segunda etapa de operação é representada por:

$$A_{2} = \begin{bmatrix} \frac{-4R_{L} - R'_{eq} - R_{o}}{4L} + \frac{R_{o}^{2}}{4L(R_{C'o} + R_{o})} & -\frac{R_{o}}{4L(R_{C'o} + R_{o})} \\ \frac{R_{o}}{C'_{o}(R_{C'o} + R_{o})} & -\frac{1}{C'_{o}(R_{C'o} + R_{o})} \end{bmatrix}$$

(25)

$$B_2 = \begin{bmatrix} \frac{1}{4L} & -\frac{1}{2L} \\ 0 & 0 \end{bmatrix}$$

(26)

em que  $C'_o$  é o valor da capacitância equivalente de saída, dada por  $C_o/2$ .  $R_{C'o}$  é a resistência série equivalente do capacitor  $C'_o$ , dada por  $2R_{Co}$ .

Para ambas as etapas, a matriz F tem valor nulo e a matriz E para a obtenção das plantas de tensão e corrente são respectivamente:

$$E_{\nu} = \begin{bmatrix} 0 & 1 \end{bmatrix}$$

e  $E_{i} = \begin{bmatrix} 1 & 0 \end{bmatrix}$ . (27)

Após linearizar as matrizes, as funções de transferência da tensão de saída e da corrente de entrada em função da razão cíclica são descritas por:

$$G(s) = E(sI - A)^{-1}[(A_1 - A_2)X + (B_1 - B_2)U]$$

(28)

em que I é a matriz identidade com dimensão relativa ao número de variáveis de estado.

Para escolher a variável de saída  $(\hat{v}_o \text{ ou } \hat{i}_L)$  que se deseja encontrar em função da razão cíclica  $\hat{d}$ , a matriz E relativa à saída desejada  $(E_v \text{ ou } E_i)$  deve ser substituída em (28). A função de transferência da tensão de saída em função da corrente de entrada pode ser obtida através da divisão entre as duas funções de transferência.

## B. Análise dos Modelos Dinâmicos

A análise dos modelos dinâmicos considera os mesmos parâmetros utilizados no protótipo, que são descritos na Tabela I.

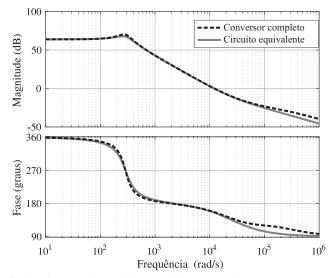

Os diagramas de Bode do modelo equivalente proposto e do modelo completo de quarta ordem do conversor HBBR são apresentados e comparados na Figura 9. A comparação é realizada para verificar matematicamente a possibilidade do uso do circuito equivalente na análise dinâmica. Os cálculos para o modelo dinâmico do conversor completo são apresentados no Apêndice.

Ao analisar os diagramas de Bode das funções de transferência de tensão dos conversores, observa-se que eles apresentam respostas em frequência semelhantes, como mostra a Figura 9.

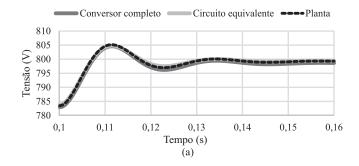

Por meio de simulação pelo *software* PSIM, é possível validar as plantas de tensão e corrente ao observar a resposta a uma perturbação de razão cíclica de 0,01. Os pontos simulados foram traçados no *software Excel* para melhor visualização e as curvas são ilustradas na Figura 10. Observa-se que o conversor completo, o circuito equivalente e as plantas calculadas possuem respostas dinâmicas similares. Isto ocorre porque os polos e zeros da parcela *boost* são dominantes em relação aos polos e zeros da parcela do capacitor chaveado, que se encontram em frequências mais elevadas.

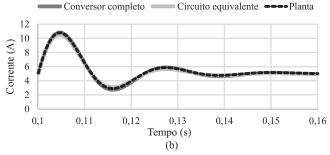

#### C. Controle

O controle da estrutura HBBR é feito de forma similar ao retificador *boost* convencional, através de controladores de tensão e de corrente cascateados e desacoplados por frequência. Por ser um retificador *boost* unidirecional, a referência de seno (dada pela leitura da tensão de entrada) e a realimentação de corrente são retificadas (igual ao retificador *boost* convencional) [24]. O diagrama de blocos do sistema em malha fechada é descrito pela Figura 11.

TABELA I Especificações do Protótipo

| Componente                                         | Especificação                           |  |  |  |

|----------------------------------------------------|-----------------------------------------|--|--|--|

| Potência nominal                                   | 1000 W                                  |  |  |  |

| Tensão de entrada (RMS)                            | 220 V                                   |  |  |  |

| Frequência da rede                                 | 60 Hz                                   |  |  |  |

| Frequência de comutação                            | 100 kHz                                 |  |  |  |

| Tensão de saída                                    | 800 V                                   |  |  |  |

| Indutor $L$                                        | 1,67 mH                                 |  |  |  |

| Capacitores de saída $C_{o1}$ e $C_{o1}$           | 2 capacitores eletrolíticos de          |  |  |  |

|                                                    | $470 \mu F / 500 V$ conectados          |  |  |  |

|                                                    | em paralelo para cada nível             |  |  |  |

| RSE dos capacitores de saída $R_{Co1}$ e $R_{Co2}$ | 0,11 Ω                                  |  |  |  |

| Capacitor chaveado $C_{sw}$                        | $40 \mu F / 500 V$ (capacitor de filme) |  |  |  |

| Tensão direta nos diodos $V_D$                     | 1,3 V                                   |  |  |  |

| Resistência nos MOSFETS R <sub>s</sub>             | 0,08 Ω                                  |  |  |  |

Fig. 9. Diagrama de Bode dos modelos encontrados.

Fig. 10. Resposta ao degrau de razão cíclica: (a) tensão de saída, (b) corrente de entrada.

Fig. 11. Diagrama de blocos do sistema em malha fechada.

#### V. RESULTADOS EXPERIMENTAIS

Um protótipo foi desenvolvido para validar experimentalmente as análises feitas. A fotografia do protótipo implementado é ilustrada na Figura 12 e as especificações utilizadas são listadas na Tabela I.

O conversor foi controlado com o DSP TMS320F28069 da Texas Instruments. A frequência de amostragem utilizada foi de 100 kHz (uma amostra por período comutação). Controladores proporcional integrais desacoplados por frequência foram utilizados para o controle das malhas interna e externa. Os controladores foram projetados a partir das funções de transferência obtidas pelo modelo equivalente, que considera a célula de capacitor chaveado como um autotransformador e uma resistência equivalente. Utilizou-se interruptores MOSFET IPW65R080CFD e diodos SCS208AM de SiC no estágio de potência. Foram utilizados capacitores eletrolíticos EPCOS B43501 no filtro de saída, e para  $C_{sw}$  foi utilizado um capacitor de filme Panasonic EZP-E50406MTA.

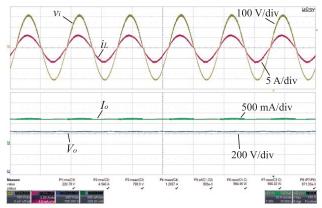

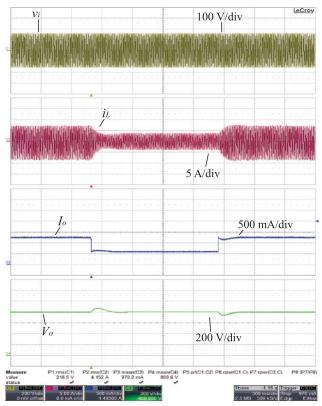

O protótipo operou adequadamente em potência nominal, como mostra a Figura 13. Observa-se que o conversor controla a tensão de saída em 798,8 V e a corrente de entrada possui envoltória senoidal.

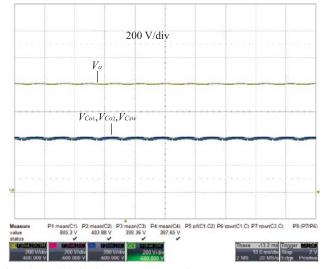

A transferência de energia entre os capacitores da célula multiplicadora é realizada de forma adequada, sendo que a tensão nos capacitores é balanceada, conforme mostra a Figura 14. O balanço natural de tensão ocorre quando há pouca queda de tensão na transferência de energia entre os

capacitores, o que é obtido por meio do dimensionamento adequado do capacitor  $C_{sw}$ , responsável pela transferência.

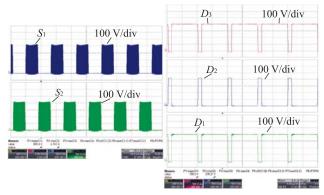

A divisão de tensão sobre os capacitores é refletida nos interruptores, sendo que os valores de tensão equivalem à metade da tensão de saída, como mostra a Figura 15.

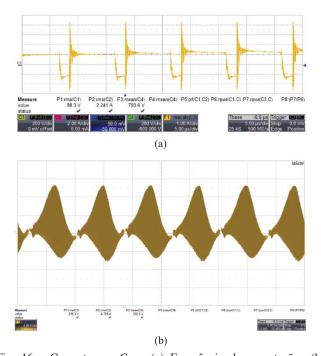

Percebe-se na Figura 16 (a) que o projeto do capacitor  $C_{sw}$  foi feito de forma adequada, pois o dimensionamento inadequado ocasionaria correntes com picos elevados em cada etapa, o que aumenta o valor eficaz da corrente, reduz o rendimento e provoca elevada queda de tensão nos capacitores. As medições de corrente em  $C_{sw}$  foram realizadas com uma sonda Rogowski, o que resultou em curvas com ruído de

Fig. 12. Protótipo do HBBR.

Fig. 13. Operação em carga nominal.

Fig. 14. Equilíbrio de tensão nos capacitores.

Fig. 15. Tensão sobre os semicondutores.

Fig. 16. Corrente em  $C_{sw}$ : (a) Frequência de comutação; (b) Frequência da rede.

medição. Entretanto, ainda é possível verificar a envoltória das curvas obtidas. Na Figura 16 (b), percebe-se que a a transferência de energia ocorre no dobro da frequência da rede, devido à característica do retificador dois níveis.

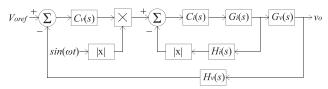

A regulação da tensão de saída e da corrente de entrada foi realizada através de controladores do tipo PI. Como mostra a Figura 17, o controlador responde adequadamente a um degrau descendente e ascendente de 50 % da carga nominal e mantém a tensão média de saída com valor próximo de 800 V. Além disto, o sistema mostrou-se robusto em termos de estabilidade durante as perturbações de carga.

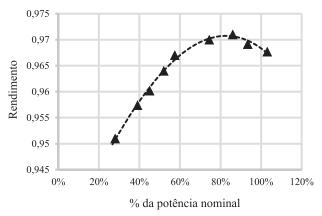

A estrutura estudada apresentou bom rendimento, como mostra a Figura 18. O maior rendimento obtido foi de 97,1 % com 86 % da potência nominal. Para a operação em carga nominal, foi obtido rendimento de 96,77 %.

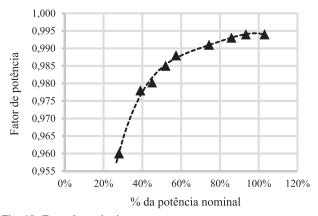

O fator de potência da estrutura foi traçado em função da potência nominal, como mostra a Figura 19. Observa-se que o conversor apresenta fator de potência próximo à unidade. O fator de potência obtido com operação em potência nominal foi de 0,993.

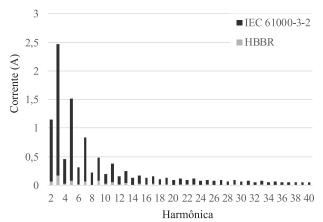

Foi obtido o espectro harmônico da corrente de entrada

Fig. 17. Resposta ao degrau de carga.

Fig. 18. Curva de rendimento.

Fig. 19. Fator de potência.

Fig. 20. Espectro harmônico.

TABELA II Comparação entre as topologias

| Recurso                                | NPC   | BDR   | CW     | HBR    | HBBR   |

|----------------------------------------|-------|-------|--------|--------|--------|

| Número mínimo de semicondutores        | 12    | 8     | 6      | 8      | 7      |

| Necessita de comandos complementares   | Sim   | Não   | Não    | Não    | Não    |

| Semicondutores submetidos a $V_o$      | 0     | 4     | 0      | 0      | 0      |

| Semiconductores submetidos a $V_o/2$   | 12    | 4     | 6      | 8      | 7      |

| Número mínimo de capacitores           | 2     | 2     | 4      | 3      | 3      |

| Conteúdo harmônico em baixa frequência |       |       |        |        |        |

| nos capacitores de saída               | $f_g$ | $f_g$ | $2f_g$ | $2f_g$ | $2f_g$ |

| Pode ser expandido em mais níveis      | Sim   | Não   | Sim    | Sim    | Sim    |

em plena carga e foi realizada a comparação com os limites estabelecidos pela norma IEC 61000-3-2. Observa-se na Figura 20 que as componentes harmônicas de corrente são significativamente menores que os limites estabelecidos pela norma.

Para avaliar as vantagens e desvantagens da topologia apresentada, as características do HBBR são comparadas a outras soluções apresentadas na literatura na Tabela II. Os retificadores escolhidos são o conversor com ponto neutro grampeado (neutral-point clamped - NPC), o retificador boost dobrador de tensão (boost doubler rectifier - BDR), o retificador baseado na célula Cockcroft-Walton (CW), o retificador boost híbrido (HBR) e a estrutura estudada neste trabalho (HBBR). As estruturas NPC, BDR, CW e HBR são apresentadas, respectivamente, nas referências [25], [26], [27] e [20].

## VI. CONCLUSÕES

Foram realizadas as análises teórica e experimental da estrutura de retificador *boost bridgeless* híbrida, que multiplica o ganho do conversor *boost* por meio de uma célula de capacitor chaveado tipo *ladder*. A estrutura estudada foi capaz de elevar a tensão na saída de forma que a tensão é dividida entre os interruptores.

Foi proposta a utilização de um circuito equivalente para a obtenção dos modelos dinâmicos da estrutura. O modelo dinâmico foi validado por simulação e utilizado na experimentação.

Uma metodologia de dimensionamento de  $C_{sw}$  foi proposta com base na resistência equivalente do circuito e ela se

mostrou adequada. O dimensionamento adequado de  $C_{sw}$  proporcionou bom comportamento em relação às correntes de carga e descarga e, por conseguinte, a transferência adequada de energia entre os capacitores, visto que os capacitores apresentaram balanço natural de tensão.

As validações experimentais mostraram que a estrutura apresenta alto fator de potência, alto rendimento e boa regulação de tensão de saída e corrente de entrada.

O HBBR foi comparado a estruturas anteriores propostas na literatura e mostrou-se uma boa alternativa para retificadores com correção de fator de potência. A estrutura tem a vantagem de utilizar um único comando para todos os interruptores, o que o torna robusto por não haver problemas com curtocircuito de braço. Em comparação ao HBR [20], a estrutura proposta tem a vantagem de possuir menos componentes semicondutores e apresentar melhor rendimento em virtude disto.

#### **APÊNDICE**

A função de transferência do sistema completo de quarta ordem foi obtida para comparar a resposta em frequência com o modelo equivalente e assim validar matematicamente a possibilidade de usar o circuito equivalente. Como feito na estrutura equivalente, utilizou-se a aproximação por espaço de estados. Para a primeira etapa de operação, as matrizes de estado são descritas por:

$$A_{1} = \begin{bmatrix} \frac{-R_{L}K_{4} - R_{o}}{K_{4}L} & \frac{R_{s}K_{4} - R_{o}}{R_{s}K_{4}L} & \frac{-K_{5}}{K_{6}L} & \frac{-R_{o}}{K_{4}R_{co}L} \\ \frac{R_{o} - R_{s}K_{4}}{R_{s}K_{4}C_{sw}} & \frac{R_{o} - R_{s}K_{4}}{R_{s}^{2}K_{4}C_{sw}} & \frac{K_{5}}{R_{s}K_{6}C_{sw}} & \frac{R_{o} + R_{Co}}{K_{6}C_{sw}} \\ \frac{-1}{K_{4}C_{o}} & \frac{-1}{R_{s}K_{4}C_{o}} & \frac{-R_{s} - R_{Co}}{K_{6}C_{o}} & \frac{-1}{K_{4}R_{co}C_{o}} \\ \frac{R_{o}}{K_{6}C_{o}} & \frac{R_{o}}{K_{6}C_{o}} & \frac{K_{5}}{K_{6}R_{co}C_{o}} & \frac{R_{o} - R_{Co}K_{4}}{R_{c}^{2}K_{4}C_{o}} \end{bmatrix}$$

(29)

$$B_{1} = \begin{bmatrix} \frac{1}{L} \\ 0 \\ 0 \\ 0 \\ 0 \end{bmatrix}$$

(30)

em que:

$$K_4 = \frac{R_s R_{Co} + (R_s + R_{Co})(R_{Co} + R_o)}{R_s R_{Co}}$$

(31)

$$K_5 = (R_o + R_{Co})(R_s + R_{Co}) - K_4 R_s R_{Co}$$

(32)

$$K_6 = R_s R_{Co} K_4. \tag{33}$$

A segunda etapa de operação é representada por:

$$A_{2} = \begin{bmatrix} -\frac{R_{o}}{R_{o}L} & \frac{R_{Co}}{R_{o}L} & 0 & \frac{R_{Co}}{R_{o}L} \\ \frac{R_{Con}}{R_{o}C_{sw}} & -\frac{R_{o}+2R_{Co}}{R_{o}R_{Co}C_{sw}} & \frac{1}{R_{Co}C_{sw}} & \frac{-1}{R_{o}C_{sw}} \\ 0 & \frac{1}{R_{Co}C_{o}} & -\frac{1}{R_{Co}C_{o}} & 0 \\ \frac{1}{R_{o}C_{o}} & \frac{-1}{R_{o}C_{o}} & 0 & \frac{-1}{R_{o}C_{o}} \end{bmatrix}$$

(34)

$$B_2 = B_1. (35)$$

Para o modelo que considera o conversor completo, os vetores de estado e de entrada são descritos por:

$$x = \begin{bmatrix} i_L \\ v_{Csw} \\ v_{Co1} \\ v_{Co2} \end{bmatrix} \quad e \quad u = v_i. \tag{36}$$

Assim como no modelo equivalente, a saída não tem relação direta com nenhuma variável de entrada, portanto F tem valor nulo. As matrizes de saída  $E_{\nu}$  e  $E_{i}$ , referentes à tensão de saída e corrente de entrada, respectivamente, são descritas, por:

$$E_{v} = \begin{bmatrix} 0 & 0 & 1 & 1 \end{bmatrix}$$

e  $E_{i} = \begin{bmatrix} 1 & 0 & 0 & 0 \end{bmatrix}$ . (37)

As funções de transferência do conversor em função da razão cíclica  $\hat{d}$  são descritas por (28), assim como no modelo equivalente.

#### REFERÊNCIAS

- [1] J. C. Dias, T. B. Lazzarin, "Steady State Analysis of Voltage Multiplier Ladder Switched-Capacitor Cell", in 12th IEEE/IAS International Conference on Industry Applications (INDUSCON), pp. 1–6, 2016.

- [2] A. Ioinovici, "Switched-capacitor power electronic circuits", *IEEE Circuits and Systems Magazine*, vol. 1, no. 3, pp. 37–42, Aug 2002.

- [3] S. L. Bin Wu, S. Singer, "A Family of twoswitch boosting switched-capacitor converters", *IEEE Transactions on Power Electronics*, vol. 30, no. 10, pp. 5413–5425, Oct 2014.

- [4] J. W. Kimball, P. T. Krein, K. R. Cahill, "Modelling of capacitor impedance in switching converters", *IEEE Power Electronics Letters*, vol. 3, no. 4, pp. 136–140, Dec 2005.

- [5] Y.-H. Chang, "Design and analysis of power-CMOS-gate-based switched-capacitor boost DC-AC inverter", *IEEE Transactions on Circuits and Systems I*, vol. 51, no. 10, pp. 6035–6041, Oct 2004.

- [6] S. Ben-Yaakov, "Behavioral average modeling and equivalent circuit simulation of switched capacitors converters", *IEEE Transactions on Circuits and Systems I*, vol. 27, no. 2, pp. 632–636, Oct 2011.

- [7] M. D. Vecchia, T. B. Lazzarin, I. Barbi, "Estudo de Conversores Estáticos CA-CA Monofásicos e Trifásicos Baseados no Princípio do Capacitor Chaveado", *Eletrônica de Potência*, vol. 20, no. 2, pp. 160–171, mar./mai. 2015.

- [8] A. D. B. Lange, T. B. Soeiro, M. S. Ortmann, M. L. Heldwein, "Three-Level Single-Phase Bridgeless PFC Rectifiers", *IEEE Transactions on Power Electronics*, vol. 30, no. 6, pp. 2935–2949, Jun 2015.

- [9] M. L. Heldwein, T. K. Jappe, R. R. Polla, A. Fuerback, T. B. Soeiro, R. Andrich, "An FPGA-based Interleaved Boost-type PFC Rectifier Employing GaN HEMT

- Devices", Eletrônica de Potência, vol. 19, no. 4, pp. 414–422, set./nov. 2014.

- [10] A. Marcos-Pastor, E. Vidal-Idiarte, A. Cid-Pastor, L. Martinez-Salamero, "Interleaved digital power factor correction based on the sliding-mode approach", *IEEE Transactions on Power Electronics*, vol. 31, no. 6, pp. 1792–1800, Jun 2016.

- [11] S. Lim, D. M. Otten, D. J. Perreault, "New AC-DC power fator correction architecture suitable for high-frequency operation", *IEEE Transactions on Power Electronics*, vol. 31, no. 4, pp. 2937–2949, Apr 2016.

- [12] J. A. P. Jakson Paulo Bonaldo, Helmo Kelis Morales Paredes, "Controle Flexível para Conversores Monofásicos Conectados a Sistemas Elétricos Distorcidos de Baixa Tensão", Eletrônica de Potência, vol. 19, no. 4, pp. 354–367, set./nov. 2014.

- [13] G. V. Silva, R. F. Coelho, T. B. Lazzarin, "Switched-capacitor differential boost inverter: Static gain and generalized structure", in 42nd IEEE/IAS International Conference on Industry Applications, pp. 1–6, 2016.

- [14] J. C. Rosas-Caro, J. M. Ramirez, P. M. Garcia-Vite, "Novel DC-DC multilevel boost converter", *in IEEE Annual Power Electronics Specialist Conference* (*PESC*), pp. 2146–2451, 2008.

- [15] Y. Tang, T. Wang, Y. He, "Generalized multicell switched-inductor/switched-capacitor combined active-network converters", *IEEE Transactions on Power Electronics*, vol. 30, no. 4, pp. 2063–2072, Apr 2015.

- [16] D. F. Cortez, G. Waltrich, J. Fraigneaud, H. Miranda, I. Barbi, "DC-DC converter for dual-voltage automotive systems based on bidirectional hybrid switched-capacitor architectures", *IEEE Transactions on Industrial Electronics*, vol. 62, no. 5, pp. 3296–3304, May 2015.

- [17] Y. Tang, T. Wang, Y. He, "A Switched-Capacitor-Based Active-Network Converter With High Voltage Gain", *IEEE Transactions on Industrial Electronics*, vol. 29, no. 6, pp. 2959–848, Jun 2014.

- [18] F. H. Dupont, C. Rech, R. Gules, J. R. Pinheiro, "Reduced-order model and control approach for the boost converter with a voltage multiplier cell", *IEEE Transactions on Power Electronics*, vol. 28, no. 7, pp. 3395–3404, Jul 2013.

- [19] J. C. Mayo-Maldonado, R. Salas-Cabrera, J. C. Rosas-Caro, J. D. Leon-Morales, E. N. Salas-Cabrera, "Modelling and control of a DC-DC multilevel boost converter", *IET Power Electronics*, vol. 4, no. 6, pp. 693–700, Oct 2010.

- [20] D. F. Cortez, M. Maccarini, S. A. Mussa, I. Barbi, "High Static Gain Single-phase PFC Based on a Hybrid Boost Converter", *International Journal of Electronics*, Oct 2016.

- [21] B. A. Miwa, D. M. Otten, M. F. Schelcht, "High efficiency power factor correction using interleaving techniques", in Applied Power Electronics Conference and Exposition (APEC 92), pp. 557–568, 1992.

- [22] M. D. Vecchia, T. B. Lazzarin, I. Barbi, "A three-phase AC-AC Converter in open-delta connection based on

- switched capacitor principle", *IEEE Transactions on Industrial Electronics*, vol. 62, no. 10, pp. 6035–6041, Oct 2015.

- [23] G. V. Silva, R. F. Coelho, T. B. Lazzarin, "State space modeling of a hybrid switched-capacitor boost converter", in *IEEE 13th Brazilian Power Electronics Conference and 1st Southern Power Electronics Conference (COBEP/SPEC)*, pp. 1–6, 2015.

- [24] A. Prodic, D. Maksimovic, R. Erickson, "Dead-zone digital controller for improved dynamic response of power factor preregulators", in Eighteenth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), pp. 382–388, 2003.

- [25] S. Wang, W. Song, J. Zhao, X. Feng, "Hybrid single-carrier-based pulse width modulation scheme for single-phase three-level neutral-point-clamped grid-side converters in electric railway traction", *IET Power Electronics*, vol. 9, no. 13, pp. 2500–2509, Oct 2016.

- [26] D. Maksimovic, R. Erickson, "Universal-input, high-power-factor, boost doubler rectifiers", *in Tenth Annual Applied Power Electronics Conference and Exposition* (APEC '95), pp. 459–465, 1995.

- [27] C.-M. Young, M.-H. Chen, C.-C. Ko, "High power factor transformerless single-stage single-phase ac to

high-voltage dc converter with voltage multiplier", *IET Power Electronics*, vol. 5, no. 2, pp. 149–157, Mai. 2012

#### DADOS BIOGRÁFICOS

Julio Cesar Dias, nascido em Blumenau, SC, Brasil em 1991, recebeu o grau de Engenheiro Eletricista pela Universidade Regional de Blumenau (FURB) em 2015 e mestre em Engenharia Elétrica pela Universidade Federal de Santa Catarina (UFSC) em 2017. Atualmente é aluno de doutorado no Instituto de Eletrônica de Potência (INEP) da Universidade Federal de Santa Catarina (UFSC) e membro estudante da Associação Brasileira de Eletrônica de Potência (SOBRAEP).

Telles Brunelli Lazzarin, nascido em Criciúma, SC, Brasil em 1979, recebeu o grau de Engenheiro Eletricista, mestre e doutor pela Universidade Federal de Santa Catarina (UFSC), Florianópolis, Brasil, em 2004, 2006 e 2010, respectivamente. Atualmente é professor no Departamento de Engenharia Elétrica e Eletrônica (EEL) da Universidade Federal de Santa Catarina (UFSC), pesquisador no Instituto de Eletrônica de Potência (INEP) e membro da Associação Brasileira de Eletrônica de Potência (SOBRAEP).