# SIMULAÇÃO EM TEMPO REAL DE ALGORITMOS DE EQUALIZAÇÃO DAS TENSÕES CC DE UM CONVERSOR MULTINÍVEL MODULAR

Frederico T. Ghetti<sup>1,2</sup>, Andrei de O. Almeida<sup>1</sup>, Pedro M. Almeida<sup>1</sup>, Pedro G. Barbosa<sup>1</sup>

<sup>1</sup>Universidade Federal de Juiz de Fora, Juiz de Fora – MG, Brasil

<sup>2</sup>Instituto Federal do Sudeste de Minas Gerais, Juiz de Fora – MG, Brasil

e-mail: frederico.ghetti@ifsudestemg.edu.br, andrei.almeida@engenharia.ufjf.br

pedro.machado@ufjf.edu.br, pedro.gomes@ufjf.edu.br

Resumo – Este artigo apresenta um estudo comparativo de estratégias usadas para ordenar e selecionar os submódulos de um conversor multinível modular em função das tensões CC dos seus capacitores. conversores foram propostos para aplicações em alta tensão devido a possibilidade da expansão do número de módulos permitindo obter tensões elevadas em seus terminais de saída. Além da modularidade, a síntese de tensões com múltiplos níveis permite que eles sejam conectados a rede sem estruturas magnéticas complexas ou filtros harmônicos de ordem elevada. de simulação em tempo real são apresentados para validar as estratégias de equalização investigadas e demonstrar o desempenho dos algoritmos implementados no processador digital de sinais. Finalmente, resultados experimentais obtidos com um protótipo em pequena escala, com três submódulos por polo, são apresentados para validar os resultados da simulação em tempo real.

Palavras-chave – Algoritmo de Ordenação, Balanceamento das Tensões dos Capacitores, Conversor Multinível Modular, Simulação em Tempo Real.

# REAL TIME SIMULATION OF DC VOLTAGE EQUALIZATION ALGORITHMS OF A MODULAR MULTILEVEL CONVERTER

Abstract - This paper presents a comparative study of different strategies used to sort and select the submodules of a modular multilevel converter according to their capacitor DC voltages. These converters have been initially proposed for high voltage applications due to the possibility to expand the number of modules allowing high-voltage levels at the converter output terminals. Besides the modularity, the synthesis of multilevel voltages allow them to be connected to the mains without complex magnetic structures or high-order harmonic filters. Real time simulation results are used to validate the control strategies investigated and to demonstrate the performance of the algorithms implemented on a digital signal processor. Finally, experimental results obtained with a small-scale prototype with three submodules per branch are presented to validate the real time simulation results.

Artigo submetido em 04/01/2017. Primeira revisão em 23/03/2017. Aceito para publicação em 13/06/2017 por recomendação do Editor Marcelo Cabral Cavalcanti.

*Keywords* - Capacitor Voltage Balancing, Modular Multilevel Converter, Real Time Simulation, Sorting Algorithm.

#### I. INTRODUÇÃO

Conversores multiníveis modulares (do inglês, *Modular Multilevel Converters*) (MMC) foram originalmente propostos para aplicações em redes elétricas com tensões elevadas sem o uso de estruturas magnéticas complexas ou filtros harmônicos de ordem elevada [1]. Contudo, para garantir o correto funcionamento do MMC, as tensões CC dos diversos submódulos (SM) devem ser reguladas para evitar que distorções e desequilíbrios apareçam nas tensões e correntes sintetizadas nos terminais de saída.

Em [2] foram usados os estados redundantes da estratégia de modulação vetorial (do inglês, *Space Vector Modulation*) (SVM) para controlar as tensões CC dos SM do MMC. Já em [3] é utilizada uma modulação com portadoras defasadas para controlar as tensões de cada SM sem a medição das correntes dos polos do MMC. Em [4], Hagiwara e Akagi utilizaram controladores individuais para regular as tensões dos SM.

Outros trabalhos propõem o uso de controladores que empregam número reduzido de sensores de tensão [5], [6]. Encontram-se também trabalhos onde são projetados observadores não lineares para diminuir o número de canais de informação entre os SM e o regulador da tensão CC do MMC [7]. Contudo, independente da metodologia, o emprego de algoritmos de ordenação desempenham um papel fundamental sobre a operação do MMC, já que nas aplicações em altas tensões estes utilizam um grande número de SM [8]–[10].

Diferentes algoritmos podem ser usados para ordenar as tensões CC dos MMC [11]. O desempenho de cada um dependerá: (i) da quantidade de tensões que deverão ser ordenadas e (ii) da forma como estas tensões estão desorganizadas na estrutura. A falta de um estudo comparativo até o momento não permite obter uma conclusão a respeito de um algoritmo mais apropriado para realizar tal tarefa [12], [13].

Ainda dentro deste contexto, a simulação em tempo real de controladores, ou simplesmente simulação *Control-Hardware-in-the-Loop* (CHIL), tem desempenhado um papel fundamental na depuração e testes de algoritmos de controle de conversores eletrônicos de média e elevada potência [14], [15]. A utilização de plataformas dedicadas de simulação em tempo real, permite não só otimizar os códigos de novos controladores, mas também minimizar os custos e reduzir o tempo de desenvolvimento.

Neste sentido, este artigo apresenta um estudo comparativo de diferentes métodos de ordenação aplicados ao controle e equalização das tensões dos capacitores de um MMC. Diferente de outros estudos publicados na literatura, a maior parte dos resultados apresentados neste artigo foram obtidos com um modelo digital de um conversor MMC implementado na plataforma em tempo real HIL-600 da Typhoon. As rotinas de controle do conversor, bem como os diferentes métodos de ordenação investigados, foram implementados em um DSP TMS320F28335 da Texas Instruments e simulados numa configuração CHIL com o Typhoon HIL. Finalmente, o DSP, com os algoritmos de controle testados, foi usado para controlar um protótipo em pequena escala de um conversor MMC com três SM por polo.

#### II. PRINCÍPIOS DE FUNCIONAMENTO DO MMC

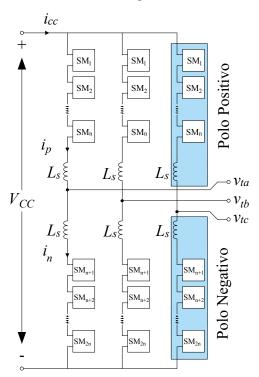

A Figura 1 mostra o diagrama esquemático de um MMC trifásico onde cada fase é formada pela conexão em cascata de n submódulos no polo positivo e n submódulos no polo negativo, conectados ao terminal CA do conversor através de dois indutores  $L_S$ . Estes indutores, além de funcionar como filtros harmônicos, limitam o fluxo de corrente circulante nos polos positivo e negativo do conversor devido as ondulações e desequilíbrios das tensões dos capacitores dos SM.

Fig. 1. Diagrama esquemático do MMC trifásico com conexão das fases em dupla estrela.

As topologias em meia ponte e em ponte completa são as mais empregadas para a síntese dos SM [1], [8], [16], [17]. Não obstante, SM formados por conversores com o neutro grampeado a diodos (do inglês, *Neutral Point Clamped*) (NPC) e com o neutro grampeado com capacitores (do inglês, *Flying Capacitor*) (FC) são propostos em [18], [19], enquanto em [20] é utilizada uma topologia duplamente grampeada.

#### A. Modulação Multiportadoras

Diferentes técnicas de modulação podem ser usadas para sintetizar as tensões de saída do MMC. Devido a simplicidade e facilidade de implementação, destacam-se àquelas baseadas em múltiplas portadoras e algoritmos de ordenação [9], [21], [22].

De uma maneira geral, considerando um conversor com n submódulos por polo, pode-se sintetizar uma tensão de fase com (n+1) níveis sempre que o número de submódulos ativos por fase for n. Neste caso, a diferença de potencial nos terminais dos indutores  $L_S$  será teoricamente nula.

Não obstante, pode-se sintetizar tensões com (2n+1) níveis se o número de SM ativos variar entre (n-1), n e (n+1). Neste caso, os indutores dos polos são submetidos a uma ddp igual a diferença entre a tensão do barramento CC e a dos SM ativos. Apesar da estratégia (2n+1) sintetizar tensões com um maior número de níveis, observa-se um aumento na ondulação da corrente dos polos do MMC [23], [24].

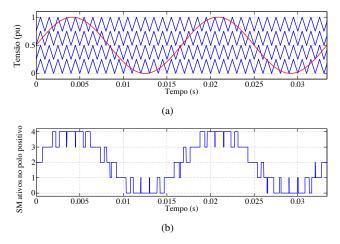

Assim sendo, neste artigo optou-se pela modulação PD-PWM (*Phase Disposition - Pulse-Width Modulation*) onde um sinal de referência é comparado com n portadoras triangulares, deslocadas simetricamente em relação ao eixo horizontal, para gerar uma tensão de saída com (n+1) níveis [8].

Na Figura 2 (a) são mostradas as formas de onda do sinal de referência e das portadoras triangulares quando n=4. Já na Figura 2 (b) é mostrado o sinal que indica, em cada instante de tempo, quantos SM deverão estar ativos no polo positivo do MMC. Este sinal é obtido a partir da comparação do sinal de referência com as portadoras triangulares sendo possível escrever a seguinte relação:

$$m_n = (n - m_p) \tag{1}$$

onde n é o número de submódulos por polo do MMC,  $m_p$  é o número de submódulos ativos no polo positivo e  $m_n$  representa o número de submódulos ativos no polo negativo.

Fig. 2. (a) Modulação PD-PWM para n = 4, (b) Número de SM ativos no polo positivo de uma fase do MMC.

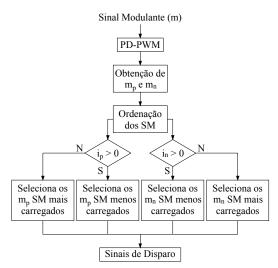

Nesta técnica de modulação, a geração dos sinais de acionamento dos interruptores fica a cargo do algoritmo de equalização das tensões dos capacitores, como será discutido a seguir.

#### B. Equalização das Tensões dos Capacitores dos SM

Duas estratégias são comumente usadas para equalizar as tensões nos capacitores dos SM. A primeira estratégia consiste em projetar controladores individuais para regular as tensões de cada SM [4]. A segunda estratégia utiliza um algoritmo para ordenar os SM em função das tensões de seus capacitores. Posteriormente, o algoritmo determina quais submódulos devem ficar ativos e/ou inativos [8]. Neste trabalho é empregado o segundo método.

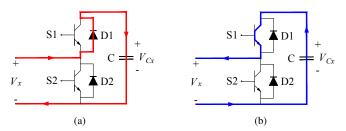

Na Figura 3 é mostrado como o capacitor pode ser carregado ou descarregado em função do sentido da corrente pelo SM quando o interruptor está ativo. O processo de equalização das tensões inicia-se determinando o número de SM que devem estar ativos nos polos positivo e negativo ( $m_p$  e  $m_n$ ), bem como o sentido da corrente nos dois polos ( $i_p$  e  $i_n$ ). Se a corrente no polo for positiva, seleciona-se os SM cujos capacitores estão menos carregados, para que os mesmos se carreguem. Por outro lado, se a corrente pelo polo for negativa, o algoritmo seleciona os SM cujos capacitores estão mais carregados, para que os mesmos se descarreguem.

Fig. 3. Processo de carga e descarga do capacitor quando o sentido da corrente é: (a) positivo e (b) negativo.

Na Tabela I é mostrada a relação entre os possíveis estados dos interruptores do SM da Figura 3 e o efeito no processo de carga/descarga do capacitor e na tensão terminal do submódulo,  $V_x$ . A tensão  $V_{Cx}$  representa o valor médio da tensão de saída do SM,  $V_{CC}$  é a tensão total do barramento CC do MMC e n representa o número de submódulos por polo do conversor.

TABELA I Tensão nos Terminais dos SM

| Estado  | S1      | S2       | V <sub>x</sub> | Ix  | Capacitor  |

|---------|---------|----------|----------------|-----|------------|

| ativo   | fechado | aberto   | $V_{CC}$       | >0  | carrega    |

| ativo   | rechado | aberto   | n              | < 0 | descarrega |

| inativo | aberto  | fechado  | 0              | > 0 | bypassed   |

| mativo  | aberto  | icciiado | 0              | < 0 | bypassed   |

Pelo exposto, verifica-se que a ordenação dos SM em função das tensões de seus capacitores é fundamental para sintetizar uma tensão multinível nos terminais CA do MMC. Por este motivo, o algoritmo de ordenação deve ser rápido o suficiente para ranquear os SM, em função das tensões dos seus capacitores, a cada ciclo de trabalho do controlador. A Figura 4 ilustra o fluxograma desta estratégia de equalização.

# III. MÉTODOS DE ORDENAÇÃO

Diferentes métodos de ordenação podem ser usados para controlar as tensões dos SM do MMC [11]. O desempenho de cada um depende basicamente de dois fatores: (*i*) quantidade

Fig. 4. Algoritmo de equalização das tensões nos SM de forma esquemática.

de dados a serem ordenados (n) e (ii) forma como os dados estão desorganizados. O pior caso ocorre quando os dados, no caso as tensões, estão dispostas em ordem inversa a que se deseja ordenar. Por outro lado, quando os dados já estão ordenados o tempo de execução será menor, sendo este considerado o melhor caso.

A seguir é apresentada uma descrição sucinta dos principais métodos de ordenação propostos na literatura e investigados neste trabalho para ranquear as tensões dos capacitores dos SM.

# A. Método da Bolha

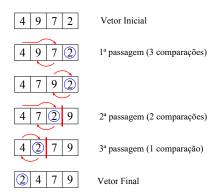

Para ordenar um vetor com n posições, o método da bolha percorre o vetor (n-1) vezes. Em cada passo, os elementos adjacentes são comparados e trocados se necessário. Na Figura 5 é mostrado um exemplo da ordenação de um vetor de quatro posições utilizando o método da bolha.

Fig. 5. Ordenação de um vetor de 4 posições através do método da bolha.

Note que após percorrer o vetor pela primeira vez, o maior elemento da sequência é movido para a última posição. No geral, após percorrer o vetor k vezes, as últimas k posições do vetor estarão ordenadas e não precisarão mais ser considerados.

O tempo de execução deste método no melhor caso é semelhante ao ideal, ou seja, proporcional a n. Por outro lado, no pior caso, o tempo é proporcional a  $n^2$ .

#### B. Método da Inserção

O método da inserção é frequentemente usado para colocar em ordem um baralho de cartas. O seu desempenho, tanto no melhor caso quanto no pior caso é semelhante ao método da bolha [11].

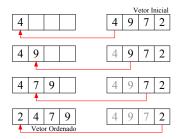

As iterações começam com o segundo elemento sendo comparado com o primeiro e trocando de posição se for menor. Nas iterações seguintes o elemento a ser inserido é comparado com o da esquerda e troca de posição enquanto for menor, quando o da esquerda for menor passa-se pra próxima iteração. Na Figura 6 é ilustrado um exemplo da ordenação de um vetor de quatro posições através da utilização deste método.

Fig. 6. Ordenação de um vetor de 4 posições através do método da inserção.

# C. Método da Seleção

O método da seleção é baseado na ideia de escolher o menor elemento do vetor, depois o segundo menor, e assim por diante [11]. Apesar disso, o método não apresenta bom desempenho. Tanto no melhor caso quanto no pior, os tempos de ordenação são semelhantes e proporcionais a  $n^2$ . A Figura 7 ilustra a ordenação de um vetor de quatro posições utilizando o método da seleção.

Fig. 7. Ordenação de um vetor de 4 posições através do método da seleção.

#### D. Método Shell

O método *shell* pode ser visto como uma variação eficiente do método da inserção [11]. Os tempos de execução são proporcionais a n.log(n) e  $n.log^2(n)$  no melhor e o pior caso, respectivamente, evidenciando a melhora no desempenho.

Enquanto a inserção compara apenas elementos adjacentes, o Shell permite comparar elementos separados por uma distância h. Essa distância h deve seguir uma sequência decrescente que termina em 1, de forma que para h=1 o algoritmo será equivalente ao da inserção. Um exemplo de

sequência é dado a seguir:

$$h(n) = \begin{cases} 3h(n-1) + 1, & n = 2, 3, 4, \dots \\ 1, & n = 1. \end{cases}$$

(2)

Note que se o último elemento do vetor for o menor, com o método da inserção serão necessárias (n-1) trocas para inseri-lo na primeira posição. O método Shell contorna esse problema comparando elementos distantes.

#### E. Método da Fusão (Merge)

Este método divide um vetor em dois subvetores de tamanhos similares para ordená-los e em seguida fundi-los [11]. Para melhorar o desempenho do método é possível dividir os subvetores sucessivamente até um certo tamanho antes de iniciar o processo de ordenação. O tempo de execução deste método tanto no melhor quanto no pior caso é proporcional a n.log(n). Na Figura 8 é ilustrado um exemplo gráfico do método da fusão aplicado a um vetor de seis posições.

Fig. 8. Ordenação de um vetor de 6 posições através do método da fusão.

#### F. Método Quick

Este método se difere do método da fusão na forma de dividir do vetor a ser ordenado. Enquanto o método da fusão divide o vetor ao meio e ordena os subvetores antes de unilos novamente, o método *quick* escolhe um elemento chamado pivô e passa os elementos menores que ele para esquerda e os maiores para a direita, depois ordena esses dois subvetores. Dessa forma é necessário apenas unir os dois subvetores já que os elementos da esquerda são menores que os da direita.

A escolha do pivô pode afetar o desempenho deste método sendo o tempo de execução no melhor caso semelhante ao do método anterior, contudo, no pior caso o tempo de execução pode ser  $n^2$ .

#### IV. DESCRIÇÃO DO SISTEMA CHIL

Conforme mencionado anteriormente, o desempenho dos métodos de ordenação é diretamente dependente do número de SM e da forma como as tensões dos capacitores estão desbalanceadas. Devido ao fato de que o comportamento destas tensões se altera com o tempo, quantificar a eficiência dos métodos de ordenação descritos na Seção III. não é tarefa simples.

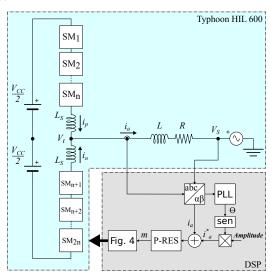

Assim, para avaliar o desempenho dos métodos de ordenação, foi planejado uma aplicação típica do MMC em um sistema *control-hardware-in-the-loop* conforme ilustrado na Figura 9. O circuito de potência formado pelo MMC

conectado a rede elétrica foi modelado no simulador em tempo real (Typhoon HIL 600). Os sinais de tensão e corrente provenientes do Typhoon foram condicionados antes de serem processados pelo DSP TMS320F28335, onde foi implementado o sistema de controle em malha fechada. Devido a limitação da quantidade de portas para comunicação entre o Typhoon e o DSP, foi modelado apenas uma fase do MMC.

Fig. 9. Diagrama de blocos do sistema control-hardware-in-the-loop.

Idealmente, o MMC foi projetado para operar como uma fonte de corrente controlada, a qual sintetiza uma corrente senoidal em fase com a tensão da rede. O sincronismo entre a corrente  $i_a(t)$  e a tensão  $v_s(t)$  é garantido pelo circuito de PLL, implementado no sistema de coordenadas  $\alpha\beta$  modificado [25].

O controlador de corrente utilizado neste estudo foi o proporcional ressonante (P-RES) que garante que a corrente sintetizada rastreie um sinal de referência senoidal com erro nulo em módulo e fase e cuja função de transferência é mostrada a seguir [26]:

$$G(s) = k_p + \frac{2k_i\omega_c s}{s^2 + 2\omega_c s + \omega_0^2}$$

(3)

onde  $k_p$  e  $k_i$  são os ganhos proporcional e integral respectivamente,  $\omega_c$  é a frequência de corte e  $\omega_0 = (2\pi f_0)$  é a frequência de ressonância do controlador, sendo  $f_0 = 60$  Hz.

Na Tabela II são fornecidos os parâmetros usados no projeto do sistema experimental. A frequência de amostragem foi escolhida dez vezes maior do que a frequência das portadoras triangulares. Tal fato se justifica pela necessidade de amostrar o sinal representado na Figura 2(b), cujo espectro apresenta componentes de frequência maior do que 1,8 kHz. Na Tabela III são dados os ganhos do controlador P-RES.

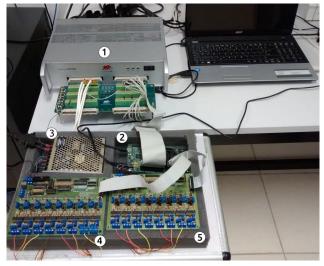

Na Figura 10 é mostrada uma fotografia do sistema *control-hardware-in-the-loop* usado para a obtenção dos resultados experimentais.

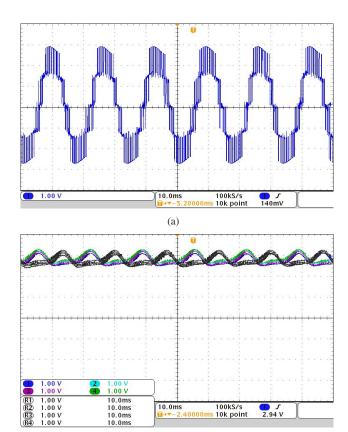

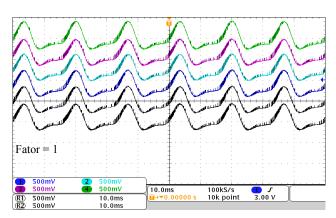

Nas Figuras 11 (a) e (b) são mostradas as formas de onda da tensão terminal do MMC, com cinco níveis, e as tensões nos capacitores dos oito submódulos, dos polos positivo e negativo, respectivamente. Esses resultados são referentes a

TABELA II Parâmetros do Sistema

| Parâmetro                                  | Valor   |

|--------------------------------------------|---------|

| Tensão eficaz de fase da rede $(V_S)$      | 127 V   |

| Tensão do barramento CC (V <sub>CC</sub> ) | 600 V   |

| Nº de SM por polo (n)                      | 4 e 6   |

| Tensão nominal dos capacitores ( $V_C$ )   | 100 V   |

| Indutância série (L)                       | 6 mH    |

| Resistência série (R)                      | 0,5 Ω   |

| Indutância do polo $(L_S)$                 | 2 mH    |

| Capacitância do SM (C)                     | 3300 μF |

| Passo de simulação no Typhoon              | 1 μs    |

| Frequência de amostragem $(f_s)$           | 18 kHz  |

| Frequência da portadora PWM $(f_{sw})$     | 1,8 kHz |

## TABELA III Controlador P-RES

| Parâmetro                          | Valor          |

|------------------------------------|----------------|

| Ganho proporcional $(k_p)$         | 40 V/A         |

| Ganho integral $(k_i)$             | 300 V/As       |

| Frequência de corte ( $\omega_c$ ) | $2\pi/3$ rad/s |

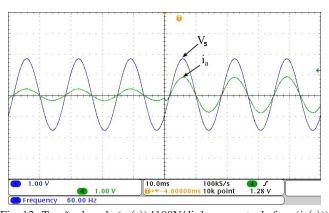

utilização do método da bolha para ordenação das tensões dos capacitores. É importante mencionar que não se observou diferença dinâmica no comportamento das tensões CC quando os diferentes métodos de ordenação foram utilizados. Na Figura 12 são mostradas as formas de onda da tensão CA da rede e da corrente do MMC. A corrente sintetizada pelo conversor é submetida a uma variação em degrau de 16 A para 36 A para demonstrar o funcionamento da malha de controle com o controlador proporcional-ressonante de corrente.

Fig. 10. Sistema *control-hardware-in-the-loop*: 1-Typhoon, 2-DSP, 3-fonte de tensão, 4 e 5-circuitos de condicionamento de sinais.

## V. DESEMPENHO DOS ALGORITMOS DE ORDENAÇÃO INVESTIGADOS

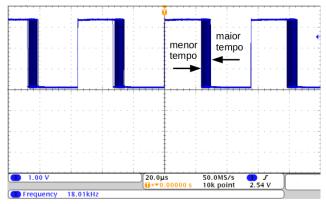

Com objetivo de investigar o esforço computacional de cada método de ordenação, foi medido o tempo que o DSP leva para executar cada um dos algoritmos de ordenação apresentados na Secão III.

No início do algoritmo de ordenação é ajustado o nível lógico alto em uma saída digital do DSP. Essa mesma saída sofre um *reset* ao final da rotina, permanecendo o nível lógico

Fig. 11. (a) Tensão terminal do MMC [100V/div]. (b) Tensões nos capacitores dos oito submódulos nos polos positivo e negativo [50V/div].

(b)

Fig. 12. Tensão da rede  $(v_s(t))$  [100V/div] e corrente de fase  $(i_a(t))$ ) [40A/div] sintetizada pelo controlador P-RES.

baixo o resto do período. Na Figura 13 é ilustrado o sinal usado para medir o tempo de execução das rotinas. Na borda de descida é observada uma sobreposição de imagens. O objetivo é evidenciar a diferença no tempo de execução do algoritmo de ordenação provocado pelo desbalanceamento das tensões dos capacitores.

Os tempos de execução dos algoritmos de ordenação em um MMC com quatro submódulos por polo são apresentados na Tabela IV. Nesta tabela estão representadas quatro situações: os menores e os maiores tempos de execução dos algoritmos de ordenação e os menores e maiores tempos de execução do algoritmo de controle completo, ou seja, está sendo levado em

consideração os tempos de execução do PLL, do controlador de corrente, da escolha dos submódulos e do *setup* das portas de saída do DSP, além do próprio algoritmo de ordenação. Na Tabela V são apresentados os tempos de processamento obtidos para um MMC com seis submódulos por polo.

Fig. 13. Medição de tempo de execução do algoritmo de ordenação.

# TABELA IV Tempos de Execução com 4 SM

| Método   | Alg. de Ordenação |          | Algoritmo Completo |          |

|----------|-------------------|----------|--------------------|----------|

| Metodo   | Menor             | Maior    | Menor              | Maior    |

| Bolha    | 7,22 μs           | 10,88 μs | 22,92 μs           | 30,32 μs |

| Inserção | 5,90 μs           | 9,70 μs  | 22,52 μs           | 29,32 μs |

| Seleção  | 9,50 μs           | 9,60 μs  | 26,52 μs           | 29,12 μs |

| Shell    | 27,10 μs          | 33,20 μs | 43,72 μs           | 52,52 μs |

| Fusão    | 13,20 μs          | 16,50 μs | 30,12 μs           | 36,12 μs |

| Quick    | 15,10 μs          | 19,40 μs | 32,12 μs           | 38,92 μs |

TABELA V Tempos de Execução com 6 SM

| Método   | Alg. de C | rdenação        | Algoritmo Completo |                 |  |

|----------|-----------|-----------------|--------------------|-----------------|--|

|          | Menor     | Maior           | Menor              | Maior           |  |

| Bolha    | 21,40 μs  | 24,40 μs        | 44,12 μs           | 47,92 μs        |  |

| Inserção | 12,20 μs  | $22,10 \ \mu s$ | 34,92 μs           | 45,72 μs        |  |

| Seleção  | 20,40 μs  | $25,00 \ \mu s$ | 43,92 μs           | 47,92 μs        |  |

| Shell    | 49,20 μs  | 56,40 μs        | 72,12 μs           | $80,00 \ \mu s$ |  |

| Fusão    | 23,20 μs  | $27,00 \ \mu s$ | 45,72 μs           | 51,92 μs        |  |

| Quick    | 23,20 μs  | 27,00 μs        | 45,10 μs           | 50,52 μs        |  |

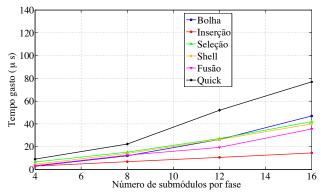

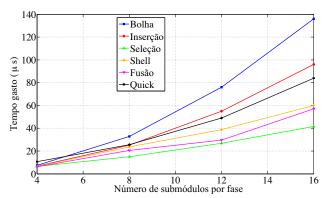

Em comparação com a Tabela IV, o pequeno aumento no número de submódulos foi suficiente para alterar o desempenho dos métodos de ordenação. Os gráficos ilustrados nas Figuras 14 e 15 evidenciam esta tendência para uma maior quantidade de submódulos. Estes gráficos foram obtidos supondo o vetor de tensões já ordenado (melhor caso) e inversamente ordenado (pior caso) para estabelecer os limites máximos e mínimos de cada método.

Na Tabela V, verifica-se que o método *shell* extrapolou o período de amostragem, ajustado em  $55,5~\mu s$ . Contudo, não se observou distorções nas tensões dos capacitores ou na tensão terminal do MMC. Este fato pode ser justificado levando em consideração a implementação do algoritmo ter sido feita dentro de uma rotina de interrupção. Enquanto a execução do código não finalizar, o próximo período de amostragem não ocorre. O efeito prático é equivalente a redução pela metade da frequência de execução do algoritmo de ordenação.

Dado o comportamento observado no método *shell*, experimentou-se executar o algoritmo de ordenação com uma

Fig. 14. Desempenho dos métodos de ordenação com o vetor ordenado (melhor caso).

Fig. 15. Desempenho dos métodos de ordenação com o vetor inversamente ordenado (pior caso).

frequência menor do que a frequência de amostragem, que no caso é igual a 18 kHz (Tabela II). O objetivo foi verificar se essa redução tinha algum efeito sobre as tensões CC e sobre a tensão terminal do MMC.

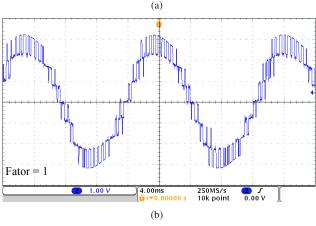

Na Figura 16 (a) são mostradas as formas de onda das tensões CC dos seis SM do polo positivo do MMC. As curvas estão deslocadas em relação ao eixo horizontal para melhor visualização do perfil das tensões CC. Já na Figura 16 (b) é mostrada a tensão terminal com sete níveis. Este resultado foi obtido para o caso em que o algoritmo de ordenação é executado de maneira síncrona, ou seja, na mesma frequência de amostragem.

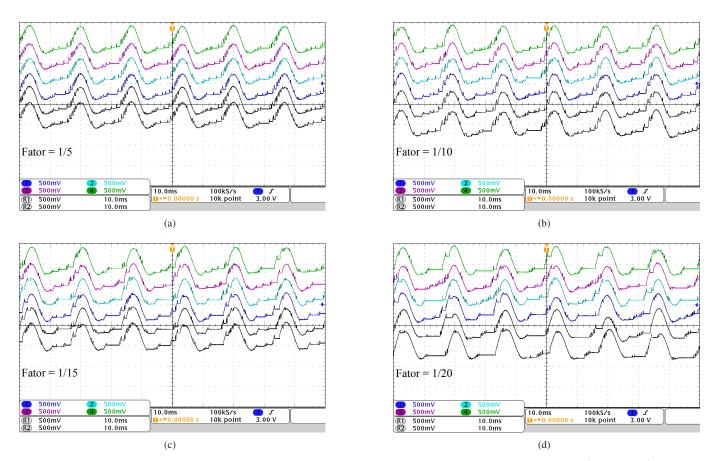

Nas Figuras 17 (a), (b), (c) e (d) são mostradas as formas de onda das tensões CC dos SM do polo positivo à medida que a frequência de execução do algoritmo de ordenação é reduzida em relação a frequência de amostragem de um fator de  $\frac{1}{5}$ ,  $\frac{1}{10}$ ,  $\frac{1}{15}$  e  $\frac{1}{20}$ , respectivamente. Apesar do esforço computacional do algoritmo de ordenação diminuir com a redução da frequência de execução, a análise das formas de onda da Figura 17 mostra que as tensões dos SM começam a se deteriorar para fatores de atualização menores que  $\frac{1}{15}$ .

Outro aspecto relacionado a redução da frequência de execução do algoritmo de ordenação é a redução do número de comutações dos interruptores dos SM. Neste caso, a determinação das maiores e menores tensões CC não são realizadas a todo período de amostragem. Consequentemente, não há trocas sucessivas entre SM ativos e inativos dos polos positivo e negativo.

Na Tabela VI é mostrada a distorção harmônica total

(THD) da tensão terminal do MMC para cada um dos casos anteriores. Esses índices foram calculados considerando até o harmônico de tensão de ordem 150. Conclui-se que a redução da frequência de execução do algoritmo de ordenação não afeta de maneira significativa a tensão terminal. Ressalta-se que os resultados da Tabela VI foram obtidos para o método *shell*, porém este comportamento se repete quando os outros métodos de ordenação são usados.

TABELA VI Efeito da Redução na Frequência de Execução do Método Shell Sobre a THD para 6 SM

| Distorção Harmônica Total |        |               |                |                |                |

|---------------------------|--------|---------------|----------------|----------------|----------------|

| Fator                     | 1      | $\frac{1}{5}$ | $\frac{1}{10}$ | $\frac{1}{15}$ | $\frac{1}{20}$ |

| THD                       | 18,69% | 18,50%        | 18,16%         | 18,97%         | 17,94%         |

Fig. 16. (a) Tensões dos capacitores dos SM do polo positivo [20V/div], (b) tensão terminal de saída para n = 6 [100V/div].

#### VI. RESULTADOS EXPERIMENTAIS

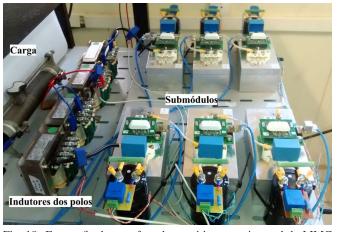

Com objetivo de demonstrar a importância da simulação CHIL, o DSP com os algoritmos de equalização testados na plataforma Typhoon HIL foi conectado a um protótipo em pequena escala de conversor MMC formado por seis módulos SEMiX202GB066HDs da Semikron. Na Figura 18 é mostrada uma fotografia de uma fase do conversor MMC construído em laboratório. Na Tabela VII são fornecidos os parâmetros do protótipo.

Assim como na simulação CHIL, os sinais de tensão e corrente provenientes do protótipo foram condicionados antes

Fig. 17. Efeito da redução da frequência de execução do algoritmo de ordenação sobre a tensão CC dos SM: (a) fator  $\frac{1}{5}$ , (b) fator  $\frac{1}{10}$ , (c) fator  $\frac{1}{15}$ , (d) fator  $\frac{1}{20}$  (escalas verticais: 20V/div).

Fig. 18. Fotografia de uma fase do protótipo experimental do MMC construído em laboratório.

de serem processados pelo DSP, onde foi implementado todo o sistema de controle do MMC.

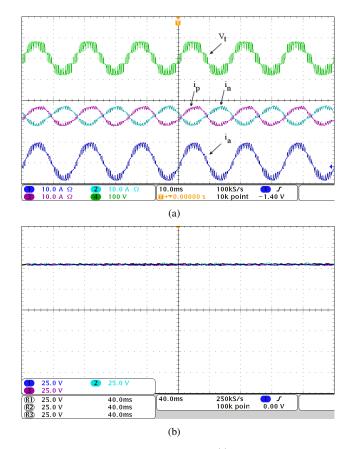

Nas Figuras 19 (a) e (b) são mostradas respectivamente as formas de onda da tensão terminal, das correntes nos polos positivo e negativo, da corrente de saída do MMC e das tensões nos capacitores dos seis submódulos para o conversor alimentando uma carga RL de  $17\Omega$  e 5mH. Foi utilizado o método da seleção para ordenar as tensões dos capacitores do MMC. É importante mencionar que não se observou diferença no comportamento das tensões CC do

# TABELA VII Protótipo Experimental

| Parâmetro                                  | Valor   |

|--------------------------------------------|---------|

| Tensão do barramento CC (V <sub>CC</sub> ) | 170 V   |

| Nº de SM por polo (n)                      | 3       |

| Indutância do polo $(L_S)$                 | 2 mH    |

| Capacitância do SM (C)                     | 3300 μF |

| Índice de modulação de amplitude ( $M_a$ ) | 0,85    |

| Frequência da portadora PWM $(f_{sw})$     | 1,8 kHz |

| Frequência de amostragem $(f_s)$           | 18 kHz  |

protótipo quando comparado com os resultados da simulação CHIL.

# VII. CONCLUSÕES

Neste artigo foram avaliados os desempenhos de alguns métodos de ordenação usados para equalizar as tensões dos SM de um MMC. Os resultados foram obtidos a partir de simulação em tempo real o que os torna mais confiáveis se comparados a outros estudos que se baseiam em distribuição aleatória dos dados para representar o desequilíbrio das tensões.

A análise das Tabelas IV e V permite concluir que os métodos da inserção, bolha e seleção apresentaram, no geral, os menores tempos de execução para um número de SM iguais a n=4 e n=6, respectivamente. Contudo, para uma quantidade maior de submódulos o método da bolha

Fig. 19. (a) Tensão terminal do MMC  $(v_t(t))$  [100V/div]; correntes nos polos positivo  $(i_p(t))$  e negativo  $(i_n(t))$  [10A/div]; e corrente da carga  $(i_a(t))$  [10A/div]. (b) Tensões nos capacitores dos submódulos nos polos positivo e negativo [25V/div].

perde a eficiência. Considerando o melhor caso, o método da inserção apresentou o menor tempo de processamento porque o vetor não realiza nenhuma troca de posição. Com o vetor inversamente ordenado (pior caso), o método da seleção foi o que apresentou o menor tempo de processamento porque realiza apenas uma troca a cada vez que percorre o vetor. Assim sendo, de uma maneira geral os métodos de ordenação da seleção, fusão e shell seriam os mais adequados para aplicação em conversores MMC com um grande número de SM. Esta afirmação é justificada pela observação das curvas mostradas nas Figuras 14 e 15.

O estudo também investigou o efeito da redução da frequência de execução do algoritmo de ordenação. A análise da Tabela VI e das Figuras 16 e 17 permite concluir que a redução na frequência de execução dos algoritmos não afetou significativamente a regulação das tensões CC dos capacitores dos SM e nem a THD da tensão terminal do MMC.

Por fim, o DSP com os algoritmos testados na plaforma em tempo real foi usado para controlar um protótipo de pequena escala construído em laboratório. Os resultados apresentados neste estudo demonstram a importância da simulação em tempo real de conversores eletrônicos destinados a aplicações em média e alta tensão.

#### **AGRADECIMENTOS**

Os autores gostariam de agradecer o CNPq (Proc. 456040/2014-5), a FAPEMIG (Proc. APQ-01046-15), a UFJF

e ao IF Sudeste MG pelo apoio financeiro e bolsas para o desenvolvimento desta pesquisa, bem como a empresa Ohmini pela cessão do equipamento Typhoon HIL 600.

#### REFERÊNCIAS

- [1] A. Lesnicar, R. Marquardt, "An innovative modular multilevel converter topology suitable for a wide power range", *in Proceedings of Power Tech Conference*, vol. 3, pp. 6–12, 2003.

- [2] M. Glinka, "Prototype of multiphase modular-multilevel-converter with 2 MW power rating and 17-level-output-voltage", in Proceedings of Power Electronics Specialists Conference, vol. 4, pp. 2572–2576, 2004.

- [3] F. Deng, Z. Chen, "A Control Method for Voltage Balancing in Modular Multilevel Converters", *IEEE Transactions on Power Electronics*, vol. 29, no. 1, pp. 66–76, Jan. 2014.

- [4] M. Hagiwara, H. Akagi, "Control and Experiment of Pulsewidth-Modulated Modular Multilevel Converters", *IEEE Transactions on Power Electronics*, vol. 24, no. 7, pp. 1737–1746, July 2009.

- [5] A. A. Elserougi, A. M. Massoud, S. Ahmed, "A Switched-Capacitor Submodule for Modular Multilevel HVDC Converters With DC-Fault Blocking Capability and a Reduced Number of Sensors", *IEEE Transactions on Power Delivery*, vol. 31, no. 1, pp. 313–322, Feb. 2016.

- [6] R. Picas, J. Zaragoza, J. Pou, S. Ceballos, J. Balcells, "New Measuring Technique for Reducing the Number of Voltage Sensors in Modular Multilevel Converters", *IEEE Transactions on Power Electronics*, vol. 31, no. 1, pp. 177–187, Jan. 2016.

- [7] G. S. da Silva, R. P. Vieira, C. Rech, "Modified sliding-mode observer of capacitor voltages in Modular Multilevel Converter", in 13th Brazilian Power Electronics Conference and 1st Southern Power Electronics Conference (COBEP/SPEC), pp. 1–6, 2015.

- [8] M. Saeedifard, R. Iravani, "Dynamic performance of a modular multilevel back-to-back HVDC system", *IEEE Transactions on Power Delivery*, vol. 25, no. 4, pp. 2903–2912, Oct. 2010.

- [9] S. Debnath, J. Qin, B. Bahrani, M. Saeedifard, P. Barbosa, "Operation, Control, and Applications of the Modular Multilevel Converter: A Review", *IEEE Transactions on Power Electronics*, vol. 30, no. 1, pp. 37–53, Jan. 2015.

- [10] S. Rohner, S. Bernet, M. Hiller, R. Sommer, "Modulation, Losses, and Semiconductor Requirements of Modular Multilevel Converters", *IEEE Transactions on Industrial Electronics*, vol. 57, no. 8, pp. 2633–2642, Aug. 2010.

- [11] G. Barnett, L. Del Tongo, *Data Structures and Algorithms: Annotated Reference with Examples*, NETSlackers, 2008.

- [12] D. Siemaszko, "Fast Sorting Method for Balancing Capacitor Voltages in Modular Multilevel Converters",

- *IEEE Transactions on Power Electronics*, vol. 30, no. 1, pp. 463–470, Jan. 2015.

- [13] F. Zhao, G. Xiao, Z. Song, C. Peng, "Insertion sort correction of two-way merge sort algorithm for balancing capacitor voltages in MMC with reduced computational load", in 8th International Power Electronics and Motion Control Conference, pp. 748– 753, 2016.

- [14] H. Vardhan, B. Akin, H. Jin, "A Low-Cost, High-Fidelity Processor-in-the Loop Platform: For Rapid Prototyping of Power Electronics Circuits and Motor Drives", *IEEE Power Electronics Magazine*, vol. 3, no. 2, pp. 18–28, June 2016.

- [15] H. Abu-Rub, S. Bayhan, S. Moinoddin, M. Malinowski, J. Guzinski, "Medium-Voltage Drives: Challenges and existing technology", *IEEE Power Electronics Magazine*, vol. 3, no. 2, pp. 29–41, June 2016.

- [16] N. Thitichaiworakorn, M. Hagiwara, H. Akagi, "Experimental Verification of a Modular Multilevel Cascade Inverter Based on Double-Star Bridge Cells", *IEEE Transactions on Industry Applications*, vol. 50, no. 1, pp. 509–519, Jan. 2014.

- [17] N. Ahmed, L. Ängquist, A. Antonopoulos, L. Harnefors, S. Norrga, H.-P. Nee, "Performance of the modular multilevel converter with redundant submodules", in *Proceedings of 41st Annual Conference of the IEEE Industrial Electronics Society*, pp. 3922–3927, 2015.

- [18] E. Solas, G. Abad, J. A. Barrena, S. Aurtenetxea, A. Cárcar, L. Zajac, "Modular Multilevel Converter With Different Submodule Concepts—Part I: Capacitor Voltage Balancing Method", *IEEE Transactions on Industrial Electronics*, vol. 60, no. 10, pp. 4525–4535, Oct. 2013.

- [19] E. Solas, G. Abad, J. A. Barrena, S. Aurtenetxea, A. Cárcar, L. Zajac, "Modular Multilevel Converter With Different Submodule Concepts-Part II: Experimental Validation and Comparison for HVDC Application", *IEEE Transactions on Industrial Electronics*, vol. 60, no. 10, pp. 4536–4545, Oct. 2013.

- [20] R. Marquardt, "Modular Multilevel Converter: An universal concept for HVDC-Networks and extended DC-Bus-applications", in Proceedings of International Power Electronics Conference, pp. 502–507, 2010.

- [21] G. S. Konstantinou, V. G. Agelidis, "Performance evaluation of half-bridge cascaded multilevel converters operated with multicarrier sinusoidal PWM techniques", in 4th IEEE Conference on Industrial Electronics and Applications, pp. 3399–3404, 2009.

- [22] M. Rejas, L. Mathe, P. D. Burlacu, H. Pereira, A. Sangwongwanich, M. Bongiorno, R. Teodorescu, "Performance comparison of phase shifted PWM and sorting method for modular multilevel converters", in Proceedings of 17th European Conference on Power Electronics and Applications, pp. 1–10, 2015.

- [23] Z. Li, P. Wang, H. Zhu, Z. Chu, Y. Li, "An Improved Pulse Width Modulation Method for Chopper-Cell-Based Modular Multilevel Converters", *IEEE Transactions on Power Electronics*, vol. 27, no. 8, pp. 3472–3481, Aug. 2012.

- [24] G. S. da Silva, R. C. Beltrame, L. Schuch, C. Rech, "Hybrid AC Power Source Based on Modular Multilevel Converter and Linear Amplifier", *IEEE Transactions on Power Electronics*, vol. 30, no. 1, pp. 216–226, Jan. 2015.

- [25] P. C. S. Furtado, M. C. B. P. Rodrigues, H. A. C. Braga, P. G. Barbosa, "Two-phase three-wire shunt active power filter control by using the single-phase pq theory", *Eletrônica de Potência*, vol. 19, no. 3, pp. 303–311, Aug. 2014.

- [26] D. N. Zmood, D. G. Holmes, "Stationary frame current regulation of PWM inverters with zero steady-state error", *IEEE Transactions on Power Electronics*, vol. 18, no. 3, pp. 814–822, May 2003.

#### DADOS BIOGRÁFICOS

<u>Frederico Toledo Ghetti</u> recebeu os títulos de engenheiro e mestre em Engenharia Elétrica pela Universidade Federal de Juiz de Fora em 2007 e 2009, respectivamente, onde atualmente cursa o doutorado.

Andrei de Oliveira Almeida recebeu os títulos de bacharel em ciências e de engenheiro eletricista pela Universidade Federal de Juiz de Fora em 2015 e 2016, respectivamente, onde atualmente ele cursa o mestrado.

<u>Pedro Machado de Almeida</u> recebeu os títulos de engenheiro, mestre e doutor em Engenharia Elétrica pela Universidade Federal de Juiz de Fora em 2009, 2011 e 2013, respectivamente.

Pedro Gomes Barbosa recebeu o título de Engenheiro Eletricista pela Universidade Federal de Juiz de Fora em 1986 e os títulos de mestre e doutor, em Engenharia Elétrica, pela Universidade Federal do Rio de Janeiro em 1994 e 2000, respectivamente.