# A SINGLE-PHASE HYBRID SWITCHED-CAPACITOR INVERTER FOR HIGH STEP-DOWN APPLICATIONS

Rodrigo de S. Santos<sup>1</sup>, Telles B. Lazzarin<sup>1</sup>, Ivo Barbi<sup>2</sup>

<sup>1</sup>INEP/PGEEL - <sup>2</sup>DAS/PGEEL - Federal University of Santa Catarina (UFSC), Florianópolis – SC, Brazil e-mail: rodrigosouza@inep.ufsc.br, telles@inep.ufsc.br, ivobarbi@gmail.com

Abstract – In this paper, a novel single-phase inverter topology is proposed, which was derived from the integration of the conventional voltage source inverter with switched-capacitor dc-dc converters. The inverter circuit can provide a low ac output voltage from a high dc input voltage, using low-voltage devices (switches and capacitors). The modulation scheme is the same employed in conventional inverters and the capacitor voltages are self-balanced. The proposed topology is suitable for applications with high conversion ratios. A 2.5 kW prototype (800 V/220 V), which achieved a peak efficiency of 97.8%, was built to show the feasibility of the novel inverter.

*Keywords* – High Step-Down Applications, Hybrid Switched-Capacitor, Inverter, Pulse Width Modulated Inverters, Switched-Capacitor.

# I. INTRODUCTION

In single-phase non-isolated applications, voltage source inverters (VSI) are the topologies most commonly used in dc-ac conversion, an example being the full-bridge (FB) inverter [1], which can only synthesize an output voltage lower than the input voltage. However, when the difference between the input and output voltages is high (i.e., high step-down conversion ratio), FB inverter will operate with low performance due to the high voltage stress on the semiconductors. Furthermore, it will operate with a lower modulation index, resulting in a poor switch utilization ratio [2] and an increase in the output voltage total harmonic distortion (THD).

Multilevel converters, such as the neutral point clamped (NPC) inverter [3], reduce the voltage stress on the semiconductors. However, additional control loops are required for the capacitor voltage balancing [4], which increases the costs (due to voltage sensors) and becomes a potential cause of failures at voltage imbalance conditions [5].

Two-stage conversion architectures consisting of a frontend step-down dc-dc converter with a back-end topology can also be employed in high step-down specifications, such as dc-dc topologies for power supply applications [6]. However, multiple-stage solutions can present a high component count, high control complexity and low efficiency, because all of the energy is processed more than once [7]. These architectures [6], [7] use a front-end switched-capacitor (SC) dc-dc converter, which presents a high conversion ratio, low semiconductor voltage stresses and suitability for integrated

Manuscript received 17/02/2017; first revision 30/04/2017; accepted for publication 21/06/2017, by recommendation of Editor Marcelo Cabral Cavalcanti.

circuits implementation. In contrast, SC converters cannot regulate the output voltage with high efficiency [6].

To provide a solution for the aforementioned issues, a single-stage single-phase high step-down hybrid switched-capacitor (HSC) inverter is proposed. The novel topology was generated through the integration of dc-dc SC converters with the FB inverter, hence the term 'hybrid'. Consequently, the advantages of SC converters can be exploited in dc-ac conversion and their drawbacks can be reduced or even eliminated.

Several HSC topologies have been proposed in low power dc-dc [8], [9], ac-dc [10] and dc-ac [11]–[15] conversion. Except for [11], [12], these inverters are not suitable for step-down applications, because they use the SC circuit to generate a multilevel staircase waveform.

Some similar topologies have been proposed as isolated high-frequency inverters for low power dc-dc conversion [7], [8], [16]. However, the inverter proposed in this paper was developed to be applied at higher power levels, for application in, for instance, grid-connected inverters for renewable systems, interruptible power supplies, ac drives, interfaces between high voltage dc and low voltage ac grids and, auxiliary power supplies. Moreover, rather than use a fixed duty-cycle as in [8], the proposed inverter employs a sinusoidal pulse width modulation (SPWM), as reported herein.

The aim of this study was to investigate and evaluate the proposed inverter performance. A detailed study, design issues, comparative analysis, and experimental results are reported herein.

# II. PROPOSED TOPOLOGY

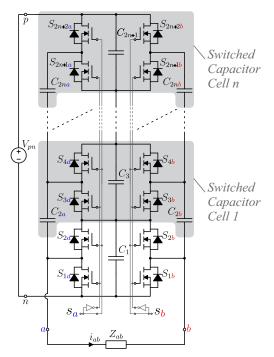

A generalized version of the proposed topology, named the full-bridge hybrid switched-capacitor (FBHSC) inverter, can be seen in Figure 1. A half-bridge version was proposed in [12]. The FBHSC is composed of 'n' SC cells  $(n \in \mathbb{N}_{\geq 1})$ , and controls the power flow between the dc input voltage  $V_{pn}$  and an ac load. Table I shows the FBHSC component count.

Regardless of the number of SC cells, all switching states

TABLE I Component Count for the FBHSC Generalized Version

| Description                                         | Value*     |

|-----------------------------------------------------|------------|

| Power Switches                                      | 4(n+1)     |

| Floating Capacitors<br>(Capacitors with even index) | 2 <i>n</i> |

| Link Capacitors<br>(Capacitors with odd index)      | n+1        |

n is the number of SC cells.

Fig. 1. Proposed single-phase inverter: generalized version with 'n' SC cells.

can be defined by only two switching functions:  $s_a$  (for leg 'a') and  $s_b$  (for leg 'b') as follows

$$s_k = \begin{cases} 1, & \text{if } S_{xk} \text{ on and } S_{yk} \text{ off} \\ 0, & \text{if } S_{yk} \text{ on and } S_{xk} \text{ off} \end{cases}$$

(1)

where  $k \in \{a, b\}, x \in \{2, 4, 6 \dots 2n - 2\}$  and y = x - 1.

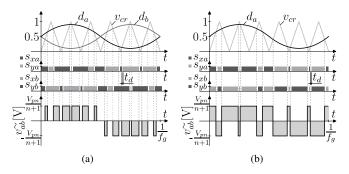

The FBHSC can operate with sinusoidal pulse width modulation (SPWM) with a symmetrical triangular carrier  $v_{cr}$ . Both unipolar (Figure 2(a)) and bipolar (Figure 2(b)) SPWM schemes can be employed. A dead time  $t_d$  between switches with subsequent index (e.g.,  $S_{1a}$  and  $S_{2a}$ ) is required to avoid a short circuit. As in FB inverters, the averaged switching functions  $d_a$  and  $d_b$  are given by

$$d_a = \langle s_a \rangle = 1 - d_b = 1 - \langle s_b \rangle = \frac{1}{2} + \frac{M}{2} \sin(\omega t)$$

(2)

where  $\omega = 2\pi f_g$  ( $f_g$  in Hertz), t is the time in seconds and M is the modulation index, which can vary from 0 to 1.

Fig. 2. (a) Unipolar and (b) bipolar SPWM schemes for the FBHSC inverter, where *x* is an odd index and *y* is an even index.

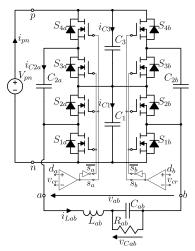

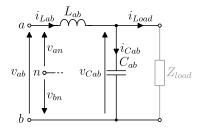

Fig. 3. FBHSC inverter with a single SC cell (n = 1).

Figure 2 also shows the expected output voltage  $v_{ab}^{\sim}$ , which is dependent on the input voltage  $V_{pn}$  and the number of SC cells n. However, for the sake of simplicity, the topology with one SC cell (shown in Figure 3) will be the focus of this paper. Moreover, the inverter operation of the proposed topology will be focused in this paper, even though the FBHSC can operate as a bidirectional rectifier, a reactive compensator or a active power filter.

#### III. THEORETICAL ANALYSIS

This section presents the theoretical analysis for the FBHSC (Figure 3). The analysis was performed, unless specified, under the following conditions:

- All components are considered ideal, except for the MOSFETs. These are represented by their on-state resistance while conducting  $(R_{DSon})$ . Without parasitic resistances, it is impossible to obtain the model [17];

- High-frequency ripple is neglected for all components;

- The current through the MOSFET, regardless of the direction, will always be conducted by the MOSFET channel instead of the body diode;

- The switching frequency  $f_{sw}$  is much higher than the output frequency  $f_g$ ;

- The low-frequency variables (e.g.,  $i_{Lab}$ ,  $v_{Cab}$ ) are assumed constant within the switching period  $T_{sw}$ ; and

- The proposed converter operates in the no-charge (NC) mode (see section IV).

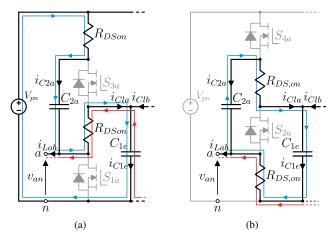

The topology presented in Figure 3 has two linearly dependent states:  $v_{C1}$  and  $v_{C3}$ . Thus, to obtain a system without redundant states, capacitors  $C_1$  and  $C_3$  will be replaced with an equivalent capacitor  $C_{1e}$ , as shown in Figure 4. The relations among these capacitors are defined by

$$\begin{cases}

C_{1e} = C_1 + C_3 \\

v_{C1e} = V_{pn} - v_{C3} = v_{C1} \\

\frac{i_{C1}}{C_1} = -\frac{i_{C3}}{C_3} \\

i_{C1e} = i_{C1} - i_{C3}

\end{cases}$$

(3)

Inverter legs can be analyzed separately. In leg 'a', the FBHSC operation can be described using two modes as follows:

Fig. 4. FBHSC switching states. (a)  $s_a = 1$ . (b)  $s_a = 0$ .

Mode 1 (Figure 4(a)): capacitor  $C_{1e}$  is connected to the output port  $v_{an}$  supplying the load while capacitor  $C_{2a}$  is connected between the voltage source  $V_{pn}$  and the capacitor  $C_{1e}$ . Assuming a positive output current  $i_{Lab}$ ,  $C_{2a}$  is charging and  $C_{1e}$  is discharging. This switching state, which has a duration of  $d_a T_{sw}$ , can be represented as

$$\begin{cases} i_{C2a} = & \frac{i_{Lab}R_{DSon} - v_{C1e} - v_{C2a} + V_{pn}}{2R_{DSon}} \\ i_{Cla} = & -\frac{i_{Lab}R_{DSon} + v_{C1e} + v_{C2a} - V_{pn}}{2R_{DSon}} \\ v_{an} = & \frac{\left(-i_{Lab}R_{DSon} + v_{C1e} - v_{C2a} + V_{pn}\right)}{2} \end{cases}, \ 0 < t < d_a T_{SW}. \tag{4}$$

Mode 2 (Figure 4(b)): inductor current  $i_{Lab}$  is in the freewheeling state through  $S_{1a}$ . The energy stored in  $C_{2a}$ , in the previous switching state, is transferred directly to  $C_{1e}$ . The instantaneous current through  $C_{1e}$  and  $C_{2a}$  is limited by  $R_{DSon}$ . This switching state, which has a duration of  $(1 - d_a)T_{sw}$ , can be represented as

$$\begin{cases} i_{C2a} = & \frac{i_{Lab}R_{DSon} + \nu_{C1e} - \nu_{C2a}}{2R_{DSon}} \\ i_{Cla} = & -\frac{i_{Lab}R_{DSon} + \nu_{C1e} - \nu_{C2a}}{2R_{DSon}} , d_aT_{sw} < t < T_{sw}. \end{cases}$$

$$v_{an} = & \frac{(-i_{Lab}R_{DSon} + \nu_{C1e} - \nu_{C2a})}{2}$$

The same procedure must be applied to leg 'b'. Furthermore, to obtain the complete system, it is necessary to include equations of the output filter (Figure 5), defined as

$$\begin{cases}

L_{ab} \frac{dv_{Lab}}{dt} = v_{an} - v_{bn} - v_{Cab} \\

C_{ab} \frac{di_{Cab}}{dt} = i_{Lab} - i_{Load}

\end{cases}$$

(6)

To attain a compact representation of the system, all equations will be written in state-space form [18], as follows

$$\dot{\mathbf{x}} = [\mathbf{A}_1 d_a + \mathbf{A}_2 (1 - d_a) + \mathbf{A}_3 d_b + \mathbf{A}_4 (1 - d_b) + \mathbf{F}] \mathbf{x} + [\mathbf{B}_1 d_a + \mathbf{B}_2 (1 - d_a) + \mathbf{B}_3 d_b + \mathbf{B}_4 (1 - d_b) + \mathbf{G}] \mathbf{u}$$

(7)

Fig. 5. LC output filter.

where the state and the input vectors  $(\mathbf{x} \text{ and } \mathbf{u})$  are

$$\mathbf{x} = \begin{bmatrix} \langle v_{C1e} \rangle & \langle v_{C2a} \rangle & \langle v_{C2b} \rangle & \langle i_{Lab} \rangle & \langle v_{Cab} \rangle \end{bmatrix}^{T} \mathbf{u} = \begin{bmatrix} V_{pn} & \langle i_{Load} \rangle \end{bmatrix}^{T}$$

(8)

In the state-space averaged model presented in (7),  $A_1$  is the matrix representation of (4). Likewise,  $A_2$  is the matrix representation of (5). Matrices  $A_3$  and  $A_4$  are the representations of equivalent leg 'b' switching states. Matrices F and F0 represent the output filter, presented in (6)0. All matrices are presented in the Appendix F1.

# A. Steady-State Analysis

All steady-state values ("-") can be found by setting all derivative terms to zero [19], as follows

$$0 = [\mathbf{A}_{1}d_{a} + \mathbf{A}_{2}(1 - d_{a}) + \mathbf{A}_{3}d_{b} + \mathbf{A}_{4}(1 - d_{b}) + \mathbf{F}]\bar{\mathbf{x}} + [\mathbf{B}_{1}d_{a} + \mathbf{B}_{2}(1 - d_{a}) + \mathbf{B}_{3}d_{b} + \mathbf{B}_{4}(1 - d_{b}) + \mathbf{G}]\bar{\mathbf{u}}$$

(9)

where the vectors  $\overline{\mathbf{x}}$  and  $\overline{\mathbf{u}}$  are given by

$$\overline{\mathbf{x}} = \left[ \begin{array}{cc} \overline{\langle \nu_{\text{C1e}} \rangle} & \overline{\langle \nu_{\text{C2a}} \rangle} & \overline{\langle \nu_{\text{C2b}} \rangle} & \overline{\langle i_{\text{Lab}} \rangle} & \overline{\langle \nu_{\text{Cab}} \rangle} \end{array} \right]^{T} \\

\overline{\mathbf{u}} = \left[ \begin{array}{cc} V_{pn} & \overline{\langle i_{Load} \rangle} \end{array} \right]^{T}$$

(10)

From (9) and performing algebraic manipulation, the steady-state values for all capacitor voltages can be found, as follows

$$\begin{cases}

\overline{\langle v_{C1e} \rangle} = \frac{V_{pn}}{2} - \frac{\overline{\langle i_{Load} \rangle} R_{DSon}}{2} \frac{d_a - d_b}{d_a (1 - d_a) + d_b (1 - d_b)} \\

\overline{\langle v_{C2a} \rangle} = \frac{V_{pn}}{2} - \frac{\overline{\langle i_{Load} \rangle} R_{DSon}}{2} \frac{d_a (2d_b - 1) + (2d_b - 3)d_b}{d_a (1 - d_a) + d_b (1 - d_b)} \\

\overline{\langle v_{C2b} \rangle} = \frac{V_{pn}}{2} - \frac{\overline{\langle i_{Load} \rangle} R_{DSon}}{2} \frac{d_a (3 - 2d_b) - 2d_a^2 + d_b}{d_a (1 - d_a) + d_b (1 - d_b)}

\end{cases} . (11)$$

All capacitor voltages have a constant value  $(V_{pn}/2)$  plus a term dependent on the output current  $i_{Load}$  and the MOSFET on-resistance  $R_{DSon}$ . Therefore, by neglecting  $R_{DSon}$ , all capacitor voltages are simplified to

$$\langle V_{C1e} \rangle \approx \langle V_{C1} \rangle \approx \langle V_{C3} \rangle \approx \langle V_{C2a} \rangle \approx \langle V_{C2b} \rangle \approx 0.5 V_{pn}.$$

(12)

From (12), all capacitor voltages are a half of the input voltage, regardless of the duty-cycle or output current, as in the regular SC converters. Moreover, all voltage across the semiconductors are also given by (12).

<sup>\*</sup>For the sake of simplicity and to avoid the average-value notation " $\langle \rangle$ ", the input voltage  $V_{pn}$  will be assumed constant (i.e.,  $\langle v_{pn} \rangle = V_{pn}$ ).

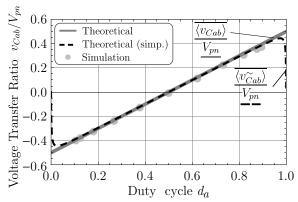

Fig. 6. FBHSC voltage transfer ratio as a function of the duty cycle: analytical model (full and simplified) and numerical simulation.

The steady-state value of the output voltage is given by

$$\overline{\langle v_{Cab}\rangle} = \frac{V_{pn}d_{ab}}{2} - \overline{\langle i_{Load}\rangle} r_{eq}$$

(13)

where  $d_{ab} = d_a - d_b$  and  $r_{eq}$  is defined by

$$r_{eq} = d_{ab}^{2} \underbrace{\frac{R_{DSon}}{2(d_{a}(1 - d_{a}) + d_{b}(1 - d_{b}))}}_{r_{eq,p}} + \underbrace{\frac{2R_{DSon}}{R_{eq,s}}}.$$

(14)

The equivalent resistance  $r_{eq}$  represents the total conduction loss and its evaluation can be useful to compare the FBHSC performance with other solutions. It can be divided into two terms:  $R_{eq,s}$  represents the losses of an equivalent FB inverter whereas  $r_{eq,p}$  represents the capacitor balancing losses.

Neglecting  $R_{DSon}$ , and recalling that  $d_b = 1 - d_a$ , the simplified output voltage can be defined as

$$\overline{\left\langle v_{Cab}^{\sim}\right\rangle} = \overline{\left\langle v_{Cab}\right\rangle}\Big|_{R_{DSon}=0} = \frac{V_{pn}(2d_a-1)}{2}.$$

(15)

Figure 6 shows the voltage transfer ratio of (13) and (15). For the non-simplified result, a resistive load (i.e.  $\overline{\langle i_{Load} \rangle} = \overline{\langle v_{Cab} \rangle / R_{ab} \rangle}$  was assumed. Also, a set of computational simulations performed in PSIM® was added to the results. All parameters used are shown in Table II.

The FBHSC voltage transfer ratio is almost linear, as shown in Figure 6. Simulation and theoretical results are in excellent agreement. Divergences between the complete and simplified results increase at the duty cycle extremes, where the converter rarely operates. Therefore, considering the whole duty cycle variation, the difference can be neglected. However, if a precise prediction of the output voltage is required (e.g., for deadbeat control), (13) can be used.

# B. Dynamic Analysis

To obtain the dynamic model, small-signal analysis will be performed. In the system presented in (7), a small ac perturbation ("^") is summed to the steady-state values, as follows:

$$\bar{\mathbf{x}} + \hat{\mathbf{x}} = \left[ \mathbf{A}_{1} (d_{a} + \hat{d}_{a}) + \mathbf{A}_{2} (1 - d_{a} - \hat{d}_{a}) + \mathbf{F} + \right. \\

\left. + \mathbf{A}_{3} (d_{b} + \hat{d}_{b}) + \mathbf{A}_{4} (1 - d_{b} - \hat{d}_{b}) \right] (\bar{\mathbf{x}} + \hat{\mathbf{x}}) + \\

\left[ \mathbf{B}_{1} (d_{a} + \hat{d}_{a}) + \mathbf{B}_{2} (1 - d_{a} - \hat{d}_{a}) + \right. \\

\left. + \mathbf{B}_{3} (d_{b} + \hat{d}_{b}) + \mathbf{B}_{4} (1 - d_{b} - \hat{d}_{b}) + \mathbf{G} \right] (\bar{\mathbf{u}} + \hat{\mathbf{u}}) \tag{16}$$

TABLE II Components Used in the Prototype and Main Specifications

| Description         | Symbol           | Value                                                         |  |  |  |

|---------------------|------------------|---------------------------------------------------------------|--|--|--|

| Input Voltage       | $V_{pn}$         | 800 V                                                         |  |  |  |

| RMS Output Voltage  | $V_{Cab,RMS}$    | 220 V                                                         |  |  |  |

| Output Power        | $P_o$            | 2500 W                                                        |  |  |  |

| Output frequency    | $f_g$            | 60 Hz                                                         |  |  |  |

| Power MOSFET        | $S_{1a4b}$       | SCT2120AF                                                     |  |  |  |

| Power MOSFET        |                  | $(R_{DSon} = 120 \text{ m}\Omega/V_{DS,max} = 650 \text{ V})$ |  |  |  |

| Switching Frequency | $f_{sw}$         | 30 kHz                                                        |  |  |  |

| Floating Capacitor  | $C_{2a}, C_{2b}$ | B32778 (60 μF × 800 V)                                        |  |  |  |

| Link Capacitor      | $C_1, C_3$       | MKP1848 (200 μF × 450 V)                                      |  |  |  |

| Output Inductor     | $L_{ab}$         | 900 μΗ                                                        |  |  |  |

| Output Capacitor    | $C_{ab}$         | *2 × B32656S (1 μF × 1000 V)                                  |  |  |  |

| Output Resistor     | $R_{ab}$         | 19.36 Ω                                                       |  |  |  |

<sup>\*</sup> Two capacitors in parallel.

where  $\hat{\mathbf{x}}$  and  $\hat{\mathbf{u}}$  are the small-signal ac variation vectors of the variables presented in (8). For the sake of simplicity, the small-signal perturbation of the input vector  $\hat{\mathbf{u}}$  will be neglected.

After extracting the steady-state values and the secondorder nonlinear terms [18] and applying the Laplace transform, a linear model can be found, as follows:

$$\hat{\mathbf{x}} = [s\mathbf{I}_{5} - [\mathbf{A}_{1}d_{a} + \mathbf{A}_{2}(1 - d_{a}) + \mathbf{A}_{3}d_{b} + \mathbf{A}_{4}(1 - d_{b}) + \mathbf{F}]]^{-1} \cdot \left[ \hat{d}_{a} [(\mathbf{A}_{1} - \mathbf{A}_{2}) \overline{\mathbf{x}} + (\mathbf{B}_{1} - \mathbf{B}_{2}) \overline{\mathbf{u}}] + \hat{d}_{b} [(\mathbf{A}_{3} - \mathbf{A}_{4}) \overline{\mathbf{x}} + (\mathbf{B}_{3} - \mathbf{B}_{4}) \overline{\mathbf{u}}] \right]$$

$$(17)$$

where  $I_5$  is a 5×5 identity matrix.

After substituting the steady-state values of (9) in (17), solving and performing some algebraic manipulation, the FBHSC transfer functions can be found. The small-signal control-to-output transfer function  $G_{vc}(s)$  is defined by

$$G_{vc}(s) = \frac{\langle v_{Cab} \rangle}{\hat{d}_{ab}} = \frac{a_2 s^2 + a_1 s + a_0}{b_4 s^4 + b_3 s^3 + b_2 s^2 + b_1 s + b_0}$$

(18)

where  $C_f = C_{2a} = C_{2b}$  and the coefficients are given by

$$\begin{cases} a_{2} = 4C_{1e}C_{f}(d_{a} - 1)d_{a}R_{DSon}^{2}V_{pn} \\ a_{1} = R_{DSon}\begin{pmatrix} 2(d_{a} - 1)d_{a}(C_{1e} + 2C_{f})V_{pn} + \\ +C_{1e}\overline{\langle i_{Load}\rangle}(2d_{a} - 1)R_{DSon} \end{pmatrix} \\ a_{0} = -8d_{b}^{2}d_{a}^{2}V_{pn} + 2\overline{\langle i_{Load}\rangle}(2d_{a} - 1)R_{DSon} \\ b_{4} = 8C_{1e}C_{f}(d_{a} - 1)d_{a}C_{ab}L_{ab}R_{DSon}^{2} \\ b_{3} = 4(d_{a} - 1)d_{a}C_{ab}R_{DSon}\begin{pmatrix} L_{ab}(C_{1e} + 2C_{f}) + \\ +2C_{1e}C_{f}R_{DSon}^{2} \end{pmatrix} \\ b_{2} = -8d_{b}d_{a}\begin{pmatrix} R_{DSon}^{2}(C_{ab}(C_{1e} + C_{f}) + C_{1e}C_{f}) + \\ +2d_{b}d_{a}C_{ab}L_{ab} \end{pmatrix} \\ b_{1} = 4(d_{a} - 1)d_{a}R_{DSon}\begin{pmatrix} (1 + 4d_{b}d_{a})C_{ab} + \\ +C_{1e} + 2C_{f} \end{pmatrix} \\ b_{0} = -16(d_{a} - 1)^{2}d_{a}^{2} \end{cases}$$

The 4<sup>th</sup> order system obtained in (18) can be simplified by

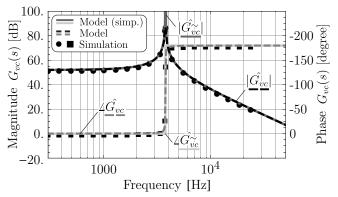

Fig. 7. Frequency responses of the control-to-output transfer function  $G_{vc}(s)$ : analytical model (full and simplified) and numerical simulation.

neglecting the MOSFET on-resistance  $R_{DSon}$ , as follows

$$G_{vc}^{\sim}(s) = G_{vc}(s)\big|_{R_{DSon}=0} = \frac{\frac{V_{pn}}{2}}{s^2 C_{ab} L_{ab} + 1}$$

(20)

Apart from the numerator  $V_{pn}/2$ , the transfer function (20) is the same as that of a FB inverter with an LC output filter. Therefore, conventional compensator design can be applied in the proposed topology to perform the output voltage control.

To validate the simplified model, a set of numerical simulations was performed in PLECS<sup>®</sup> with the parameters shown in Table II. The frequency responses of the simulated and theoretical results are given in Figure 7.

The frequency responses presented in Figure 7 show excellent agreement between the theoretical and simulation results. Therefore, it can be concluded that the switching capacitor dynamics can be neglected without loss of generality, as presented in [10], [20]. As a consequence, a simplified state-space system can be proposed, as follows

$$\dot{\mathbf{x}} = \begin{bmatrix} 0 & \frac{-1}{L_{ab}} \\ \frac{1}{C_{ab}} & 0 \end{bmatrix} \underbrace{\begin{bmatrix} \langle i_{Lab} \rangle \\ \langle v_{Cab} \rangle \end{bmatrix}}_{\mathbf{x}} + \begin{bmatrix} \frac{1}{L_{ab}} & 0 \\ 0 & \frac{-1}{C_{ab}} \end{bmatrix} \begin{bmatrix} \langle v_{ab} \rangle \\ \langle i_{Load} \rangle \end{bmatrix}$$

(21)

where the voltage  $v_{ab}$  is defined by

$$\langle v_{ab} \rangle = \frac{MV_{pn}}{2} \sin(\omega t).$$

(22)

The model detailed in (21) is a large signal model, as used in conventional inverter modelling. Since the simplified model is the matrix representation of the output filter, the dynamic model for other output filter topologies (e.g., L, LCL filters) can be easily deduced.

# IV. DESIGN CONSIDERATIONS FOR THE FLOATING CAPACITORS

Apart from the well-known design criteria (e.g. current stress, voltage ripple), FBHSC floating capacitors must also be designed considering the charge/discharge in the switching period, as in SC design [21]. Otherwise, a high peak current will flow through the components, increasing FBHSC losses.

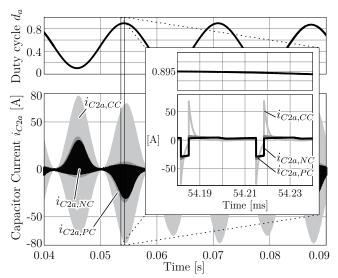

Fig. 8. Simulation results for  $\tau_f$  effect on the capacitor current  $i_{C2a}$  for all SC operation modes: CC, PC and NC.

Maximum instantaneous peak current in the capacitors is dependent on the floating capacitor value, the MOSFET onresistance value, the modulation index M and the switching period  $T_{sw}$ . Depending on these values, the converter can operate in three modes: complete charge (CC), partial charge (PC) and no charge (NC) [21].

As stated in section III, theoretical analysis was performed assuming NC mode. However, NC mode operation requires a high switching frequency or a high capacitance value, resulting in a difficult design process. Thus, the PC mode was selected because it ensures low peak current in capacitors, avoids large capacitance values and provides a small error compared to the NC mode [20], [22]. The PC operation mode, assuming unipolar SPWM, is guaranteed when

$$2R_{DSon}C_f \approx \tau_f > \frac{MT_{sw}}{2} \tag{23}$$

where  $C_{2a} = C_{2b} = C_f$ , and assuming  $C_1 \gg C_f$ .

An example of the floating capacitor design is shown in Figure 8. All parameters are given in Table III, except for the floating capacitors. The operation in the other operation modes was obtained with  $C_{2a} = C_{2b} = 6 \,\mu\text{F}$  (CC mode) and  $C_{2a} = C_{2b} = 400 \,\mu\text{F}$  (NC mode). The PC operation mode was obtained with  $C_{2a} = C_{2b} = 60 \,\mu\text{F}$ , resulting in a time constant  $\tau_f \approx 14.4 \,\mu\text{s}$ .

Even though the peak current through  $C_{2a}$  in the NC mode (29.26 A) is lower than that in the PC mode (34.12 A), the PC mode capacitance is six times lower. In addition, the  $i_{C2a}$  RMS values in the two modes ( $I_{C2a,NC,RMS} = 5.69$  A,  $I_{C2a,PC,RMS} = 5.83$  A) are similar. However, the CC mode must be avoided due to its high peak current (78.56 A) and high RMS value (9.27 A).

As shown in Table II, it was employed capacitors of 60  $\mu$ F to the floating capacitors ( $C_{2a}$  and  $C_{2b}$ ), which fulfills the current stress criteria and ensure the PC mode operation. On the other hand, the link capacitors ( $C_1$  and  $C_3$ ) should be greater than the floating capacitors and fulfill the current stress criteria. Moreover, the link capacitors should limit the well-known low-frequency voltage ripple present in single-phase

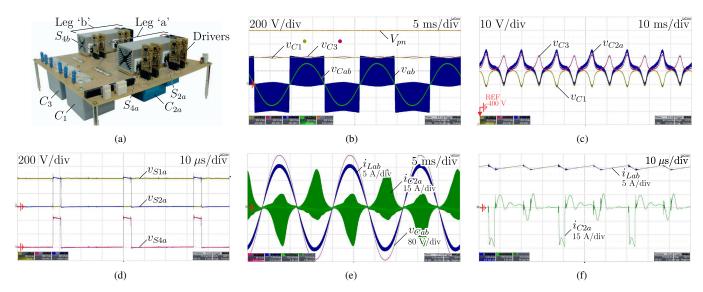

Fig. 9. Picture of the prototype and experimental results for the converter at nominal output power (2.5 kW). (a) Implemented 2.5-kW FBHSC hardware prototype (mechanical dimensions: 238 mm x 246 mm x 115 mm). (b) Input voltage  $V_{pn}$ , capacitor voltages  $v_{C1}$ ,  $v_{C3}$  and  $v_{C2a}$  and output voltage  $v_{Cab}$ . (c) Detailed view of  $v_{C1}$ ,  $v_{C3}$  and  $v_{C2a}$ . (d) Semiconductor voltages  $v_{S1a}$ ,  $v_{S2a}$  and  $v_{S4a}$ . (e) Inductor current  $i_{Lab}$ , floating capacitor current  $i_{C2a}$  and output voltage  $v_{Cab}$ . (f) Detailed view of  $i_{Lab}$  and  $i_{C2a}$ .

systems [23], which is defined by

$$\Delta V_{\%} = \frac{P_o}{4\pi f_g V_{pn}^2 C_{link}} \tag{24}$$

where  $\Delta V_{\%}$  is the percentage of ripple on the input voltage.

Assuming  $\Delta V_{\%} = 4\%$ , a capacitance of approximately 130  $\mu F$  is obtained by (24). Therefore, the dc-link was implemented with two capacitors of 200  $\mu F$  connected in series, which complemented with the floating capacitors [22] fulfills the required voltage ripple.

# V. EXPERIMENTAL RESULTS

A single-SC-cell 2.5-kW FBHSC prototype, as shown in Figure 9(a), was built to evaluate and verify the concepts introduced above. All tests were carried out in open loop, with a modulation index of approximately 0.79 using unipolar SPWM, and with a resistive load, as seen in Figure 3. FBHSC gating signal generation was performed by a microcontroller TMS320F28027, developed by Texas Instruments. All components used in the prototype and the specifications can be found in Table II.

As the converter operates in open loop, the input voltage  $V_{pn}$  was generated by a regulated dc source. However, any control structure applied to VSI inverters (e.g., current control in the inner loop and dc-link control in the outer loop) can be employed.

Due to the low semiconductor voltage stress, silicon carbide (SiC) low-voltage (e.g., 650 V) devices could be used. SiC was also chosen due to its better performance and lower switching losses. With regard to the capacitors, only polypropylene film capacitors were employed in the prototype, due to their high current capability and better reliability, when compared to the aluminum electrolytic capacitors. On the other hand, film capacitors have a higher cost and lower

energy density, leading to a large volume to obtain the needed capacitance [24]. However, due to its low equivalent series resistance (ESR) and the high current stresses common in SC converters, film capacitors can achieve a higher lifetime than the aluminum electrolytic capacitors.

The waveforms in Figures 9(b)-9(f) show the operation at nominal output power. The high step-down inverter operation can be seen in Figure 9(b), which shows all voltages in the same scale, including the switched  $(v_{ab})$  and filtered  $(v_{Cab})$  output voltage. All capacitor voltages are equal to half of the input voltage plus a small ripple (less than 7% of  $V_{pn}/2$ ), as shown in Figure 9(c). Consequently, it is expected that the voltages across the semiconductors are limited to the same value, as seen in Figure 9(d), which shows the voltages  $v_{S1a}$ ,  $v_{S2a}$  and  $v_{S4a}$ .

Figure 9(e) shows the inductor current, the output voltage and the current through the floating capacitor  $C_{2a}$ . As expected, the inductor current and the output voltage are sinusoidal, with a negligible displacement angle. Even though the peak current in the capacitor  $C_{2a}$  is less than 3 times the peak current at the output, the RMS value is less than 60% (6.68 A) of the inductor current.

A detailed view of the current  $i_{C2a}$  (Figure 9(f)) shows the behavior within the switching period, where it can be observed that the converter operates in the PC mode. However, the exponential behavior cannot be clearly seen due to the switching transition resonances, which were probably caused by the parasitic inductances and the PCB layout.

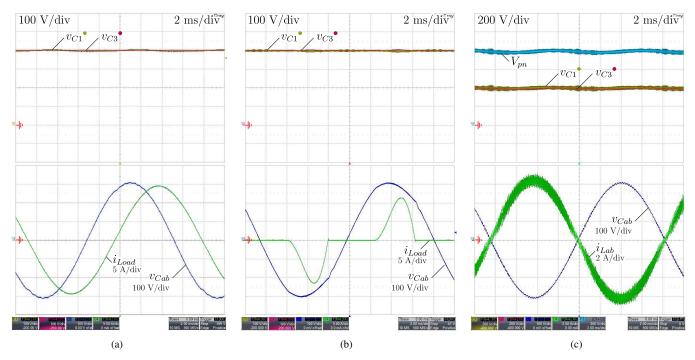

The FBHSC was also tested as a inverter with different types of loads (inductive and nonlinear) and as a rectifier. The parameters are the same presented in Table II, except for the output filter ( $L_{ab}=470~\mu\text{H}$  and  $C_{ab}=8~\mu\text{F}$ ) in all cases, and the switching frequency (50 kHz) at the rectifier and nonlinear load tests. The experimental results are presented in Figure 10.

Figure 10(a) presents the output voltage  $v_{Cab}$  and the output load current  $i_{Load}$  for a 2245 VA inductive load with

Fig. 10. Experimental results of the proposed converter operating with different loads. (a) Inductive load operation: capacitor voltages  $v_{C1}$  and  $v_{C3}$ , output voltage  $v_{Cab}$ , and load current  $i_{Load}$ . (b) Nonlinear load operation: capacitor voltages  $v_{C1}$  and  $v_{C3}$ , output voltage  $v_{Cab}$ , and load current  $i_{Load}$ . (c) Rectifer operation: input voltage  $v_{Dn}$ , capacitor voltages  $v_{C1}$  and  $v_{C3}$ , output voltage  $v_{Cab}$  and output inductor current  $i_{Lab}$ .

a power factor of 0.504. The nonlinear load test, presented in Figure 10(b), was performed with a 1100 VA load with a crest factor of 2.25. At the nonlinear load operation, it is important to analyze the maximum peak current at the semiconductors, since the semiconductor currents is higher than the output current. In both tests, the converter operates properly with low output voltage distortion and maintaining the self-balancing in the capacitors.

Figure 10(c) presents the results with the converter operating as a rectifier. The rectifier operation was achieved by a self-control strategy [25], [26], adapted to the single-phase full-bridge rectifier. The converter was supplied by an ac power source (Agilent 6813B) in order to supply a 970 W resistive load. The self-control constant was adjusted to keep the nominal input (800 V) and output voltage (220 V), as shown in Figure 10(c). As the previously results, the FBHSC operates properly, validating the four-quadrant operation.

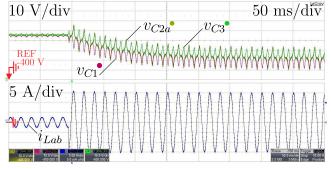

The capacitor voltage balancing was evaluated under load variation conditions. The response for a resistive load step from 15% to 100% is shown in the waveform of Figure 11, and the capacitor voltages  $v_{C1}$ ,  $v_{C3}$  and  $v_{C2a}$  are also shown. Even with a step from a light load to a full load condition, all capacitor voltages remain balanced.

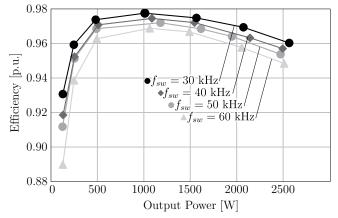

Figure 12 shows the converter efficiency experimentally obtained using the power analyzer WT-1800 (Yokogawa Electric) with resistive load and excluding the output filter losses. The prototype was tested under different switching frequencies in order to verify the best operation point, which was observed to be at 30 kHz. An efficiency of 96.03% at full load (peak of 97.8% for a load of  $0.403P_o$ ) was obtained, which is in good agreement with similar results reported in the literature [27].

Fig. 11. Experimental step response of the output current  $i_{Lab}$  after a load step from 15% to 100% of the output power. Capacitor voltages  $(v_{C1}, v_{C3} \text{ and } v_{C2a})$  are also shown.

Fig. 12. Efficiency curve for the converter as a function of the output power obtained experimentally (excluding output filter losses).

#### VI. TOPOLOGY COMPARISON

This section presents a comparison between the proposed topology and some of the well-known solutions available in the literature: FB, HB (half-bridge), HB-NPC, FB-NPC inverters, and a two-stage architecture (dc-dc bidirectional buck converter plus a FB inverter). Table III presents the results of the comparison, in relation to the specifications given in Table II.

The comparison was performed through some simple metrics. The number of switches  $(n_s)$ , diodes  $(n_d)$ , and capacitors  $(n_{cap})$  were analyzed and grouped according to the blocking voltage. For the topologies with a capacitor divider, it is important to analyze the low-frequency harmonics of the current injected at the midpoint ' $i_{mid,LF}$ ', because this can require a high capacitance value for the capacitor divider [28]. The requirement of an additional control loop for the capacitor voltages and the inverter modulation index M are also considered. The output filter components are excluded from this analysis.

Both HB and FB inverters have the lowest component count. However, all switches are subjected to the full input voltage. Apart from the increase in switching losses, the use of high-voltage switches can yield an increase in conduction losses. For silicon high-voltage MOSFETs ( $V_{DS,max} \geq 600$  V),  $R_{DSon}$  is approximately proportional to the square of the breakdown voltage [29]. On the other hand, FBHSC uses only low-voltage devices, leading to low switching losses and low conduction losses. However, a high semiconductor count, as is the case for the FBHSC inverter, result in a high number of isolated gate-driver circuits, increasing the PCB area and the costs. To alleviate this drawback, some bootstrap techniques can be employed at the FBHSC to reduce the number of gate drive circuits [30].

Based on Table III, HB-NPC can be considered a notable candidate, due to its low component count with low voltage devices. However, HB-NPC has a low-frequency current in the midpoint (worst case in the HB inverter), leading to a high capacitance value. Although the FB-NPC solves the midpoint current issue, both NPC solutions require a voltage control loop for the capacitor voltage balancing, resulting in additional sensors. Although FBHSC has more capacitors, the midpoint current is negligible and the voltages across the capacitors are self-balanced. However, FBHSC achieves self-balancing with

TABLE III

Comparison of Topologies for High Step-Down

Applications

|                          | Component count |   |   |                                     | t | Midpoint                       | Capacitor        | Modul.         |

|--------------------------|-----------------|---|---|-------------------------------------|---|--------------------------------|------------------|----------------|

| Topology                 |                 |   |   | n <sub>c</sub> @<br>V <sub>pn</sub> | - | current<br>i <sub>mid,LF</sub> | balance<br>Loop? | Index<br>M     |

| FBHSC                    | 0               | 8 | 0 | 0                                   | 4 | $\approx 0$                    | no               | $\approx 0.78$ |

| FB                       | 4               | 0 | 0 | 1                                   | 0 | -                              | no               | $\approx 0.39$ |

| HB                       | 2               | 0 | 0 | 0                                   | 2 | $i_{Load}$                     | no               | $\approx 0.78$ |

| HB-NPC                   | 0               | 4 | 2 | 0                                   | 2 | Ki <sub>Load</sub> a           | no               | $\approx 0.78$ |

| FB-NPC                   | 0               | 8 | 4 | 0                                   | 2 | $\approx 0$                    | yes              | $\approx 0.39$ |

| Buck <sup>b</sup><br>+FB | 2               | 4 | 0 | 1                                   | 1 | -                              | no               | ≈ 0.78         |

<sup>&</sup>lt;sup>a</sup> Where  $K = 1 - |M\sin(\omega t)|$ .

the drawback of additional losses (see section III-A).

Low-modulation-index operation, as occurs in FB and FB-NPC, must be avoided because it leads to a higher THD on the output voltage. FB-NPC, for example, when operating with  $M \approx 0.38$  will synthesize only a 3-level voltage, rather than a 5-level voltage. This issue can be resolved through the addition of an output low-frequency stepdown autotransformer, which increases the converter volume and weight. FBHSC avoids the need for the use of autotransformers, since it can synthesize a low ac voltage with a high modulation index. The SC circuit can be seen as an electronic dc-dc autotransformer integrated to an inverter in the proposed topology.

FBHSC can be considered a strong candidate in high step-down applications. Even though FBHSC has a high component count, its features such as low-voltage devices and capacitors with self voltage balancing provide some compensation for its drawbacks. The additional losses, due to capacitor balancing, have a minimal effect on the overall FBHSC losses, reaching a maximum efficiency of 97.08% with the built prototype.

# VII. CONCLUSIONS

In this paper, a novel single-phase inverter topology (FBHSC) was proposed. With the use of low-voltage devices and no additional voltage control loop, the FBHSC can synthesize a low ac voltage from a high dc input voltage. Hence, the FBHSC is suitable for high step-down applications, where the conventional topologies (e.g., FB inverter) cannot operate properly. The FBHSC inverter also includes the following features:

- Single-stage topology with bidirectional power flow;

- Operation in high step-down applications with a high modulation index;

- All switches and capacitors are subjected to half of the input voltage (for one SC cell), leading to low switching and conduction losses;

- The capacitor voltages are naturally self-balanced through the switching states. In addition, the voltage ripple is negligible and the output current control does not provoke imbalance in the capacitors.

- The topology can be generalized by the addition of more SC cells;

- Regardless of the number of SC cells, FBHSC has a low-order dynamic model, resulting in a conventional compensator design;

- FBHSC has a simple modulation strategy, the same as that used in the conventional FB Inverter;

With the built prototype, an efficiency of 96.08% (peak of 97.8%) in a high-conversion-ratio specification was achieved. Although other solutions could be applied to high stepdown applications, the FBHSC overall performance makes the solution proposed herein a noteworthy candidate.

# **ACKNOWLEDGEMENTS**

The authors would like to thank Delvanei Bandeira and Daniel Flores for the collaboration in the revision of this paper.

<sup>&</sup>lt;sup>b</sup> The dc-dc buck converter operates with a duty-cycle of 0.5.

In addition, we would like to acknowledge the funding from the Brazilian National Research Council (CNPq).

#### **APPENDIX**

#### A. State-Space Matrices

The matrices in (7) are defined in (25) to (31).

$$\mathbf{A_{1}} = \begin{bmatrix} \frac{-1}{2C_{1e}R_{DSon}} & \frac{-1}{2C_{1e}R_{DSon}} & 0 - \frac{1}{2C_{1e}} & 0\\ \frac{-1}{2C_{2a}R_{DSon}} & \frac{-1}{2C_{2a}R_{DSon}} & 0 & \frac{1}{2C_{2a}} & 0\\ 0 & 0 & 0 & 0 & 0\\ \frac{1}{2L_{ab}} & -\frac{1}{2L_{ab}} & 0 & \frac{R_{DSon}}{-2L_{ab}} & 0\\ 0 & 0 & 0 & 0 & 0 \end{bmatrix}$$

(25)

$$\mathbf{A_2} = \begin{bmatrix} \frac{-1}{2C_{1e}R_{DSon}} & \frac{1}{2C_{1e}R_{DSon}} & 0 & \frac{-1}{2C_{1e}} & 0\\ \frac{1}{2C_{2a}R_{DSon}} & \frac{-1}{2C_{2a}R_{DSon}} & 0 & \frac{1}{2C_{2a}} & 0\\ 0 & 0 & 0 & 0 & 0\\ \frac{1}{2L_{ab}} & -\frac{1}{2L_{ab}} & 0 & \frac{R_{DSon}}{-2L_{ab}} & 0\\ 0 & 0 & 0 & 0 & 0 \end{bmatrix}$$

(26)

$$\mathbf{A_{3}} = \begin{bmatrix} \frac{-1}{2C_{1e}R_{DSon}} & 0 & \frac{-1}{2C_{1e}R_{DSon}} & \frac{1}{2C_{1e}} & 0\\ 0 & 0 & 0 & 0 & 0\\ \frac{-1}{2C_{2b}R_{DSon}} & 0 & \frac{-1}{2C_{2b}R_{DSon}} & \frac{-1}{2C_{2b}} & 0\\ \frac{-1}{2L_{ab}} & 0 & \frac{1}{2L_{ab}} & \frac{R_{DSon}}{-2L_{ab}} & 0\\ 0 & 0 & 0 & 0 & 0 \end{bmatrix}$$

(27)

$$\mathbf{A_4} = \begin{bmatrix} \frac{-1}{2C_{1e}R_{DSon}} & 0 & \frac{1}{2C_{1e}R_{DSon}} & \frac{1}{2C_{1e}} & 0\\ 0 & 0 & 0 & 0 & 0\\ \frac{1}{2C_{2b}R_{DSon}} & 0 & \frac{-1}{2C_{2b}R_{DSon}} & \frac{-1}{2C_{2b}} & 0\\ \frac{-1}{2L_{ab}} & 0 & \frac{1}{2L_{ab}} & \frac{R_{DSon}}{-2L_{ab}} & 0\\ 0 & 0 & 0 & 0 & 0 \end{bmatrix}$$

(28)

$$\mathbf{B_1}^T = \begin{bmatrix} \frac{1}{2C_{1e}R_{DSon}} & \frac{1}{2C_{2a}R_{DSon}} & 0 & \frac{1}{2L_{ab}} & 0\\ 0 & 0 & 0 & 0 \end{bmatrix}, \mathbf{B_2} = 0\mathbf{I}_{5\times2} \quad (29)$$

$$\mathbf{B_3}^T = \begin{bmatrix} \frac{1}{2C_{1e}R_{DSon}} & 0 & \frac{1}{2C_{2b}R_{DSon}} & \frac{-1}{2L_{ab}} & 0\\ 0 & 0 & 0 & 0 \end{bmatrix}, \mathbf{B_4} = 0\mathbf{I}_{5\times2} \quad (30)$$

# REFERENCES

- [1] R. Gonzalez, J. Lopez, P. Sanchis, L. Marroyo, "Transformerless Inverter for Single-Phase Photovoltaic Systems", *IEEE Transactions on Power Electronics*, vol. 22, no. 2, pp. 693–697, Mar. 2007.

- [2] N. Mohan, T. M. Undeland, W. P. Robbins, *Power Electronics: Converters, Applications, and Design*, 3rd ed., Wiley, Hoboken, NJ, 2002.

- [3] A. Nabae, I. Takahashi, H. Akagi, "A New Neutral-Point-Clamped PWM Inverter", *IEEE Transactions on Industry Applications*, vol. IA-17, no. 5, pp. 518–523, Sept. 1981.

- [4] S. Busquets-Monge, S. Alepuz, J. Bordonau, J. Peracaula, "Voltage Balancing Control of Diode-Clamped Multilevel Converters With Passive Front-

- Ends", *IEEE Transactions on Power Electronics*, vol. 23, no. 4, pp. 1751–1758, July 2008.

- [5] J. Pou, D. Boroyevich, R. Pindado, "Effects of imbalances and nonlinear loads on the voltage balance of a neutral-point-clamped inverter", *IEEE Transactions on Power Electronics*, vol. 20, no. 1, pp. 123–131, Jan. 2005.

- [6] S. Xiong, S.-C. Wong, S.-C. Tan, C. Tse, "A Family of Exponential Step-Down Switched-Capacitor Converters and Their Applications in Two-Stage Converters", *IEEE Transactions on Power Electronics*, vol. 29, no. 4, pp. 1870–1880, April 2014.

- [7] M. Chen, K. K. Afridi, S. Chakraborty, D. J. Perreault, "Multitrack Power Conversion Architecture", *IEEE Transactions on Power Electronics*, vol. 32, no. 1, pp. 325–340, Jan. 2017.

- [8] M. Kline, I. Izyumin, B. Boser, S. Sanders, "A transformerless galvanically isolated switched capacitor LED driver", in *Proceedings of APEC*, pp. 2357–2360, 2012.

- [9] M. Uno, "High Step-Down Converter Integrating Switched Capacitor Converter and PWM Synchronous Buck Converter", in Proceedings of INTELEC, pp. 273– 278, 2013.

- [10] D. Flores Cortez, M. C. Maccarini, S. A. Mussa, I. Barbi, "High Static Gain Single-phase PFC Based on a Hybrid Boost Converter", *International Journal of Electronics*, vol. 104, no. 5, pp. 821–839, Dec. 2016.

- [11] F. Z. Peng, "A generalized multilevel inverter topology with self voltage balancing", *IEEE Transactions on Industry Applications*, vol. 37, no. 2, pp. 611–618, Apr. 2001.

- [12] R. d. S. Santos, T. B. Lazzarin, I. Barbi, "A new half-bridge Hybrid Switched-Capacitor inverter", *in Proceedings of COBEP-SPEC*, pp. 1142–1147, 2015.

- [13] A. Tsunoda, Y. Hinago, H. Koizumi, "Level and Phase-Shifted PWM for Seven-Level Switched-Capacitor Inverter Using Series/Parallel Conversion", *IEEE Transactions on Industrial Electronics*, vol. 61, no. 8, pp. 4011–4021, Aug. 2014.

- [14] A. Taghvaie, J. Adabi, M. Rezanejad, "Circuit Topology and Operation of a Step-Up Multilevel Inverter With a Single DC Source", *IEEE Transactions on Industrial Electronics*, vol. 63, no. 11, pp. 6643–6652, Nov. 2016.

- [15] R. Samanbakhsh, A. Taheri, "Reduction of Power Electronic Components in Multilevel Converters Using New Switched Capacitor-Diode Structure", *IEEE Transactions on Industrial Electronics*, vol. 63, no. 11, pp. 7204–7214, Nov. 2016.

- [16] C. Le, M. Kline, D. L. Gerber, S. R. Sanders, P. R. Kinget, "A stackable switched-capacitor DC/DC converter IC for LED drivers with 90% efficiency", in *Proceedings of CICC*, pp. 1–4, 2013.

- [17] F. Dupont, C. Rech, R. Gules, J. Pinheiro, "Reduced order model of the boost converter with voltage multiplier cell", *in Proceedings of COBEP*, pp. 473–478, 2011.

- [18] R. W. Erickson, D. Maksimovic, Fundamentals of Power Electronics, 2nd ed., Kluwer Academic Publishers, New York, N.Y, 2001.

- [19] P. Li, G. Adam, Y. Hu, D. Holliday, B. Williams, "Three-Phase AC-Side Voltage-Doubling High Power Density Voltage Source Converter With Intrinsic Buck-Boost Cell and Common-Mode Voltage Suppression", *IEEE Transactions on Power Electronics*, vol. 30, no. 9, pp. 5284–5298, Sep. 2015.

- [20] D. Cortez, I. Barbi, "A Three-Phase Multilevel Hybrid Switched-Capacitor PWM PFC Rectifier for High-Voltage-Gain Applications", *IEEE Transactions on Power Electronics*, vol. 31, no. 5, pp. 3495–3505, May 2016.

- [21] S. Ben-Yaakov, "Behavioral Average Modeling and Equivalent Circuit Simulation of Switched Capacitors Converters", *IEEE Transactions on Power Electronics*, vol. 27, no. 2, pp. 632–636, Feb. 2012.

- [22] R. Andersen, T. Lazzarin, I. Barbi, "A 1-kW Step-Up/Step-Down Switched-Capacitor AC-AC Converter", *IEEE Transactions on Power Electronics*, vol. 28, no. 7, pp. 3329–3340, July 2013.

- [23] S. Araujo, P. Zacharias, R. Mallwitz, "Highly Efficient Single-Phase Transformerless Inverters for Grid-Connected Photovoltaic Systems", *IEEE Transactions* on *Industrial Electronics*, vol. 57, no. 9, pp. 3118–3128, Sep. 2010.

- [24] H. Wang, F. Blaabjerg, "Reliability of Capacitors for DC-Link Applications in Power Electronic Converters - An Overview", *IEEE Transactions on Industry Applications*, vol. 50, no. 5, pp. 3569–3578, Sep. 2014.

- [25] S. Ben-Yaakov, I. Zehser, "PWM converters with resistive input", *IEEE Transactions on Industrial Electronics*, vol. 45, no. 3, pp. 519–520, Jun. 1998.

- [26] D. Borgonovo, Análise, Modelagem e Controle de Retificadores PWM Trifásicos, Doctorate Thesis, Federal University of Santa Catarina, Florianópolis, SC, 2005.

- [27] A. Anthon, Z. Zhang, M. A. E. Andersen, T. Franke, "Efficiency investigations of a 3kW T-Type inverter for switching frequencies up to 100 kHz", in Proceedings of IPEC-ECCE, pp. 78–83, 2014.

- [28] T. Tanaka, T. Sekiya, Y. Baba, M. Okamoto, E. Hiraki, "A new half-bridge based inverter with the reduced-capacity DC capacitors for DC micro-grid", in *Proceedings of ECCE*, pp. 2564–2569, 2010.

- [29] M. Hartmann, Ultra-compact and ultra-efficient threephase PWM rectifier systems for more electric aircraft, Ph.D. thesis, Eidgenössische Technische Hochschule ETH Zürich, Zurich, Swiss, 2011.

[30] J. J. Graczkowski, K. L. Neff, X. Kou, "A Low-Cost Gate Driver Design Using Bootstrap Capacitors for Multilevel MOSFET Inverters", *in Proceedings of IPEMC*, vol. 2, pp. 1096–1100, 2006.

#### **BIOGRAPHIES**

Rodrigo de Souza Santos was born in São Paulo, Brazil, in 1986. He received the B.S. degree from the São Paulo Engineering College, São Paulo (SP), Brazil, and the M.S. degree in 2013 from the Federal University of Santa Catarina, Florianópolis (SC), Brazil, both in electrical engineering. He is currently working toward the Ph.D. degree in electrical engineering at the Power Electronics Institute of Federal University of the Santa Catarina. His interests include dedc bidirectional converters, switched-capacitor converters, and current source converters.

Telles Brunelli Lazzarin was born in Criciúma, Brazil, in 1979. He received the B.Sc., M.Sc., and Ph.D. degrees in electrical engineering from the Federal University of Santa Catarina (UFSC), Florianópolis, Brazil, in 2004, 2006, and 2010, respectively.

He is currently an Adjunct Professor with the UFSC. His interests include inverters, parallel operation of inverters, UPS, high-voltage dc-dc converters, direct ac-ac power converters, switched capacitor (SC) converters, and hybrid SC converters.

Dr. Lazzarin is a member of the Brazilian Power Electronics Society (SOBRAEP), IEEE Power Electronics Society (PELS), and IEEE Industrial Electronics Society (IES).

Ivo Barbi was born in Gaspar, Santa Catarina, Brazil, in 1949. He received the B.S. and M.S. degrees in electrical engineering from the Federal University of Santa Catarina, Florianópolis, Brazil, in 1973 and 1976, respectively, and the Dr. Ing. degree from the Institut National Polytechnique de Toulouse, Toulouse, France, in 1979. He founded the Brazilian Power Electronics Society (SOBRAEP) and the Brazilian Power Electronics Conference (COBEP) in 1990, and the Brazilian Power Electronics and Renewable Energy Institute (IBEPE) in 2016.

Prof. Barbi is an Associate Editor of the IEEE Transactions on Power Electronics and the IET Electronics Letters, President of the Brazilian Power Electronics and Renewable Energy Institute (IBEPE), researcher at the Solar Energy Research Center and Professor of Electrical Engineering at Federal University of Santa Catarina (Brazil).