# MODELO ANALÍTICO DE CÁLCULO DE PERDAS EM MOSFETS DE POTÊNCIA PARA APLICAÇÃO EM BANCO DE DADOS

Edemar O. Prado<sup>1,2</sup>, Pedro C. Bolsi<sup>1,2</sup>, Hamiltom C. Sartori<sup>1</sup>, José Renes Pinhero<sup>1,2</sup>

<sup>1</sup>Universidade Federal de Santa Maria – UFSM, Santa Maria – RS, Brasil

<sup>2</sup>Universidade Federal da Bahia – UFBA, Salvador – BA, Brasil

e-mail: edemar.prado@ufba.br, pcbolsi@gmail.com, hamiltomsar@gmail.com, jrenes@gepoc.ufsm.br

Resumo - Este artigo apresenta um modelo analítico simples e acurado para cálculo de perdas em MOSFETs de potência. Uma análise comparativa entre o modelo proposto e modelos comumente utilizados na literatura é mostrado. O modelo proposto utiliza uma simplificação na modelagem das cargas das capacitâncias parasitas. Variações da temperatura de junção com a variação da frequência são consideradas. Resultados térmicos obtidos experimentalmente são usados para validar o modelo em frequências de até 300 kHz. Os resultados demonstram acurácia do modelo proposto usando dois part numbers de MOSFETs diferentes, com as tecnologias de superjunção e Silício convencional. Devido à acurácia e simplicidade de implementação, este modelo é recomendado para utilização em análises onde são verificados extensivos pontos de operação (tensão, frequência e potência), algorítimos genéticos e aplicações com banco de dados.

Palavras-chave – Capacitância Miller, Frequência de comutação, Modelo analítico, MOSFETs, Perdas de comutação.

### ANALYTICAL MODEL FOR THE CALCULATION OF LOSSES IN POWER MOSFETS FOR DATABASE APPLICATIONS

Abstract - This work presents a simple and accurate analytical model for power MOSFET loss calculation. A comparative analysis among commonly used methods in the literature and the proposed approach is presented. The proposed model uses a simplification of the charge behavior of MOSFET parasitic capacitances. Junction temperature variation with frequency is considered. Thermal measurements are used to validate the model up to 300 kHz. Results demonstrate the accuracy of the proposed model using two different MOSFET part numbers, of superjunction and conventional silicon technology. Due to the accuracy and simplicity of the model, it is recommended for use in analyses where many operating points are tested (voltage, frequency, power), genetic algorithms, and database applications.

*Keywords* – Analytical model, Miller capacitance, MOSFETs, Switching frequency, Switching losses.

Manuscript received 07/14/2021; first revision 08/31/2021; accepted forpublication 11/13/2021, by recommendation of Editor Demercil de Souza Oliveira Jr. http://dx.doi.org/10.18618/REP.2021.4.0023.

### I. INTRODUÇÃO

O avanço no desenvolvimento de tecnologias de semicondutores wide bandgap e de superjunção aplicados a transistores MOSFET, torna crescente a operação de conversores em hard-switching com alta densidade de potência em frequências na ordem de dezenas e centenas de kHz [1]–[3]. Nestas situações a potência dissipada no transistor deve ser calculada de forma correta. Caso contrário o rendimento do conversor pode ser mal interpretado e projetos de sistemas de transferência de calor subdimensionados, podendo ocasionar a fusão da junção, ou superdimensionados tornando-os volumosos e com custos adicionais indesejados.

Comumente existem três métodos computacionais capazes de estimar a potência dissipada durante a operação dos transistores do tipo FET: A análise por elementos finitos (*Finite Element Analysis*, FEA), o SPICE e o analítico [4], [5]. As principais diferenças entre eles estão relacionadas à exatidão nos resultados, a complexidade na implementação e ao tempo computacional exigido. Embora com menor acurácia, o modelo analítico apresenta maior simplicidade na modelagem e a maior velocidade de processamento em relação ao modelo SPICE e o FEA, por essa razão torna-se atrativo e preferido em projetos de otimização que utilizam banco de dados, buscando soluções por varreduras [3], [6], [7].

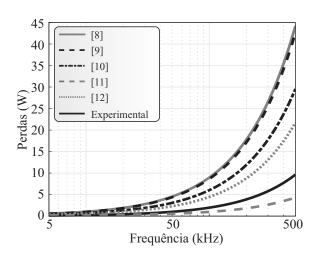

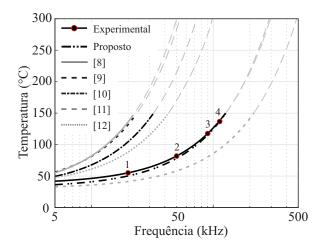

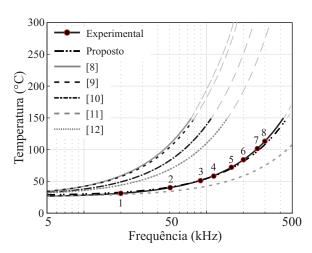

Nas últimas décadas diferentes autores abordaram e sugeriram modelos analíticos [8]–[12]. A Figura 1 mostra um comparativo entre estes modelos e a potência dissipada obtida experimentalmente. Os parâmetros do circuito de testes são mostrados na Tabela I. Maiores detalhes do circuito de teste utilizado são mostrados na Seção IV.

Nos pontos de operação mostrados na Figura 1, os modelos analíticos apresentaram resultados próximos aos experimentais em frequências de comutação abaixo de 50 kHz. Entretanto, com o aumento da frequência de comutação há também um aumento no erro relativo. Este comportamento está diretamente relacionado ao balanço entre as perdas por condução e comutação. De modo geral, em baixa frequência as perdas por comutação são dominantes sobre as perdas por comutação, correspondendo ao maior percentual de perdas. Com o aumento da frequência, o percentual de perdas por comutação aumenta gradativamente, resultando no aumento do erro relativo.

Isso não significa que os modelos analisados são necessariamente incorretos, pois geralmente quando um modelo analítico é desenvolvido ele leva em consideração pontos de operação específicos. Para obter um modelo analítico acurado sob diferentes pontos de operação, os

Fig. 1. Comparativo entre a simulação de modelos analíticos e resultados experimentais na faixa de 5 - 500 kHz.

### TABELA I Parâmetros do circuito

| Parâmetro                    | Símbolo   | Valor       |

|------------------------------|-----------|-------------|

| Tensão de ruptura            | $V_{DSb}$ | 600V        |

| Tensão de bloqueio           | $V_{DS}$  | 300 V       |

| Indutância                   | L         | 1,7 mH      |

| Carga                        | R         | 70 Ohm      |

| Tensão de gate               | $V_G$     | 15 V        |

| Resistência de gate          | $R_G$     | 15 Ohm      |

| Corrente Média<br>no indutor | $I_{MED}$ | 2,14 A      |

| Duty cycle                   | D         | 0,5         |

| Frequência                   | $F_{SW}$  | 5 - 500 kHz |

| Transistor                   | #         | IPW60R040C7 |

fenômenos físicos relacionados a temperatura de junção, níveis de tensão e frequência de comutação aplicados ao transistor devem ser modelados de forma adequada.

Com base nestas considerações, este artigo propõe um modelo analítico acurado para auxiliar na estimativa de perdas em MOSFETs de potência. A análise comparativa entre o modelo proposto, os modelos analíticos de [8]–[12] e resultados obtidos experimentalmente também é apresentada. Na Seção II são fornecidas equações para cálculo de perdas por condução, considerando o comportamento físico da resistência *drain-to-source* em relação a temperatura de junção. Na Seção III é mostrada a modelagem das não linearidades da capacitância Miller em função da variação das tensões de bloqueio. Na Seção IV o somatório da potência dissipada no transistor é utilizado em validações térmicas do modelo proposto em relação a resultados experimentais, nesta seção também são apresentadas as discussões dos resultados obtidos. A Seção V é dedicada às conclusões.

### II. MODELO DE PERDAS POR CONDUÇÃO

O modelo analítico para obter a potência dissipada durante o período de condução dos transistores do tipo MOSFET foi amplamente difundido em artigos acadêmicos [8], [9], [11], notas de aplicação [10], [12] e livros [13], [14], em todos os casos está relacionada ao produto do quadrado da corrente eficaz com a resistência  $drain-to-source\ on-state\ (R_{DSon})$ .

A obtenção de  $R_{DSon}$  está associada aos mecanismos que determinam as mobilidades de portadores [15]–[17]. Em um cristal puro os portadores são espalhados principalmente pela interação com as vibrações geradas termicamente dos átomos do substrato em função da temperatura. A saturação da velocidade de *drift* de portadores quentes reduz significativamente sua mobilidade [17]. Uma revisão sobre esse assunto também pode ser encontrada em [18].

Para fins de simulação, devido à grande complexidade e a dificuldade de modelar com acurácia este fenômeno e suas interações, normalmente é necessária uma lei de potência simples. Os coeficientes são obtidos pela adequação dos valores da mobilidade experimental em função da temperatura, representado pelas curvas  $R_{DSon}$  x  $T_J$  fornecidas pelos fabricantes.

Dentre os modelos supracitados, [12] apresenta um modelo que representa o comportamento da curva  $R_{DSon} \times T_J$  na forma matemática

$$R_{DSon(T_J)} = R_{DSonMAX}(25^{\circ}C).\left(1 + \frac{\alpha}{100}\right)^{T_J - 25^{\circ}C}$$

(1)

onde  $T_J$  é a temperatura de junção durante a operação e  $R_{DSonMAX}$  25 °C é o valor máximo de  $R_{DSon}$  a (25 °C) mostrado no *datasheet*. Rearranjando (1) o coeficiente de temperatura  $\alpha$  pode ser calculado com dois conjuntos de valores ( $T_{J1}$ ,  $R_{DSon1}$ ) e ( $T_{J2}$ ,  $T_{DSon2}$ ),

$$\alpha = 100 \left( \left( \frac{R_{DSon2}}{R_{DSon1}} \right)^{\left( \frac{1}{T_{J2} - T_{J1}} \right)} - 1 \right)$$

(2)

sendo  $R_{DSon1}$  é a resistência de condução máxima a 25 °C,  $T_{J2}$  é um segundo ponto de temperatura da curva  $R_{DSon}$  (deve ser extraído próximo a temperatura de fusão do transistor) e  $R_{DSon2}$  é a resistência equivalente em  $T_{J2}$ .

Assim as perdas por condução podem ser calculadas

$$P_C = R_{DSon(Tj)} I_{RMS}^2. (3)$$

Desta forma para validar a análise comparativa, (3) foi utilizada em todos os modelos mostrado na Figura 1, de modo a considerar a mesma dependência térmica na correção de  $R_{DSon}$ . Além da temperatura de junção, a tensão de *gate* tem impacto direto na resistência de condução, neste sentido, este artigo faz uma avaliação de transistores trabalhando na região de saturação.

### III. MODELO DE PERDAS POR COMUTAÇÃO

As perdas por comutação possuem maior complexidade na elaboração do modelo quando comparadas com as perdas por condução. Diferentes autores apresentaram metodologias para o cálculo das perdas por comutação em MOSFETs de potência. A diferença entre os modelos está relacionada à estratégia de determinação dos tempos de carga e descarga das capacitâncias parasitas entre *gate* e *source* ( $Q_{GS}$ ) e entre *gate* e *drain* ( $Q_{GD}$ ). Nestes períodos ocorrem as sobreposições entre tensão e corrente nos transistores, também chamados de tempos de *overlap*. Em [8]–[12], os tempos de *overlap* são

utilizados em (4) para determinar as perdas por comutação,

$$P_{SW} = \frac{1}{2} (t_{on} V_{DS} I_{on} + t_{off} V_{DS} I_{off}) F_{SW}$$

(4)

onde  $V_{DS}$  é a tensão de bloqueio,  $I_{on}$  e  $I_{off}$  as correntes de comutação na entrada e saída de condução respectivamente e  $t_{on}$  e  $t_{off}$  os tempos de overlap. Em alguns casos ( [9], [11], [12]) são acrescidas a (4) perdas capacitivas referentes a capacitância de saída do transistor ( $C_{OSS}$ ). De acordo com [19] as contribuições de perda de energia da descarga e carga de  $C_{OSS}$  ao acionar e bloquear se cancelam quase completamente. A energia armazenada em  $C_{OSS}$  já está contabilizada no cálculo da energia de bloqueio do MOSFET. Considerar o termo implicaria redundância no cálculo, portanto não será considerado neste artigo.

Com o aumento da frequência, as indutâncias parasita internas aos transistores e de PCB tem impacto nos transitórios de tensão e corrente [5], [19], [20]. Devido à complexidade e incertezas ao determinar o valor dessas indutâncias (dependem do *layout* utilizado), a análise comparativa desenvolvida neste artigo não considera o impacto das indutância parasitas.

### A. Modelagem de $Q_{GS}$

A modelagem dos comportamentos de carga e descarga da capacitância  $gate - source (C_{GS})$  são obtidas durante o período em que a tensão de gate do transistor está entre a tensão de Limiar  $(V_{TH})$  e a tensão de  $Plateau (V_{PL})$  (tempo em que ocorrem as transições de corrente). Como  $C_{GS}$  é relativamente maior que a capacitância  $gate - drain (C_{GD})$ , também chamada de capacitância Miller ou capacitância de transferência reversa  $C_{RSS}$ ) e altamente linear, é usual aproxima-la pela capacitância de entrada  $(C_{ISS})$  [5]. Assim a carga pode ser definida como o produto de  $C_{ISS}$  pela diferença entre  $V_{PL}$  e  $V_{TH}$ ,

$$Q_{GS} = C_{ISS}(V_{PL} - V_{TH}). \tag{5}$$

### B. Revisão da Modelagem de Q<sub>GD</sub>

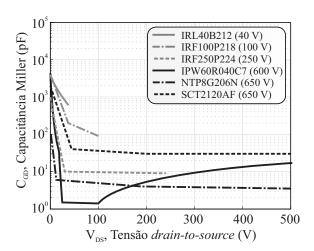

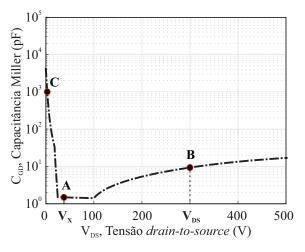

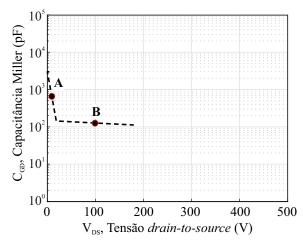

A modelagem da carga e descarga de  $C_{GD}$  ocorrem nas transições de tensão do transistor. A capacitância  $C_{GD}$  é relativamente menor que  $C_{GS}$  e altamente não linear em função da variação de tensão, o que torna a análise complexa. De acordo com [21] este fenômeno é perceptível principalmente em transistores cuja capacidade de bloqueio de tensão é maior do que 40 V. Os *part numbers* IRL40B212 (Si), IRF100P218 (Si), IRF250P224 (Si), IPW60R040C7 (CoolMOS), NTP8G206N (GaN cascode) e SCT2120AF (SiC) utilizados na Figura 2 foram selecionados considerando diferentes tecnologias e tensões de bloqueio, de modo a tornar a analise representativa.

Embora com amplitudes diferentes, o comportamento de  $C_{GD}$  para os MOSFETs IRF100P218, IRF250P224, IPW60R040C7, NTP8G206N e SCT2120AF são similares, apresentando um estágio com maior variação em tensões abaixo de 40 V e outro com menor variação entre 40 V e a tensão de ruptura do transistor. O MOSFET IRL40B212 ( $V_{DS} < 40$  V) apresenta apenas um estágio de variação da capacitância.

Como mencionado, o comportamento e a maneira de

Fig. 2. Comparativo do comportamento de  $C_{GD}$  entre MOSFETs com diferentes tensões de bloqueio e tecnologias.

utilizar  $C_{GD}$  no cálculo das perdas por comutação foi abordado em diferentes modelos analíticos [8]–[12]. Parte destes modelos foram projetados e validados para calcular a potência dissipada em MOSFETs que geralmente operam tensões de bloqueio inferiores a 40 V como são os casos de [8] e [12]. Com o avanço no desenvolvimento das tecnologias SiC, CoolMOS e GaN a aplicação destes transistores em projetos de otimização em frequências acima de  $100 \ kHz$  é crescente. Da mesma forma, a utilização destes modelos onde maiores tensões de operação são empregadas é recorrente [22],[23].

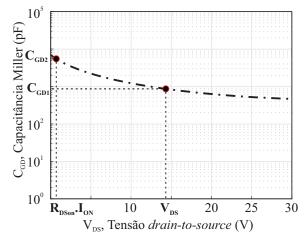

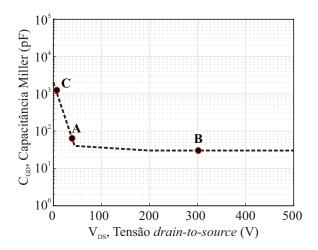

Na Figura 3 é mostrado o modelo para utilização da  $C_{GD}$  em tensões menores que 40 V proposto por [12]. Embora não seja a aplicação de projeto, este modelo é utilizado de forma equivocada em artigos para calcular as perdas por comutação em transistores que operam em tensões de bloqueio na faixa de 400 V [23], [24]. Neste modelo a  $C_{GD}$  é obtida por dois pontos da curva da capacitância versus tensão. O primeiro ponto ou  $C_{GD1}$  é extraído na tensão de bloqueio aplicada ao transistor  $(V_{DS})$  e o segundo ponto na tensão equivalente a queda de tensão do canal  $(R_{DSon}I_{ON})$ , apontada como  $C_{GD2}$ . A diferença no comportamento da capacitância Miller em diferentes tensões de bloqueio mostrada na Figura 2, pode

Fig. 3. Modelo para extração da  $C_{GD}$  utilizando dois pontos da curva capacitância Miller x tensão drain-to-source proposto por [12].

ocasionar erros na utilização do modelo analítico de [12]. A incorreta escolha de  $C_{GD}$  resultará em erro no cálculo da potência dissipada. Este erro se acentua com o aumento da frequência de comutação.

Em [25] é proposto um modelo para calcular com maior acurácia os tempos dos transitórios de tensão. Neste modelo são extraídos 300 pontos da curva  $C_{GD} \times V_{DS}$  (1 ponto por Volt). A acurácia no cálculo de perdas nos transitórios de tensão é melhorada, porém surgem problemas de complexidade na implementação e tempo computacional. Quando se trabalha com banco de dados, podem ser utilizadas dezenas ou centenas de *part numbers* de transistores de diferentes tecnologias, inviabilizando a utilização do modelo. Outra dificuldade para a utilização deste modelo está relacionada à resolução das curvas de  $C_{GD}$  ja que na maioria dos *datasheets* as escalas são logarítmicas, necessitando da utilização de um software computacional para correta extração dos pontos [26].

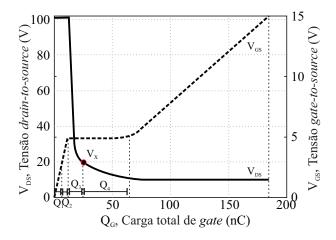

Já [19] aborda de forma multifísica o comportamento de carga e descarga de  $C_{GD}$  em transistores MOSFET. Como resultado o autor propõe analisar a carga entre gate e drain  $(Q_{GD})$  como duas parcelas distintas chamadas de  $Q_3$  e  $Q_4$  (Figura 4). Durante  $Q_3$   $V_{DS}$  cai rapidamente até a tensão de transição  $V_X$  e depois diminui lentamente até a queda de tensão no transistor durante o período de condução  $(V_{DSon})$ . Ainda, conforme o autor,  $V_X$  representa o  $V_{DS}$  no qual a camada n-epitaxial sob o óxido de porta muda de depleção para acumulação.  $Q_3$  é definido como o incremento de carga de gate necessário para a tensão  $V_{DS}$  cair para a tensão de transição  $V_X$  e representa a parcela mais significativa de perdas.  $Q_4$  tem pouca influência nas perdas de comutação e pode ser desconsiderada.

Esta abordagem resultou em um modelo analítico validado no software DESSIS, obtendo boa exatidão. Porém, como os fabricantes fornecem apenas a carga total entre *gate* e *drain*  $(Q_{GD})$ , não é possível identificar qual parcela corresponde a  $Q_3$  e a  $Q_4$ , prejudicando a utilização deste modelo analítico.

### C. Modelo Proposto Para Determinar $Q_{GD}$

Embora com contribuições importantes, os modelos analíticos de [12] e [19] não são adequados para estimar o

Fig. 4. Características da carga de *gate* em função da tensão drain-to-source (adaptado de [19]).

comportamento de  $Q_{GD}$  em transistores fabricados para operar em tensões acima de 100 V. Enquanto o modelo de [25] não é indicado para aplicações que utilizam varreduras e banco de dados.

Sendo assim, este trabalho propõem a utilização destes conceitos e metodologias de forma conjunta. No modelo proposto, os pontos para extração de  $C_{GD}$  sugeridos por [12] devem ser escolhidos considerando as contribuições sobre análise da carga de *gate* fornecida por [19]. Com isso buscase modelar analiticamente a parcela de  $Q_{GD}$  responsável pela maior parte das perdas durante os transitórios de tensão, chamada de  $Q_3$  em [19].

Na Figura 5 o modelo proposto é representado pelos pontos destacados como A e B. Estes pontos devem ser extraídos na tensão de bloqueio sobre o transistor (ponto B, 300 V) e no ponto A equivalente à  $V_X$  em [19]. A determinação do ponto  $V_X$  foi associada com a constante de tempo de circuitos RC ( $\tau$ ) representando a queda de tensão de  $V_{DS}$  em 2 $\tau$ , onde a tensão atinge 13.5 % de  $V_{DS}$  (40,5 V). Esta tensão sempre será 13,5% em 2 $\tau$ , independente dos atuais valores de  $V_{CD}$  e  $V_{CD}$  ( $V_{CD}$ ).

A base do método proposto é uma linearização: traçando uma linha entre as tensões  $V_{DS}$  e  $V_X$  da Figura 4, um triângulo é formado; dentro dele está a maior parte da área de sobreposição de tensão e corrente. Esta área aumentaria se mais constantes de tempo fossem utilizadas, resultando em perdas de comutação estimadas mais altas. Por outro lado, constantes de tempo menores resultariam em uma área de sobreposição estimada menor.

Por exemplo, escolher uma constante de tempo maior que  $4\tau$  resultaria em um  $V_X$  próximo à queda de tensão no estado de condução ( $V_{DSon}$ ). Isso resultaria em alocar  $V_X$  conforme pretendido por [12], no  $C_{GD2}$  da Figura 3. Por outro lado, escolher um valor abaixo de  $1\tau$  resultaria em  $V_X$  sendo muito perto de  $V_{DS}$ , e o tempo de carga de  $C_{GD}$  tenderia a zero.

Com base nestas discussões, a tensão de transição  $V_X$  é colocado na curva  $C_{GD} \times V_{DS}$  a 13,5% do  $V_{DS}$ . A Figura 5 ilustra esta localização para o *part number* do MOSFET usado na validação experimental.

Fig. 5. Modelagem da capacitância Miller do transistor IPW60R040C7 (tecnologia superjunção) utilizando os pontos de extração sugeridos pelo autor (pontos A e B) em comparativo com os sugeridos por [12] (pontos B e C).

Fig. 6. Modelagem da capacitância Miller do transistor SCT2120AF (tecnologia SiC) utilizando os pontos de extração sugeridos pelo autor (pontos A e B) em comparativo com os sugeridos por [12] (pontos B e C).

A Figura 6 mostra a modelagem de  $C_{GD}$  para o transistor SCT2120AF seguindo a mesma metodologia aplicada na Figura 5. Para o modelo proposto são utilizados os pontos B (tensão de bloqueio, 300 V) e A (equivalente de  $V_X$ , 40,5 V).

Com a utilização dos pontos A e B, a carga média associada a capacitância de Miller em função da tensão sobre o transistor pode ser calculada,

$$Q_{GD} = \left(\frac{C_{GD(B)}V_{DS} + C_{GD(A)}0.135V_{DS}}{2}\right)$$

(6)

onde  $C_{GD(B)}$  é a capacitância *gate-to-drain* na tensão de bloqueio aplicada e  $C_{GD(A)}$  é a capacitância *gate-to-drain* em 13.5 % de  $V_{DS}$  (ponto A). Assim, a carga responsável pelas perdas de comutação no MOSFET (7) pode ser obtida pela soma da  $Q_{GS}$  com a  $Q_{GD}$  obtidas por (5) e (6) respectivamente,

$$Q = Q_{GS} + Q_{GD} \tag{7}$$

e pela razão entre a carga e a corrente fornecida pelo circuito de acionamento, é possível determinar os tempos de *overlap* para a entrada (8) e sáida de condução (9),

$$t_{on} = \frac{Q}{I_{Gon}} \tag{8}$$

$$t_{off} = \frac{Q}{I_{Goff}} \tag{9}$$

sendo as corrente de gate determinadas por (10) e (11),

$$I_{Gon} = (V_{DR} - V_{PL})/(R_G + R_{Gint})$$

(10)

$$I_{Goff} = V_{PL}/(R_G + R_{Gint}) \tag{11}$$

onde  $V_{DR}$  é a tensão de *gate* e  $R_{Gint}$  é a resistência de *gate* intrínseca ao transistor (também utilizada em [8]). Definidos estes fatores, a potência dissipada por *overlap* no transistor pode ser encontrada por (4) como uma função da frequência de comutação. Então, A potência total dissipada é obtida pelo

somatório de (3) e (4), como mostra (12),

$$P_{TOT} = P_C + P_{SW}. (12)$$

## IV. VALIDAÇÃO DO MODELO E ANÁLISE COMPARATIVA

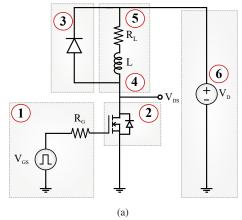

Para validar os resultados o circuito de teste mostrado na Figura 7 foi projetado. Este circuito é utilizado como teste de pulso duplo em [5], [19], e [21], com o objetivo de obter as formas de onda de tensão e corrente e integrá-las em função do período. Nesta validação o circuito opera em regime permanente e equilíbrio térmico. Este fator elimina os transitórios térmicos no MOSFET, e a temperatura no transistor pode ser considerada uniforme [27].

Pela temperatura, as perdas totais são obtidas, utilizando a resistência térmica de cada MOSFET. Os MOSFETs testados foram os *part numbers* IPW60R040C7(SJ) e o IRFP260N(Si), operando com 50 % da tensão de bloqueio máxima (*V*<sub>DSb</sub>) do respectivo MOSFET. Para minimizar os efeitos de recuperação reversa, o diodo de roda livre C3D10060A tecnologia SiC foi utilizado.

Para as medidas térmicas, a câmera térmica Fluke Ti20 foi utilizada. Este equipamento tem precisão de  $\pm$  2 °C ou 2%, o que for maior [28]. A emissividade da câmera for ajustada para 0.9. A temperatura ambiente é constante para cada teste,

Fig. 7. Circuito de teste: (a) diagrama e (b) *setup* experimental. 1) *Gate driver*; 2) dispositivo sob teste; 3) diodo com dissipador; 4) Indutor; 5) Carga resistiva (*bottom side*); 6) Fonte de tensão ajustável  $V_D$  utilizado para manter  $V_{DS}$  constante; 7) *Air cooler*.

e o ambiente laboratorial foi mantido isolado de interferências externas na temperatura, como ventos, brisas, e fontes de calor próximas ao *setup*.

As temperaturas de junção, *case* e dissipador são modeladas em função da potência dissipada no semicondutor (12) [27], [29]. A temperatura de junção pode ser encontrada por,

$$T_J = P_{TOT}R_{\theta JA} + T_A \tag{13}$$

onde  $T_A$  é a temperatura ambiente e  $R_{\theta JA}$  é a resistência térmica entre junção e ambiente.

Como as resistências térmicas de dissipadores são não lineares em função do comprimento, número de aletas, fluxo de ar, altitude, entre outros [27],[29],[30], optou-se por utilizar o transistor sem dissipador de modo a aumentar a exatidão dos resultados térmicos. As perdas totais são obtidas utilizando a temperatura de *case* ( $T_C$ ), temperatura ambiente ( $T_A$ ) e a resistência térmica *case-ambient*  $R_{\theta CA}$  de cada MOSFET.

$$T_C = R_{\theta CA} P_{TOT} + T_A. \tag{14}$$

Os valores de cada  $R_{\theta CA}$  é calculado pelas resistências térmicas fornecidas pelo fabricante: *junction-ambient*  $R_{\theta JA}$  e *junction-case*  $R_{\theta JC}$ .

### A. IPW60R040C7

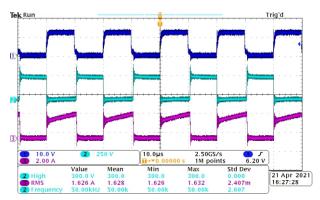

O MOSFET de superjunção IPW60R040C7 é utilizado como exemplo do processo de obtenção do modelo térmico. As resistências térmicas fornecidas pelo fabricante são  $R_{\theta JA}=62~^{\circ}\text{C/W}$  e  $R_{\theta JC}=0.55~^{\circ}\text{C/W}$ , resultando em  $R_{\theta CA}=61.45~^{\circ}\text{C/W}$ . A curva de  $C_{GD}\times V_{DS}$  para este part number foi mostrado na Figura 5. Neste estudo de caso os parâmetros utilizados são os mostrados na Tabela I. Para assegurar o nível de tensão e frequências de comutação corretas, as formas de onda de tensão de gate, tensão de sobre o MOSFET, e corrente RMS no transistor foram medidas com o auxilio de um osciloscópio. Para exemplificação, na Figura 8 são mostradas as formas de onda com o circuito operando a 50 kHz.

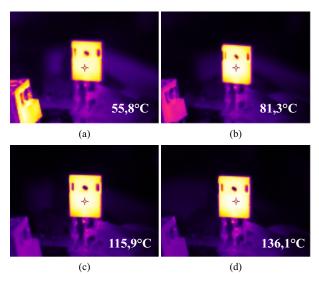

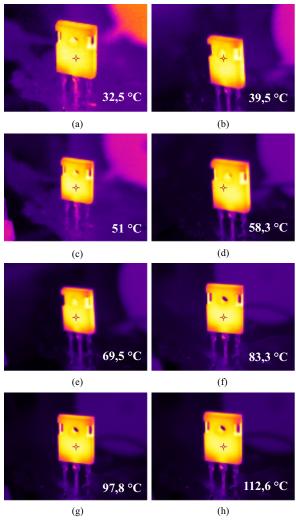

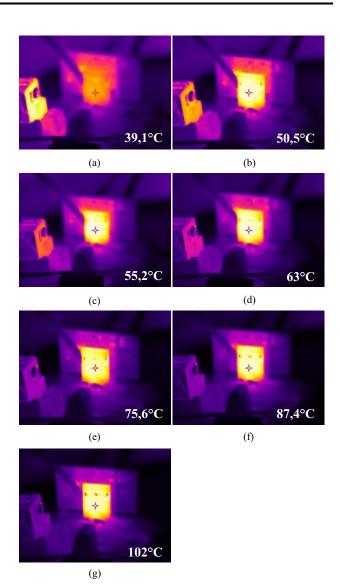

As temperaturas medidas experimentalmente para as frequências de comutação de 20, 50, 90 e 110 kHz, com o air cooler desligado são mostradas na Figura 9. Na Tabela II são comparadas às temperaturas obtidas matematicamente, juntamente aos erros relativos para cada ponto de operação nos modelos analisados. Os parâmetros utilizados nesta validação

Fig. 8. Formas de onda de tensão de *gate*, tensão de sobre o MOSFET, e corrente RMS no transistor com  $F_{SW} = 50 \text{ kHz}$

foram os mostrados na Tabela I.

A Figura 10 apresenta na forma gráfica os dados térmicos mostrados na Tabela II. Os pontos em vermelho representam as temperaturas obtidas experimentalmente. A curva preta a que estão sobrepostos representa um *fitting* desses resultados. Ao exceder a temperatura de 150 °C (limitação térmica do transistor) são mostrados na cor cinza e em formato de traços longos. A partir deste ponto, sistemas de transferência de calor devem se utilizados para evitar a fusão das junções.

Os resultados da Figura 10 mostram que o modelo proposto reproduz com acurácia o comportamento de perdas e temperatura (validação experimental). Isso acontece devido a melhor representação da capacitância Miller em função da tensão de bloqueio, reduzindo significativamente o erro em maiores frequência de comutação. Em menores frequências de comutação (5 kHz, por exemplo) a tendência é que ambos os modelos se aproximem dos resultados experimentais, pois

Fig. 9. Imagens térmicas obtidas com o Fluke Ti20 utilizando o transistor IPW60R040C7 ( $R_{\theta CA}=61.45~^{\circ}\text{C/W}$ ), *air cooler* desligado. (a) 20 kHz. (b) 50 kHz. (c) 90 kHz. (d) 110 kHz.  $T_A=25~^{\circ}\text{C}$ .

Fig. 10. Temperatura de *case* estimada pelos modelos analíticos de [8]–[12], [25], em caparação com as medidas experimentais e com o modelo proposto. Transistor IPW60R040C7,  $R_{\theta CA} = 61.45$  °C/W.  $T_A = 25$  °C.

TABELA II Temperaturas (IPW60R040C7)

| Frequência | Experimental | Modelo proposto | [8]             | [9]             | [10]            | [11]          | [12]            |

|------------|--------------|-----------------|-----------------|-----------------|-----------------|---------------|-----------------|

| 20 kHz     | 55,8°C       | 52,3°C −6,3%    | 136,2°C +144,1% | 131,9°C +136,4% | 104,7°C +87,6%  | 41,4°C −25,8% | 88,3°C +58,2%   |

| 50 kHz     | 81,3°C       | 78,3°C −3,7%    | 298,4°C +267,0% | 283,2°C +248,3% | 215,1°C +164,6% | 58,0°C −28,6% | 169,5°C +108,5% |

| 90 kHz     | 115,9°C      | 112,4°C −3,0%   | 514,7°C +344,1% | 484,8°C +318,3% | 362,2°C +212,5% | 80,2°C −30,4% | 277,7°C +139,6% |

| 110 kHz    | 136,1°C      | 132,7°C −2,5%   | 623,1°C +357,9% | 585,9°C +330,6% | 436,1°C +220,5% | 91,6°C −32,7% | 332,1°C +144,0% |

nessas condições a potência dissipada é majoritariamente resultante das perdas por condução. Como o aumento da frequência de comutação a curva de aumento da temperatura pode ser identificada com proveniente do aumento das perdas por comutação.

Nesta condição os modelos de [8]–[10] sobrestimaram as perdas em toda a faixa de  $F_{SW}$ . Estes modelos utilizam valores de  $Q_{GS}$  e  $Q_{GD}$  diretamente retirados das tabelas do *datasheet*, com exceção de [8], que utiliza a transcondutância para calcular os tempos de *overlap*. De modo geral, estas aproximações são não acuradas pelo fato de as tabelas do *datasheet* representarem um único ponto de operação, para valores específicos de  $V_{DS}$ ,  $R_G$ ,  $V_{GS}$ , não sendo validos para qualquer aplicação.

Além disto, o valor de  $Q_{GD}$  fornecido pelo fabricante, normalmente representa a carga total entre *gate-drain*, representado por  $Q_4$  na Figura 4. Utilizar  $Q_4$  vai contribuir para sobrestimar os tempos de subida e queda da tensão, como ocorre nos modelos de [8]–[10]. O valor apropriado de  $Q_{GD}$  deve ser  $Q_3$ , como exemplificado na Seção III B.

O modelo de [11] utiliza os tempos dos transitórios de corrente  $t_{rise}$  e  $t_{fall}$  das tabelas do datasheet. Similar a  $Q_{GD}$  para os modelos [8]–[10],  $t_{rise}$  e  $t_{fall}$  são fornecidos para um único ponto de operação, resultando na não acurácia do modelo de perdas. A diferença é que, nestas condições, [11] subestima as perdas por comutação. A não acurácia dos modelos de [8]–[11] mostram que os tempos de overlap devem ser estimados utilizando os diagramas de características elétricas do overlap datasheet, possibilitando o ajuste dos parâmetros para o ponto de operação desejado.

Utilizar a curva  $C_{GD} \times V_{DS}$  permite ajustar  $Q_{GD}$  para a aplicação de interesse. Isto é feito em [12], mas o processo de linearização de  $Q_{GD}$  pode ser não acurado, dependendo do *shape* da curva  $C_{GD} \times V_{DS}$ . Como é o caso do MOSFET IPW60R040C7.

#### B. IPW60R040C7 Air Cooler Ligado

Como mencionado, os resultados apresentados nas Figuras 9 e 10 foram obtidos com o *air cooler* desligado. De modo a operar o transistor IPW60R040C7 acima de 110 kHz sem danificar a junção por excesso de temperatura, a  $(R_{\theta JA})$  e desta forma a temperatura de junção, devem ser reduzidas. Isto é possível com o aumento da superfície de dissipador ou pelo aumento do coeficiente de convecção  $(h_c)$ , alterando a convecção natural por convecção forçada [29].

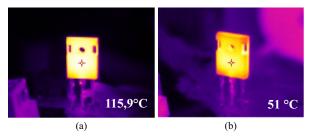

Como não foram incluídos dissipadores no MOSFET sob teste, o *air cooler* mostrado na Figura 7 é utilizado. O *air cooler* foi posicionado perpendicular a superfície do MOSFET com 105 mm de distância. Na Figura 11 é mostrado um comparativo térmico do transistor comutando a 90 kHz, *air cooler* desligado (a) e com *air cooler* ligado (b).

Fig. 11. Comparativo térmico do transistor comutando a 90 kHz: (a) *air cooler* desligado e (b) com *air cooler* ligado.

Com o *air cooler* ligado, a temperatura de *case* em regime permanente diminui de 115,9 °C para 51 °C (Figura 11.a e .b). A utilização de convecção forçada também altera  $R_{\theta CA}$  e  $R_{DSon}$ . Para obter as perdas totais utilizando a temperatura, a resistência térmica resultante da utilização do *air cooler* deve ser determinada.

Aplicando a temperatura da Figura 11.a e rearranjando os termos de (13) e (14), a potência dissipada pode ser determinada,

$$P_{TOT} = \frac{T_C - T_A}{R_{\theta CA}} = \frac{115,9 - 25}{61,45} = 1,479$$

W. (15)

Como a resistência  $R_{\theta CA}$  é muito maior que  $R_{\theta JC}$  a temperatura de junção pode ser aproximada pela temperatura de *case*. Assim, aplicando a temperatura de 115,9 °C em (3), obtém-se a parcela de perdas por condução de 148 mW. Corrigindo a temperatura de 115,9 °C para 51 °C tem-se o equivalente de 105,3 mW de perdas por condução ou 1,436 W de perdas totais. Rearranjando os termos de (15), aplicando a potência dissipada e a temperatura de 51 °C obtém-se o valor  $R_{\theta CA}$  para o experimento com o *air cooler* ligado,

$$R_{\theta CA} = \frac{T_C - T_A}{P_{TOT}} = \frac{51 - 25}{1,436} = 18,1^{\circ}\text{C/W}.$$

(16)

Conhecido o  $R_{\theta CA}$  para o circuito utilizando *air cooler*, novos ensaios térmicos foram realizados, considerando as frequências de comutação de 20, 50, 90, 110, 150, 200, 250 e 300 kHz. As imagens térmicas obtidas são mostradas na Figura 12, as temperaturas na Tabela III e o comparativo gráfico na Figura 13.

Comparativamente, o comportamento dos modelos analíticos na Figura 13 são similares a Figura 10. O modelo proposto estimou a temperatura próximo aos resultados experimentais. Enquanto os modelos de [8]–[12] apresentaram erros significativos com o aumento da frequência, pelas razões discutidas na Seção IV-A.

TABELA III Temperaturas utilizando *air cooler*

| Frequência | Experimental | Modelo proposto | [8]             | [9]              | [10]            | [11]          | [12]             |

|------------|--------------|-----------------|-----------------|------------------|-----------------|---------------|------------------|

| 20 kHz     | 32,5°C       | 32,4°C −0,3%    | 58,9°C +81,1%   | 57,5°C +77,1%    | 49,2°C +52,0%   | 29,8°C −8,3%  | 44,2°C +36,0%    |

| 50 kHz     | 39,5°C       | 40,9°C +3,5%    | 108,3°C +174,3% | 103,7°C +162,4%  | 82,8°C +109,6%  | 34,7°C −12,1% | 68,8°C +74,2%    |

| 90 kHz     | 51°C         | 51,9°C +1,8%    | 174,7°C +242,6% | 165,1°C +223,8%  | 127,5°C +150,2% | 41,2°C −19,3% | 101,7°C +99,4%   |

| 110 kHz    | 58,3°C       | 57,4°C −1,5%    | 207,3°C +255,6% | 195,9°C +236,1%  | 150°C +157,3%   | 44,4°C -23,7% | 118,1°C +102,6%  |

| 150 kHz    | 69,5°C       | 68,2°C −1,8%    | 273,3°C +293,3% | 257,4°C +270,4%  | 194,8°C +180,3% | 50,9°C −26,7% | 151°C +117,3%    |

| 200 kHz    | 83,3°C       | 81,5°C −2.1%    | 355,8°C +327,2% | 334,4°C +301,4%  | 250,8°C +201,2% | 59,1°C −29,1% | 192,2°C +130.7%  |

| 250 kHz    | 97,8°C       | 94,8°C −3,1%    | 438,3°C +348,2% | 411,3°C +320,5%  | 306,9°C +213,8% | 67,3°C −31,2% | 233,3°C +138,54% |

| 300 kHz    | 112,6°C      | 107,9°C −4,7%   | 520,9°C +362,6% | 488,3 °C +333,6% | 363,0°C +222,4% | 75,5°C −33%   | 274,4°C +143,7%  |

Fig. 12. Imagens térmicas obtidas com o equipamento Fluke Ti20, transistor IPW60R040C7 e protótipo de teste utilizando *air cooler* ( $R_{\theta CA} = 18,1^{\circ}\text{C/W}$ ): (a) 20 kHz,(b) 50 kHz, (c) 90 kHz, (d) 110 kHz, (e) 150 kHz, (f) 200 kHz, (g) 250 kHz e (h) 300 kHz.

### C. IRFP260N Air Cooler Desligado

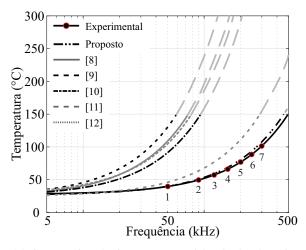

O modelo também foi validado para a tecnologia de Si IRFP260N, utilizando o circuito da Figura 7 com o *air cooler* desligado. Os parâmetros utilizados neste estudo de caso são mostrados na Tabela IV e a modelagem de  $C_{GD}$  é mostrada na Figura 14.

A resistência térmica  $R_{\theta JA}$  do MOSFET IRFP260N é de 40 °C/W e  $R_{\theta JC}$  de 0,5 °C/W resultando no  $R_{CA}$  de 39,5 °C/W. Os resultados térmicos obtidos utilizam a mesma metodologia

Fig. 13. Comparativo térmico entre os modelos de [8], [9], [10], [11] e [12] em relação aos resultados experimentais e ao modelo proposto utilizando o transistor IPW60R040C7 (circuito com *air cooler*) cujo  $R_{\theta CA} = 18.1^{\circ}\text{C/W}$ .

dos ensaios anteriores, portanto o mesmo equacionamento pode ser aplicado. Assim, as temperaturas calculados para cada ponto de frequência de comutação analisada são mostrados na Tabela V, bem como o comparativo na forma gráfica na Figura 15. As imagens térmicas provenientes dos ensaios experimentais são mostradas na Figura 16. A Os pontos de frequências de comutação validados foram: 20, 50, 100, 150, 200, 250 e 300 kHz.

O comportamento dos modelos analíticos mostrados na Figura 15 coincidem com os resultados apresentados nas Figuras 10 e 13. Com o aumento da frequência observa-se o aumento na divergência entre as temperaturas calculadas por cada modelo em relação aos resultados experimentais.

TABELA IV Parâmetros do circuito (IRFP260N)

| Parâmetro                    | Símbolo   | Valor       |  |

|------------------------------|-----------|-------------|--|

| Tensão de ruptura            | $V_{DSb}$ | 200V        |  |

| Tensão de bloqueio           | $V_{DS}$  | 100 V       |  |

| Indutância                   | L         | 1,7 mH      |  |

| Carga                        | R         | 35 Ohm      |  |

| Tensão de gate               | $V_G$     | 15 V        |  |

| Resistência de gate          | $R_G$     | 15 Ohm      |  |

| Corrente Média<br>no indutor | $I_{MED}$ | 1,42 A      |  |

| Duty cycle                   | D         | 0,5         |  |

| Frequência                   | $F_{SW}$  | 5 - 500 kHz |  |

| Transistor                   | #         | IRFP260N    |  |

TABELA V Temperaturas IRFP260N

| Frequência | Experimental | Modelo proposto | [8]             | [9]             | [10]            | [11]           | [12]            |

|------------|--------------|-----------------|-----------------|-----------------|-----------------|----------------|-----------------|

| 50 kHz     | 39,1         | 40°C +2,3%      | 109,3°C +179,5% | 130,4°C +233,5% | 91,5°C +134%    | 46,2°C +18%    | 109,9°C +181,2% |

| 90 kHz     | 50,5         | 50,9°C +0,8%    | 177,6°C +251,7% | 215,2°C +326,1% | 145°C +187,2%   | 63,5°C +25,7%  | 173,4°C +243,4% |

| 110 kHz    | 55,2         | 56,3°C +2,0%    | 211,8°C +283,7% | 257,5°C +366,5% | 171,8°C +211,2% | 72,1°C +30,7%  | 266,1°C +382,1% |

| 150 kHz    | 63           | 67,1°C +6,5%    | 280,1°C +344,6% | 342,2°C +443,1% | 225,2°C +257,5% | 89,4°C +41,9%  | 271,6°C +331,1% |

| 200 kHz    | 75,6         | 80,6°C +6,7%    | 365,5°C +383,5% | 448,1°C +492,6% | 292,1°C +286,4% | 111,1°C +47%   | 353,4°C +367,5% |

| 250 kHz    | 87,4         | 94,2°C +7,8%    | 451°C +416%     | 553,9°C +533,8% | 359,1°C +310,8% | 132,8°C +51,9% | 435,3°C +398%   |

| 300 kHz    | 102          | 108°C +5,8%     | 536,5°C +425%   | 659,9°C +546,9% | 426,1°C +317,7% | 154,6°C +51,5% | 517,2°C +407%   |

Fig. 14. Modelagem da capacitância Miller do transistor IRFP260N (tecnologia Si) utilizando os pontos de extração sugeridos pelo autor (pontos A e B).

Fig. 15. Comparativo térmico entre os modelos de [8], [9], [10], [11] e [12] em relação aos resultados experimentais e ao modelo proposto utilizando o transistor IRFP260N cujo  $R_{\theta CA} = 39,5^{\circ}\text{C/W}$ .

Como discutido no exemplo da Figura 10, os modelos de [8]–[11] estimaram perdas maiores por utilizarem os parâmetros diretamente das tabelas fornecidas na folhas de dados do fabricante. O modelo de [12] superestima  $Q_{GD}$ , resultando em perdas maiores que as medidas experimentalmente. O modelo proposto novamente foi o que apresentou resultados mais próximos às validações térmicas.

Fig. 16. Imagens térmicas obtidas com o equipamento Fluke Ti20 e o transistor IRFP260N ( $R_{\theta CA}=39,5^{\circ}\mathrm{C/W}$ ): (a) 50 kHz,(b) 90 kHz, (c) 110 kHz, (d) 150 kHz, (e) 200 kHz, (f) 250 kHz e (g) 300 kHz.

### V. CONCLUSÃO

Este artigo fornece um modelo analítico para o cálculo de perdas em MOSFETs de potência. O comportamento da resistência drain-to-sourse on-state ( $R_{DSon}$ ) em função da temperatura de junção (modelo de [12]) e a não linearidade da capacitância Miller ( $C_{GD}$ ) em diferentes capacidades de bloqueio de tensão foram considerados. A acurácia do modelo proposto foi validada por resultados térmicos obtidos

experimentalmente.

Na Tabela II e na Figura 10 os resultados foram validados para o MOSFET de superjunção IPW60R040C7 em frequências de até 110 kHz, onde atingiu-se o limite térmico de operação. Na Tabela III e na Figura 13 um *air cooler* foi inserido de modo a reduzir a resistência térmica junção ambiente ( $R_{\theta JA}$ ). A inserção de dissipadores pode trazer erros para o modelo devido às não linearidades em função de comprimento, altitude, fluxo de ar e variação de temperatura. Com a redução da  $R_{\theta JA}$  os resultados utilizando o MOSFET IPW60R040C7 foram validados até 300 kHz, estendendo o *fit* até 500 kHz. Na Tabela V e na Figura 15 os resultados para o MOSFET IRFP260N (tecnologia convencional de Silício) os resultados foram validados até 300 kHz, estendendo o *fit* até 500 kHz.

O modelo proposto demonstrou resultados acurados do em relação aos dados experimentais em todas as verificações realizadas. Devido à relativa facilidade de implementação e acurácia, sua utilização é recomendada em aplicações onde banco de dados são necessários, bem como em avaliações que utilizam soluções por varreduras de pontos de operação.

### **AGRADECIMENTOS**

Os autores gostariam de agradecer ao PPGEE PROEX/CAPES, o projeto INCT-GD e aos órgãos financiadores (CNPq processo 465640/2014-1, CAPES processo no. 23038.000776/2017-54 - Código de Financiamento 001).

### REFERÊNCIAS

- [1] B. Chen, B. Gu, L. Zhang, Z. U. Zahid, J.-S. Lai, Z. Liao, R. Hao, "A high-efficiency MOSFET transformerless inverter for nonisolated microinverter applications", *IEEE Transactions on Power Electronics*, vol. 30, no. 7, pp. 3610–3622, July 2015.

- [2] P. C. Bolsi, H. C. Sartori, J. R. Pinheiro, "Comparison of Core Technologies Applied to Power Inductors", in 2018 13th IEEE International Conference on Industry Applications (INDUSCON), pp. 1100–1106, 2018, doi: 10.1109/INDUSCON.2018.8627236.

- [3] H. C. Sartori, H. L. Hey, J. R. Pinheiro, "An optimum design of PFC Boost Converters", *in 2009 13th European Conference on Power Electronics and Applications*, pp. 1–10, IEEE, 2009.

- [4] Y. Xiao, H. Shah, T. Chow, R. Gutmann, "Analytical modeling and experimental evaluation of interconnect parasitic inductance on MOSFET switching characteristics", in Nineteenth Annual IEEE Applied Power Electronics Conference and Exposition, 2004. APEC'04., vol. 1, pp. 516–521, IEEE, 2004.

- [5] Y. Ren, M. Xu, J. Zhou, F. C. Lee, "Analytical loss model of power MOSFET", *IEEE transactions on* power electronics, vol. 21, no. 2, pp. 310–319, Mar. 2006.

- [6] E. O. Prado, H. C. Sartori, J. R. Pinheiro, "How to select power transistors for static converters applications?", in 2018 13th IEEE International

- Conference on Industry Applications (INDUSCON), pp. 138–143, IEEE, 2018.

- [7] S. Busquets-Monge, J.-C. Crebier, S. Ragon, E. Hertz, D. Boroyevich, Z. Gurdal, M. Arpilliere, D. K. Lindner, "Design of a boost power factor correction converter using optimization techniques", *IEEE Transactions on Power Electronics*, vol. 19, no. 6, pp. 1388–1396, Nov. 2004.

- [8] J. Brown, "Modeling the switching performance of a MOSFET in the high side of a non-isolated buck converter", *IEEE transactions on power electronics*, vol. 21, no. 1, pp. 3–10, Jan. 2006.

- [9] H. C. Sartori, F. Beltrame, H. H. Figueira, J. E. Baggio, J. R. Pinheiro, "Power density comparative analysis concerning to three transistor technologies applied to a CCM PFC BOOST converter using optimization techniques", in 2013 Brazilian Power Electronics Conference, pp. 1317–1323, IEEE, 2013.

- [10] G. Lakkas, "MOSFET power losses and how they affect power-supply efficiency", *Analog Appl*, vol. 10, pp. 22–26, 2016.

- [11] F. Beltrame, F. H. Dupont, H. C. Sartori, E. C. Cancian, C. Rech, J. R. Pinheiro, "Efficiency optimization of DC/DC boost converter applied to the photovoltaic system", in IECON 2013-39th Annual Conference of the IEEE Industrial Electronics Society, pp. 706–711, IEEE, 2013.

- [12] D. Graovac, M. Purschel, A. Kiep, "MOSFET power losses calculation using the data-sheet parameters", *Infineon application note*, vol. 1, 2006.

- [13] R. W. Erickson, D. Maksimovic, *Fundamentals of power electronics*, Springer Science & Business Media, 2007.

- [14] M. H. Rashid, *Power electronics handbook*, Butterworth-Heinemann, 2017.

- [15] D. A. Neamen, Semiconductor physics and devices: basic principles, New York, NY: McGraw-Hill,, 2012.

- [16] K. Seeger, "Semiconductor physics: an introduction. 2004", .

- [17] S. S. Li, "The dopant density and temperature dependence of hole mobility and resistivity in boron doped silicon", *Solid-State Electronics*, vol. 21, no. 9, pp. 1109–1117, Sep. 1978.

- [18] C. Jacoboni, C. Canali, G. Ottaviani, A. A. Quaranta, "A review of some charge transport properties of silicon", *Solid-State Electronics*, vol. 20, no. 2, pp. 77–89, Feb. 1977.

- [19] Y. Xiong, S. Sun, H. Jia, P. Shea, Z. J. Shen, "New physical insights on power MOSFET switching losses", *IEEE Transactions on Power Electronics*, vol. 24, no. 2, pp. 525–531, Feb. 2009.

- [20] T. Piovesan, H. C. Sartori, V. C. Bender, J. R. Pinheiro, "Método para quantificação de perdas em semicondutores aplicados a conversores estáticos devido aos elementos parasitas da placa de circuito impresso", Eletrônica de potência, vol. 26, Mar. 2021.

- [21] X. Huang, Q. Li, Z. Liu, F. C. Lee, "Analytical loss model of high voltage GaN HEMT in cascode configuration", *IEEE Transactions on Power*

- Electronics, vol. 29, no. 5, pp. 2208–2219, June 2013

- [22] H. C. Sartori, J. E. Baggio, H. L. Hey, J. R. Pinheiro, F. Beltrame, "Integrated methodology design to improve the efficiency and reduce volume of the CCM PFC boost converters with pre-sizing settings", in 2015 IEEE 24th International Symposium on Industrial Electronics (ISIE), pp. 1378–1385, IEEE, Oct. 2015.

- [23] P. Lakshmanan, J. Liang, N. Jenkins, "Assessment of collection systems for HVDC connected offshore wind farms", *Electric Power Systems Research*, vol. 129, pp. 75–82, Dec. 2015.

- [24] R. P. Twiname, D. J. Thrimawithana, U. K. Madawala, C. A. Baguley, "A new resonant bidirectional DC– DC converter topology", *IEEE Transactions on power electronics*, vol. 29, no. 9, pp. 4733–4740, Nov. 2013.

- [25] J. Guo, H. Ge, J. Ye, A. Emadi, "Improved method for MOSFET voltage rise-time and fall-time estimation in inverter switching loss calculation", in 2015 IEEE Transportation Electrification Conference and Expo (ITEC), pp. 1–6, IEEE, July 2015.

- [26] W. J. de Paula, G. H. Tavares, G. M. Soares, P. S. Almeida, H. A. C. Braga, "An improved methodology for switching losses estimation in sic MOSFETs", *Eletrônica de potência*, vol. 25, Sep. 2020.

- [27] M. Melito, A. Gaito, G. Sorrentino, "Thermal effects and junction temperature evaluation of Power MOSFETs", in 2017 IEEE East-West Design Test Symposium (EWDTS), vol. 1, p. 141, Nov. 2015.

- [28] Fluke Corporation, *Ti20 Thermal Imager*, Sep 2006, rev. 1.

- [29] On Semiconductor, *Heat Sink Selection Guide for Thermally Enhaced SO8-FL*, Feb. 2015, rev. 1.

- [30] S. Lee, "Optimum design and selection of heat sinks", *IEEE Transactions on Components, Packaging, and Manufacturing Technology: Part A*, vol. 18, no. 4, pp. 812–817, Dec. 1995.

### DADOS BIOGRÁFICOS

Edemar de Oliveira Prado, natural de Frederico Westphalen - RS. Possui graduação em Engenharia Elétrica (2018) e mestrado (2020). Atualmente, é aluno de doutorado em Engenharia Elétrica pela Universidade Federal de Santa Maria

(UFSM) e pela Universidade Federal da Bahia (UFBA). Possui experiência na área de eletrônica de potência, atuando principalmente na área de otimização de transistores aplicados a conversores estáticos, sistemas de transferência de calor e análise física de semicondutores.

Pedro Cerutti Bolsi, natural de Frederico Westphalen - RS. Possui graduação em Engenharia Elétrica (2018) e mestrado (2020). Atualmente, é aluno de doutorado em Engenharia Elétrica pela Universidade Federal de Santa Maria (UFSM) e pela Universidade Federal da Bahia (UFBA). Possui experiência na área de eletrônica de potência, atuando principalmente na área de projeto físico e otimização de dispositivos magnéticos, modelagem de perdas no cobre e núcleo, projeto de filtros e uso de ferramentas FEA.

Hamiltom Confortin Sartori, natural de Marau - RS. Possui graduação em Engenharia Elétrica (2007) na Universidade Federal de Santa Maria, mestrado (2009), doutorado (2013) e pós-doutorado (2016) em Engenharia Elétrica. Atualmente é professor Adjunto de Departamento de Processamento de Energia Elétrica da Universidade Federal de Santa Maria. Possui experiência na área de eletrônica de potência, atuando principalmente nas áreas de projetos otimizados de conversores estáticos, conversores de alto ganho, projetos de componentes magnéticos, semicondutores de potência, sensoriamento e compatibilidade eletromagnética (EMI).

José Renes Pinheiro, recebeu o grau de Eng Eletricista pela UFSM, e os graus de Mestre e Doutor em Engenharia Elétrica pela UFSC, em 1981, 1984, e 1994, respectivamente. È Prof. Titular (Voluntário) do DPEE da UFSM, onde atua desde 1985. Desde 2018, também atua como Prof. Titular Visitante no PPGEE da UFBA. Em 1987, foi um dos fundadores e líder do Grupo de Eletrônica de Potência e Controle (GEPOC). Entre 2006 e 2015 foi coord. do PPGEE da UFSM. Entre 2001 e 2002, realizou pós-doutorado no Center for Power Electronics Systems (CPES), Virginia Tech, EUA. Suas principais linhas de pesquisas e interesse incluem Projetos Otimizados de conversores estáticos, Sistemas Híbridos de conversão estática de energia, Conversão de Energia em Alta Frequência, Modelagem e Controle de Conversores Estáticos e Sistemas Distribuídos de Energia. É membro da SOBRAEP, da SBA, e das Sociedades PELS, IAS, IES e PES da IEEE.