# Mission Profile Emulator for MMC-based Battery Energy Storage Systems

William Caires Silva Amorim<sup>1,2</sup>, João Victor Guimarães França<sup>3</sup>, Allan Fagner Cupertino<sup>4</sup>, Victor Flores Mendes<sup>5</sup>, Heverton Augusto Pereira<sup>3</sup>

<sup>1</sup>Graduate Program in Electrical Engineering, Federal University of Minas Gerais, Belo Horizonte, MG, Brazil <sup>2</sup>Advanced Campus Itabirito, Federal Institute of Education, Science and Technology of Minas Gerais, Itabirito, MG, Brazil

<sup>3</sup>Department of Electrical Engineering, Federal University of Viçosa, Viçosa, MG, Brazil

<sup>4</sup>Department of Electrical Engineering, Federal Center for Technological Education of Minas Gerais, Belo Horizonte, MG,

Brazil

<sup>5</sup>Department of Electrical Engineering, Federal University of Minas Gerais, Belo Horizonte, MG, Brazil

$e-mail:\ william.amorim@ifmg.edu.br, joao.v.franca@ufv.br, afcupertino@ieee.org, victormendes@cpdee.ufmg.br, afcupertino@iee.org, victormendes@cpdee.ufmg.br, afcupertino@iee.org, victormendes@cpdee.ufmg.br, victormendes@cpdee.ufmg.br, victormen$

heverton.pereira@ufv.br

Abstract - In recent years, Modular Multilevel Converters (MMC) have been widely used in medium/high voltage applications, such as high-voltage direct current (HVDC) systems, and pointed out as a promising solution for battery energy storage systems (BESS) and static synchronous compensators (STATCOM), according to recent research. Especially, in BESS application, the current and voltage conditions in the battery bank are fundamental to evaluate thermal dynamic, reliability, and lifetime. However, depending on the voltage and power levels, MMC is based on hundreds of SMs. Thus, the full MMC system implementation can be costly and complex for operational and reliability tests. In this sense, the so-called mission profile emulators (MPE), have been developed to emulate the voltage and current in an SM and batteries. The MPE eliminates the need to implement the full converter and contributes to more agile tests of the MMC dynamics, resulting in the design of more reliable converters. In addition, the MPE can be used to obtain battery current and arm current spectrum similar to those obtained in MMC. This work presents a detailed design and implementation of the MPE for an MMC-based BESS. The MPE is validated in simulations and in a reduced-scale prototype.

*Keywords* – Design Validation, Mission Profile Emulators (MPE), MMC-based BESS, Modular Multilevel Converter (MMC), Testing Scheme.

## I. INTRODUCTION

Modular multilevel converter (MMC) is a promising technology for the next generations of medium/high-power voltage source converters (VSC) [1], [2]. Especially, MMC has favorable characteristics for application in battery energy storage systems (BESS) due to the reduced switching frequency, low harmonic distortion level, reduced passive filters, and ease of state-of-charge (SOC) balancing [3], [4]. The operating reliability of the MMC is important for high-voltage direct current (HVDC) (as presented in recent projects [5]), static synchronous compensators (STATCOM),

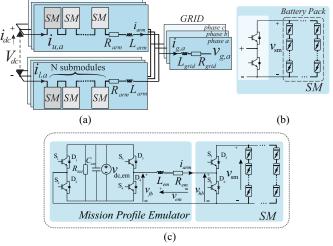

Fig. 1. Basic structure of an MMC-BESS and MPE (a) converter structure (b) SM structure (c) mission profile emulator connected to the SM under test.

and battery energy storage system (BESS) (according to recent research [6], [7]), among others. However, the significant use of submodules (SM) poses challenges to the reliability of capacitors, IGBT modules, and batteries. These components are the most vulnerable in power electronics systems according to industry-based surveys [8], [9]. Electrothermal stress is one of the main mechanisms resulting in SM fatigue and failure [10], [11]. Thus, the validation of the MMC reliability before its operation in the field is crucial [12]. Figure 1.a presents the MMC BESS topology studied in this work. The SM structure, presented in Figure 1.b, is a half-bridge topology. The battery pack is connected to the SM, with series and parallel association to fulfill the power and energy requirements.

Despite the technical advantages, the MMC-BESS implementation is challenging, since the converter contains hundreds or thousands of switching devices, capacitors, and batteries [13], [14]. Thus, studies on the reliability, electrical and thermal aspects of MMC can be extremely costly and require high implementation complexity in a full MMC construction [15], [16]. This is especially important when the BESS application is taken into account. Therefore, mission profile emulators (MPE) play an important role in the simulation of SM, since the MPE can emulate similar voltage and current profiles [17], [18], with the

<sup>&</sup>quot;Manuscript received 09/13/2021; first revision 11/08/2021; accepted for publication 05/02/2022, by recommendation of Editor Marcelo Lobo H eldwein. http://dx.doi.org/10.18618/REP.2022.2.0035"

advantage of a significant reduction of components for implementation [19], [20], [21].

Reference [14] proposes a model-assisted SM test scheme for evaluating the MMC operation in HVDC, STATCOM, among others applications with a full-bridge converter. Reference [22] employs a full-bridge converter to emulate the arm current profile with a circulating current suppression method. In this study, a circulating current suppression method is proposed and evaluated in the emulator operation of inverting and rectifying mode. Authors of [23] develop an MPE with two full-bridge converters to assess the thermal behavior and the reliability of the power modules in the MMC. Reference [24] proposes the use of a novel control scheme for MPE with nearest level control. Reference [25] employs a three-phase MPE for multiple SM in MMC.

The MPE can be used to obtain battery current and arm current spectrum similar to those obtained in MMC. Thus, thermal and degradation studies on the batteries connected in the SM can be performed, without the implementation of the full MMC-BESS. Thus, aspects of the inclusion of batteries in the MPE design, operation during the batteries discharging process, validation of typical battery current spectrum in MMC-BESS, among others are not evaluated in the literature. However, to the best of the authors knowledge, MPE for MMC-based BESS has not been investigated.

This paper fills the aforementioned void, a MPE based on a full-bridge converter is used to emulate the arm current MMC in steady-state, as shown in Figure 1.c. The SM under test is switched in such a way that the battery current harmonic spectra are similar to that observed in MMC-BESS. The proposal is verified through simulations and a reduced scale prototype which validates the proposal experimentally. The rest of this paper is outlined as follows. Section II presents the MPE control strategy and design. Section III presents the case study and the parameters of the simulation and testing scheme. Section IV presents the simulation and experimental results of the MPE. Conclusions are stated in Section V.

## II. MISSION PROFILE EMULATOR CONTROL STRATEGY AND DESIGN

#### A. MPE Parameters

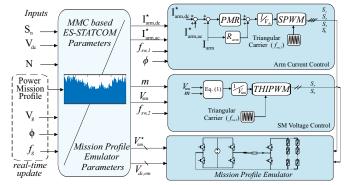

The MPE is composed of a current-controlled full-bridge converter and a coupling inductor. The MMC-BESS parameters and operational conditions are the input variables used to derive the MPE parameters, as shown in Figure 2. Thus, the MMC-BESS parameters, such as nominal power  $(S_n)$ , dc-link voltage  $(V_{dc})$ , number of SM (N), and operational conditions (update in real-time), such as power factor  $(\phi)$ , grid frequency  $(f_g)$  and grid voltage  $(V_g)$  are converted to the MPE parameters: dc arm current reference  $(I_{arm,dc}^*)$ , ac arm current reference  $(I_{arm,ac}^*)$ , SM (under test) voltage reference  $(V_{sm}^*)$ , coupling inductor  $(L_{em})$  and dc supply voltage  $(V_{dc,em})$ .

The MPE output current is regulated by a proportional-integral multi resonant (PIMR) controller. Regarding the modulation strategy, sinusoidal pulse width modulation (SPWM) is employed. The triangular carrier frequency is denoted by  $f_{sw,1}$  in this paper. In addition, the SM voltage control is performed with the third harmonic injection to increase the linear region of the modulator

Fig. 2. Control scheme of the proposed MPE.

[6]. This approach is known as third harmonic injection pulse width modulation (THIPWM). The triangular carrier frequency is denoted by  $f_{sw,2}$ . In the simulation of the full MMC-BESS, the classic equations of the MMC in steady-state are implemented, as presented in [6],[26].

The half-bridge output voltage reference  $(v_{hb}^*)$  used to modulate the SM voltage is related with the equation that relates the arm voltage  $(v_{arm})$  synthesized in the MMC. In this sense, the half-bridge output voltage is given as a function of the full MMC-BESS parameters, without loss of generality, the upper arm of phase *a* is considered in the mathematical modeling. Accordingly [6]:

$$v_{hb}^{*} = \frac{V_{sm}}{2} - m \frac{V_{sm}}{2} \cos(\omega_{g}t) + m \frac{V_{sm}}{12} \cos(3\omega_{g}t),$$

(1)

where  $V_{sm}$  is the SM nominal voltage, *m* is the modulation index, and  $\omega_g$  is the angular grid frequency. The analyses performed are referred to the converter phase *a*, which results in angular displacement equal to zero degree in the  $v_{hh}^*$ .

The circulating current in an MMC for BESS application has a significant second harmonic component that affects the SM voltage ripple and semiconductor losses [6]. In this work, the circulating current control inserts damping in the converter dynamic response through a proportional and resonant controller tuned in the second harmonic. In this sense, the second harmonic current suppression is implemented only in the MMC simulation. The MPE design approach assumes that the circulating current control works properly, i.e., the second harmonic component is suppressed. Thus, the arm current reference in MPE is based on the analytical expression for an arm current in full MMC-BESS [6]. Accordingly:

$$\dot{i}_{arm}^* = \frac{\dot{i}_{dc}}{3} + \frac{\dot{i}_{g,n}}{2}\cos(\omega_g t - \phi_n), \qquad (2)$$

where  $i_{dc}$  is the dc-link current,  $i_{g,n}$  is the amplitude of grid current in the *n*-th converter phase and  $\phi_n$  is the power angle in the *n*-th converter phase. For the decentralized disposal of batteries in the SM of MMC, as presented in Figure 1.a, the  $i_{dc}$  is equal to 0, during MMC balanced operation [27].

#### B. Current Control Parameters Selection

The transfer function that relates the output voltage of the full-bridge  $(V_s)$  with the arm current  $(I_{arm})$  that flows through the MPE coupling inductor is given by:

$$\frac{I_{arm}(s)}{V_s(s)} = \frac{1}{L_{em}s + R_{em}},\tag{3}$$

where  $L_{em}$  is the MPE inductance and  $R_{em}$  is the resistance of MPE inductance. Therefore, the open-loop transfer function  $(G_i(s))$  is given by:

$$G_i(s) = \left(k_p + \frac{k_i}{s} + \frac{k_{r,1}}{s^2 + \omega_{r,1}^2} + \frac{k_{r,2}}{s^2 + \omega_{r,2}^2}\right) \frac{1}{sT_{sw,MPE} + 1} \frac{1}{sL_{em} + R_{em}},$$

(4)

where  $k_p$ ,  $k_i$  and  $k_r$  are the proportional, integral and resonant gain, respectively,  $T_{sw,MPE}$  is the switching period of the MPE and  $\omega_n$  is the resonant frequency. The implementation delay caused by the modulator and sampling the arm current is considered as a first-order transfer function (for a double updated acquisition,  $\tau = T_{sw,MPE}$ ). The proportional, integral, and resonant gains are computed based on [28], [29], which proposes to maximize the control bandwidth based on the phase margin ( $\phi_{pm}$ ). This methodology leads to the following tuning formulas:

$$k_p = \frac{L_{em}(\frac{\pi}{2} - \phi_{pm})}{T_{sw,MPE}},\tag{5}$$

$$k_i = \frac{10R_{em}f_{sw,MPE}}{3},\tag{6}$$

$$k_{r,1} = k_{r,2} = \frac{k_p(\frac{\pi}{2} - \phi_{pm})}{2 \times 10 \times T_{sw,MPE}}.$$

(7)

A phase margin of  $\phi_{pm} = 60$  degrees is assumed for the implementation of arm current control in both simulation and experiments.

Assuming that typical frequency of MMC is in the range of 150-2000 Hz [5], [23], the MPE requires switching frequencies in the order of 1.5 kHz to 20 kHz. In this way, the maximum value found in the typical frequency of the MMC is adopted. Thus, the disturbances caused by the commutation of the SM converter do not affect the control of the average arm current.

#### C. MPE Coupling Inductance Design

The design of the MPE coupling inductor is based on the maximum current ripple present in the arm current emulated by the full-bridge converter. In this sense, a relationship between the time that the semiconductors devices are turned on in the full-bridge converter ( $t_{on,1}$  and  $t_{on,3}$ ) and in the SM under test ( $t_{on,5}$ ) can be derived to estimate the maximum ripple magnitude.

Figure 3 shows the estimated arm current ripple obtained for the instants where the SM is bypassed ( $S_5$  OFF), as presented in Figures 3.a and 3.c, and the instants where the SM is inserted ( $S_5$  ON), as presented in Figures 3.b and 3.d. Additionally, the Figure 3 details the situation where  $d_1 > d_3$ , as presented in Figures 3.a and 3.b, and  $d_1 < d_3$ , as presented in Figures 3.c and 3.d.

According to Figures 3.a and 3.c, the current derivative is negligible in the situation where the state of switches  $S_1$  and  $S_3$  are both high or low. Furthermore, the considerable inductor current ripple is defined for the instant where the emulator dc-link is inserted, being submitted to the emulator dc-link voltage and limited by the MPE coupling inductor.

In a similar way, the analysis can be performed for the instants where the SM is inserted. In this situation, zero current variation does not occur due to the voltage difference between the emulator dc-link voltage and SM voltage. The maximum derivative is defined for the instant when the SM and the dc-link emulator is inserted, leading to the maximum ripple magnitude [24].

The duty cycle of full-bridge converter ( $d_1$  and  $d_3$ , related with switch  $S_1$  and  $S_3$ , respectively) and SM under test ( $d_5$ , related with switch  $S_5$ ) can be defined by:

$$d_1 = \frac{t_{on,1}}{T_{sw,MPE}}, \ d_3 = \frac{t_{on,3}}{T_{sw,MPE}} \text{ and } d_5 = \frac{t_{on,5}}{T_{sw,SM}},$$

(8)

where  $t_{on,3}$  is the time that the switch  $S_3$  are turned on,  $t_{on,5}$  is the time that the switch  $S_5$  are turned on,  $T_{sw,MPE}$  is the switching period of the switch  $S_1$  and  $S_3$  and  $T_{sw,SM}$  is the switching period of the switch  $S_5$ . Additionally, the MPE global duty cycle  $(d_{em})$  can be defined as the relationship

Fig. 3. Switch state of full-bridge and half-bridge converter and generated arm current. (a) SM bypassed and  $d_1 > d_3$  (b) SM inserted and  $d_1 > d_3$  (c) SM bypassed and  $d_1 < d_3$  (d) SM inserted and  $d_1 < d_3$ .

between emulator dc-link and SM voltage:

$$d_{em} = \frac{V_{dc,em}}{V_{sm}}.$$

(9)

The relationship between the MPE global duty cycle and the duty cycle of full-bridge converter can be given as a function of the derivative of the arm current, the SM voltage, and emulator dc-link voltage. Accordingly:

$$d_1 - d_3 = \left(V_{sm} + L_{arm}\frac{di_{arm}}{dt}\right)\frac{1}{V_{dc,em}} = d_{em} + \frac{L_{arm}}{V_{dc,em}}\frac{di_{arm}}{dt}.$$

(10)

The maximum ripple magnitude is defined as the maximum difference between the reference arm current and the arm current generated due to inserting/bypassing the emulator dc-link. Thus, based on Figure 3, four situations of maximum ripple magnitude can de be considered:

$$\Delta I_{arm} = max \left( \Delta I_{arm,1}, \Delta I_{arm,2}, \Delta I_{arm,3}, \Delta I_{arm,4} \right).$$

(11)

Once the switching frequency of the full-bridge converter is assumed to be higher than the SM under test ( $f_{sw,MPE} \gg f_{sw,SM}$ ), the maximum arm current ripple can be computed considering the instant where the SM and the dc-link emulator are inserted, leading to a greater deviation of the arm current, in relation to the reference arm current, as shown in Figure 3.b. In addition, the maximum current ripple (illustrated by  $\Delta I_{arm,2}$ ) occurs at approximately half of the switching period of the full-bridge converter, as discussed in [24]. Accordingly:

$$\Delta I_{arm} = \Delta I_{arm,2} \approx \left(\frac{V_{dc,em} - V_{sm}}{L_{arm}} - \frac{di_{arm}}{dt}\right) \frac{d_1 - d_3}{2f_{sw,MPE}}.$$

(12)

Rearranging the terms of (12) and replacing the relation (10) in (12), the following relation is obtained:

$$\Delta I_{arm} \approx \left[1 - (d_1 - d_3)\right] (d_1 - d_3) \frac{V_{dc,em}}{2L_{em} f_{sw,MPE}}.$$

(13)

In this sense, the emulator inductance  $(L_{em})$  is obtained by rearranging the terms in (13):

$$L_{em} \approx [1 - (d_1 - d_3)] (d_1 - d_3) \frac{V_{dc,em}}{2\Delta I_{arm} f_{sw,MPE}}.$$

(14)

In addition, it is noteworthy that the other cases of arm current variations ( $\Delta I_{arm,1}$ ,  $\Delta I_{arm,3}$  and  $\Delta I_{arm,4}$ ), despite imposing a higher rate in nominal terms, occur in events with times shorter than the situation presented in  $\Delta I_{arm,2}$ , according to [24].

The dc-link voltage emulator must be set considering the voltage level of the SM, as well as the voltage drop in the semiconductor devices and the maximum values of di/dt values imposed by the MPE [19]. Accordingly:

$$v_{dc,em} \ge v_{sm} + L_{em}\omega_g I_{arm} + R_{em}I_{arm} + 3V_{IGBT}, \qquad (15)$$

where  $I_{arm}$  is the peak of arm current and  $V_{IGBT}$  is the collector-emitter voltage of IGBTs.

The maximum current ripple is defined for the instant where the derivative of the equation obtained in (14), in relation to  $d_1 - d_3$ , is equal to zero. Thus, for the instants which  $d_1 - d_3 = 0.5$ , the  $L_{em}$  is defined.

#### **III. CASE STUDY**

#### A. MMC-BESS and MPE Simulation

The performance of the MPE is compared with a full MMC-BESS system simulation of 25 MVA/33 kV and 75 MWh of BESS [7]. The grid frequency is equal to 60 Hz and the MMC is considered an arm inductance of 34.7 mH (0.15 pu). The nearest level control (NLC) for SM voltage balancing is implemented in the full MMC-BESS simulation [5]. The simulation results are developed on the PLECS platform and consider the implementation delay due to the acquisition of the current signal of the MPE inductor. The main parameters for the MMC-BESS simulation are shown in Table I.

| TABLE I                                           |

|---------------------------------------------------|

| Main System Parameters of the MMC-BESS Simulation |

| Parameters                         | Symbol     | Value |

|------------------------------------|------------|-------|

| Rated apparent power [MVA]         | Sn         | 25    |

| Rated reactive power [Mvar]        | $Q_n$      | 25    |

| Rated active power [MW]            | $P_n$      | 25    |

| Total energy storage [MWh]         | $E_n$      | 75    |

| Output voltage (line to line) [kV] | $V_g$      | 33    |

| dc-link voltage [kV]               | $V_{dc}$   | 56    |

| Grid frequency [Hz]                | $f_g$      | 60    |

| Arm inductance [mH]                | Larm       | 15.11 |

| Number of SMs per arm              | Ν          | 30    |

| Nominal SM voltage [kV]            | $V_{sm}^*$ | 1.87  |

In addition, the main system parameters used in the MPE simulation are shown in Table II, considering the same ratings of the SM voltage, grid frequency, arm current and arm inductance observed in the full MMC-BESS system simulation.

TABLE II Main System Parameters of the MPE Simulation (based on full MMC-BESS simulation)

| Parameters                           | Symbol              | Value |

|--------------------------------------|---------------------|-------|

| Peak ac arm current [A]              | I <sub>arm,ac</sub> | 309.2 |

| Maximum arm current ripple [%]       | $\Delta I_{arm,\%}$ | 10    |

| MPE arm inductance [mH]              | $L_{em}$            | 15.11 |

| Switching frequency of the MPE [kHz] | f <sub>sw.MPE</sub> | 20    |

| Switching frequency of the SM [kHz]  | f <sub>sw.SM</sub>  | 2     |

| Grid frequency [Hz]                  | $f_g$               | 60    |

| Nominal SM voltage [kV]              | $V_{sm}^*$          | 1.87  |

| Emulator dc-link voltage [kV]        | $V_{dc,em}$         | 2.9   |

#### B. MPE Setup

The MPE results are obtained considering the same SM nominal voltage, grid frequency, battery arrangement, and nominal arm current, for experimental and simulated results. The results consider a reduced scale prototype, as presented in Table III. The validations for the arm current and battery current are based on the spectrum current and the maximum arm current ripple.

TABLE III Main System Parameters of the MPE in Experimental and Simulation Results

| Parameters                                | Symbol              | Value  |

|-------------------------------------------|---------------------|--------|

| Peak ac arm current [A]                   | I <sub>arm,ac</sub> | 1      |

| Maximum arm current ripple [%]            | $\Delta I_{arm,\%}$ | 17.12  |

| Arm inductance [mH]                       | $L_{em}$            | 7.3    |

| Arm induc. internal resistance $[\Omega]$ | $R_{em}$            | 1.1    |

| MPE Switching frequency [kHz]             | $f_{sw,MPE}$        | 20     |

| SM Switching frequency [kHz]              | $f_{sw,SM}$         | 2      |

| Sampling frequency [kHz]                  | $f_s$               | 40     |

| Grid frequency [Hz]                       | $f_g$               | 60     |

| Power devices (IKP20N60H3)[A/V]           | $S_{1-6}, D_{1-6}$  | 40/600 |

| Nominal SM voltage [V]                    | $V_{sm}^*$          | 12     |

| Emulator dc-link voltage [V]              | $V_{dc,em}$         | 20     |

| Battery (12MN63) voltage [V]              | $V_{bat}$           | 12     |

| Battery internal resistance [mΩ]          | $R_{bat,em}$        | 7      |

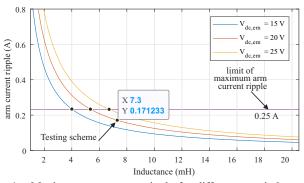

Fig. 4. Maximum arm current ripple for different arm inductance and emulator dc-link voltage.

The design of the coupling inductor considers a limit of maximum arm current ripple of 25%. In this sense, the testing scheme employed in this work adopted an inductance of 7.3 mH (with a 1.1  $\Omega$  of internal resistance) leading to a maximum arm current ripple of 17.12% (for  $V_{dc,em} = 20V$ ), according to (14). Figure 4 shows the maximum arm current ripple derived from (14) for different values of emulator dc-link voltage and arm inductance, highlighting the design point employed in the testing scheme.

The switching frequency of the MPE and SM is equal to 20 kHz and 2 kHz, respectively. The experimental setup used to develop this research considers the operation of the MPE with arm current control, for validation of the SPWM operating with a switching frequency of 20 kHz.

Based on the MPE parameters presented in Tab. II and III, the PIMR controller parameters are calculated for the MPE with full MMC-BESS parameters and testing scheme, as presented in Tab. IV, respectively.

TABLE IV PIMR Controllers Parameters

| Gains for MPE in full MMC-BESS                 | Value              |

|------------------------------------------------|--------------------|

| Proportional gain $(k_p)$                      | 25.4               |

| Integral gain $(k_i)$                          | $7.8 	imes 10^3$   |

| Resonant gain $(k_{r,1} \text{ and } k_{r,2})$ | $2.33 \times 10^3$ |

| Gains for MPE in testing scheme                | Value              |

| Proportional gain $(k_p)$                      | 100.5              |

| Integral gain $(k_i)$                          | $7.3 	imes 10^4$   |

| Resonant gain $(k_{r,1} \text{ and } k_{r,2})$ | $1.05 \times 10^5$ |

Eletrôn. Potên., Florianópolis, v. 27, n. 2, p. 177-185, abr./jun. 2022

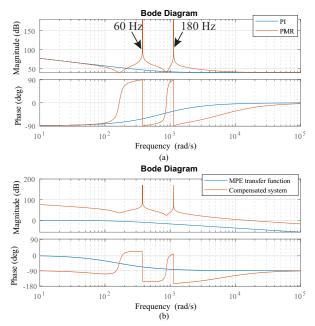

Figure 5.a shows the bode diagram for the traditional PI controller and the employed PIMR controller (based on equation (4)), highlighting the resonance frequencies used in the PIMR controller (1-*st* and 3-*rd* harmonics). In addition, the bode diagram for the open-loop MPE transfer function and the resulting compensated system (based on equation (3) and  $(3) \times (4)$ , respectively) is presented in Figure 5.b.

Fig. 5. (a) Bode diagram of traditional PI controller and the employed PIMR controller (b) Bode diagram of the open-loop MPE system and the compensated system.

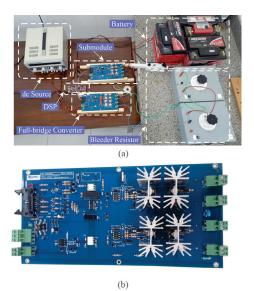

Fig. 6. (a) Experimental setup. (b) Top view of the PCB used to develop the MPE and SM.

Figure 6.a presents the experimental setup developed in this work, highlighting the connection between MPE, SM, dc source, DSP, and bleeder resistor ( $R_{bld}$ , used to discharge the output capacitor of MPE unidirectional power supply). In addition, the PCB developed for the operation of the full-bridge converter and SM is presented in Figure 6.b.

The control algorithm is programmed in the Texas

Instruments TMS320F28379D digital-signal-processor. The dc power supplier FA-3050 supplies the voltage of the full-bridge dc-side. The voltage and current measurements are obtained from a Tektronix DPO 2014B oscilloscope equipped with A612 and P5200 A probes.

The analyses carried out consider the discharge process of a 12 V battery with a peak discharging current of 1 A. In addition, the control dynamics is evaluated with a step in the reference of arm current from 0.1 A to 1.5 A.

#### **IV. RESULTS**

## A. MMC-BESS and MPE Simulation

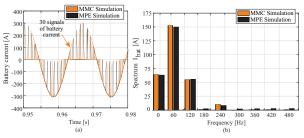

Figure 7.a shows the arm current obtained from the full MMC-BESS and MPE simulation. The arm current reference is set to an amplitude of 309.2 A, in both simulations. Figure 7.b shows that the maximum value of the coupling inductor current ripple is equal to 28.6 A, which corresponds to 9.25% of the arm current reference peak (considering a maximum arm current of 309.2 A).

Fig. 7. (a) Dynamic behavior of the arm current (b) arm current ripple (c) spectrum of arm current.

Based on the spectrum of the arm current, shown in Figure 7.c, it observed that the harmonic contents of both currents are similar, evidencing a purely ac signal (with emphasis on the fundamental component). In addition, a low level of total harmonic distortion (THD) is observed in both simulations.

Figure 8.a shows the current measurements in the SMs of the MMC upper arm, as well as the battery current measured in the MPE. Once the full MMC-BESS simulation implements all the SMs of the MMC, the 30 signals of battery current in the upper arm of phase A are presented.

Figure 8.b shows the average current spectrum of the 30 battery current signals with the current spectrum measured in the MPE simulation. The harmonic content of the battery current for both models are similar, especially for the most significant components dc,  $1^{st}$ ,  $2^{nd}$  and  $4^{th}$  order. Furthermore, the result shows that even using different modulation techniques (NLC, for full MMC simulation and PWM, for the MPE), the low-frequency spectral content is

Fig. 8. (a) Dynamic behavior of the battery current in SM (b) spectrum of battery current.

well represented by the emulator.

## B. Experimental Results - proof of concept

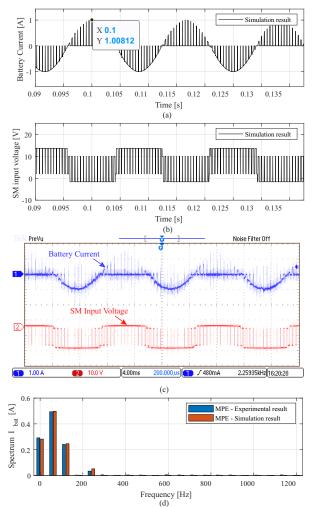

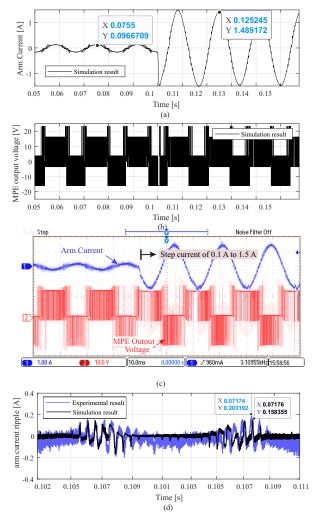

Figures 9.a and 9.b presents the battery current and SM input voltage, respectively, during the battery discharging process for an arm peak current of 1 A, from the MPE simulation with the same parameters of the experimental setup.

Fig. 9. (a) Battery current from simulation. (b) SM input voltage from simulation. (c) experimental waveforms of the SM input voltage [10 V/div], arm current [1 A/div] and time division of 100 ms/div. (d) spectrum of experimental and simulation battery current.

The difference observed between the upper and lower level in the SM input voltage is due to the collector-emitter saturation voltage in the IGBT ( $V_{CEsat} \approx 1.95V$ ) and diode

forward voltage ( $V_F \approx 1.65V$ ). A similar effect will be observed for the MPE output voltage. Figure 9.c shows the experimental waveforms of the SM input voltage and battery current during the discharging process for arm current peak of 1 A.

Figure 9.d presents the battery current spectrum for the simulated and experimental system. The harmonic content of the battery current for the two models is similar, especially for the most significant components of dc,  $1^{st}$ ,  $2^{nd}$ , and  $4^{th}$  order, with amplitude error lower than 10%.

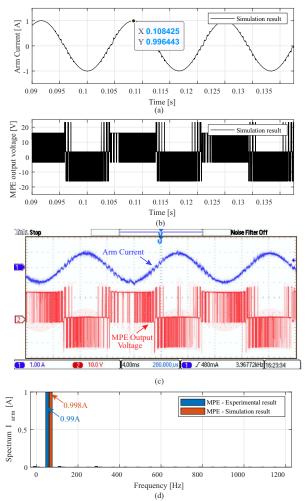

Figures 10.a and 10.b presents the arm current and MPE output voltage, respectively, during the battery discharging process for an arm peak current of 1 A, from the MPE simulation.

Fig. 10. (a) Arm current from simulation. (b) MPE output voltage from simulation. (c) experimental waveforms of the full-bridge output voltage [10 V/div], arm current [1 A/div] and time division of 100 ms/div. (d) spectrum of experimental and simulation arm current.

Figure 10.c shows the experimental waveforms of the MPE output voltage and arm current during the discharging process for an arm current peak of 1 A. Figure 10.d presents the arm current spectrum for the simulated and experimental system. The harmonic content of the battery current for the two models is similar, especially for the fundamental component, where the  $1^{st}$  amplitude is equal to 0.99 A to the testing scheme and equal to 0.998 A for the simulation result, resulting in

an error lower than 1%. Some high-order components, in the range of 200 - 1200 Hz, are verified in the experimental signal spectrum, but with negligible amplitudes.

Fig. 11. (a) Arm current from simulation. (b) MPE output voltage from simulation. (c) Experimental waveforms of the MPE output voltage [10 V/div], arm current [1 A/div] (for step of arm current) and time division of 100 ms/div. (d) arm current ripple for experimental setup for one fundamental cycle.

Finally, Figures 11.a and 11.b present the arm current and MPE output voltage, respectively, for a variation of arm current peak of 0.1 A to 1.5 A. Figure 11.c shows the arm current control dynamic behavior for a step in the arm current amplitude from 0.1 A to 1.5 A. The waveforms presented are the MPE output voltage and the MPE output current. As verified, the peak of the output current ranges from 0.1 A to 1.5 A, for a 60 Hz sinusoidal reference current. Figure 11.d shows the arm current ripple with a maximum peak value of 0.203 A, for the experimental result, and 0.158 A, for the simulation result. The maximum arm current ripple is computed by nulling the fundamental component of the Fourier transform of the measured current of the arm. Thus, to obtain the ripple signal of the arm current, the inverse Fourier transform is performed. Tab. V presents a summary of the obtained maximum arm current ripple values and their respective errors for experimental and simulation results. The experimental arm current ripple shows an error of 18.66% and the simulated arm

current ripple, an error of 7.52%.

TABLE V

Maximum Arm Current Ripple Results

| Method                          | Current Ripple [A] | Error [%]) |

|---------------------------------|--------------------|------------|

| Theoretical Analysis - Eq. (13) | 0.17123            | -          |

| Simulation Result               | 0.15835            | 7.52       |

| Experimental Result             | 0.203192           | 18.66      |

## V. CONCLUSION

In this paper, a methodology for the model and design of an MPE was evaluated in terms of control dynamics and maximum arm current ripple with a full-bridge converter. The MPE design was evaluated using simulation and experimental results, which validated the ability to reproduce the characteristic waveforms of an MMC-BESS. The developed design of the MPE coupling inductor was supported by analytical expressions of the maximum arm current ripple among the full-bridge converter and half-bridge converter.

The experimental results indicated that the converter dynamics with the design implemented is suitable for emulating SM steady-state waveforms of MMC-BESS during the battery discharging process. The arm current transient is smooth and does not significantly affect the converter dynamics. Furthermore, the results showed that the estimated maximum arm current ripple shows good agreement with the approximation to design MPE coupling inductor. In addition, the spectrum of arm and battery current showed that the harmonic content of these signals is similar among the experimental and simulation results, according to the typical current spectrum observed in the MMC-BESS.

## ACKNOWLEDGEMENTS

The authors would like to thank the Brazilian agencies CAPES, CEMIG (D722), CNPq, and FAPEMIG (APQ-02556-21) by funding.

## REFERENCES

- [1] S. Debnath, J. Qin, B. Bahrani, M. Saeedifard, P. Barbosa, "Operation, Control, and Applications of the Modular Multilevel Converter: A Review", *IEEE Trans on Power Electr*, vol. 30, no. 1, pp. 37–53, mar. 2015.

- [2] Y. Xuan, X. Yang, "A novel circuit topology for the VSC-HVDC submodules testing", *in IFEEC ECCE Asia*, pp. 1435–1439, oct. 2017.

- [3] C. A. Bharadwaj, S. Maiti, "Modular multilevel converter based hybrid energy storage system", *IEEE PES APPEEC*, pp. 1–6, mar. 2017.

- [4] G. Wang, G. Konstantinou, C. D. Townsend, J. Pou, S. Vazquez, G. D. Demetriades, V. G. Agelidis, "A Review of Power Electronics for Grid Connection of Utility-Scale Battery Energy Storage Systems", *IEEE Trans on Sustain Energy*, vol. 7, no. 4, pp. 1778–1790, jul. 2016.

- [5] K. Sharifabadi, L. Harnefors, H. Nee, S. Norrga, R. Teodorescu, "Design, Control, and Application

of Modular Multilevel Converters for HVDC Transmission Systems", *Wiley - IEEE*, jan. 2016.

- [6] A. F. Cupertino, J. V. Farias, H. Pereira, S. I. Seleme, R. Teodorescu, "DSCC-MMC STATCOM Main Circuit Parameters Design Considering Positive and Negative Sequence Compensation", *J of Control, Autom and Electr Syst*, vol. 29, pp. 62–74, nov. 2018.

- [7] J. Gherard, W. Amorim, A. F. Cupertino, H. A. Pereira, S. I. Seleme, R. Teodorescu, "Optimum Design of MMC-based ES-STATCOM Systems: The Role of the Submodule Reference Voltage", *IEEE Trans on Ind Appl*, pp. 1–1, may 2020.

- [8] F. Mohamad, J. Teh, "Impacts of Energy Storage System on Power System Reliability: A Systematic Review", *Energies*, vol. 11, no. 7, jul. 2018.

- [9] H. Wang, M. Liserre, F. Blaabjerg, "Toward Reliable Power Electronics: Challenges, Design Tools, and Opportunities", *IEEE Industrial Electronics Magazine*, vol. 7, no. 2, pp. 17–26, jun. 2013.

- [10] Y. Zhang, H. Wang, Z. Wang, Y. Yang, F. Blaabjerg, "Impact of lifetime model selections on the reliability prediction of IGBT modules in modular multilevel converters", *in ECCE*, pp. 4202–4207, nov. 2017.

- [11] Y. Zhu, K. Ma, X. Cai, "Thermal Characterization Method of Power Semiconductors Based on H-Bridge Testing Circuit", *IEEE Trans on Power Electr*, vol. 34, no. 9, pp. 8268–8273, feb. 2019.

- [12] F. Hahn, M. Andresen, G. Buticchi, M. Liserre, "Mission Profile Based Reliability Evaluation of Building Blocks for Modular Power Converters", *in PCIM Europe*, pp. 1–7, may. 2017.

- [13] N. Ahmed, L. Ängquist, S. Norrga, A. Antonopoulos, L. Harnefors, H. Nee, "A Computationally Efficient Continuous Model for the Modular Multilevel Converter", *IEEE J of Emerg and Sel Topics in Power Electron*, vol. 2, no. 4, pp. 1139–1148, jun. 2014.

- [14] Y. Tang, L. Ran, O. Alatise, P. Mawby, "A Model Assisted Testing Scheme for Modular Multilevel Converter", *IEEE Trans on Power Electron*, vol. 31, pp. 165–176, mar. 2016.

- [15] Y. Tang, O. Alatise, L. Ran, P. Mawby, "Improved Testing Capability of the Model-Assisted Testing Scheme for a Modular Multilevel Converter", *IEEE Trans on Power Electron*, vol. 31, pp. 7823–7836, nov. 2016.

- [16] Y. Yang, K. Ma, Y. Song, W. Wang, "Control and Design of Mission Profile Emulator for Sub-modules in Modular Multilevel Converter", *ECCE*, pp. 4789–4794, nov. 2019.

- [17] S. Jiang, K. Ma, X. Cai, "Self-Circulating Testing Method for Both Rectifying and Inverting Submodules of Modular Multilevel Converter With Low DC Supply Voltage", *IEEE Trans on Power Electr*, vol. 35, no. 8, pp. 7795–7803, aug. 2020.

- [18] Y. Yang, W. Wang, K. Ma, "Mission-Profile-Based Testing Scheme for Sub-Modules in Modular Multilevel Converter", *IEEJ J of Industry Applic*, vol. 9, no. 3, pp. 219–226, may 2020.

Eletrôn. Potên., Florianópolis, v. 27, n. 2, p. 177-185, abr./jun. 2022

- [19] Z. Wang, H. Wang, Y. Zhang, F. Blaabjerg, "A Viable Mission Profile Emulator for Power Modules in Modular Multilevel Converters", *IEEE Trans on Power Electron*, vol. 34, pp. 11580–11593, mar. 2019.

- [20] Y. Yang, K. Ma, W. Wang, "Mission Profile Emulator for Sub-Modules of Modular Multilevel Converter with Carrier Phase-Shift Modulation", *ICPE 2019 -ECCE Asia*, pp. 1836–1841, aug. 2019.

- [21] J. Tang, Y. Dong, H. Yang, W. Li, X. He, J. Ma, G. Chen, Y. Tian, E. Yang, "An equivalent power test scheme for modular multilevel converters (MMCs)", *mar 2017 IEEE APEC*, pp. 1837–1842, 2017.

- [22] Y. Yang, W. Wang, K. Ma, "Mission-Profile-Based Testing Scheme for Sub-Modules in Modular Multilevel Converter", *IEEJ Journal of Ind Appl*, vol. 9, pp. 219–226, oct. 2020.

- [23] Z. Wang, H. Wang, Y. Zhang, F. Blaabjerg, "A Minimum Viable Mission Profile Emulator for IGBT Modules in Modular Multilevel Converters", *APEC*, pp. 313–318, may 2019.

- [24] S. Jiang, K. G. Ma, Y. Yang, X. Cai, "Mission Profile Emulator for Individual Submodule in Modular Multilevel Converter with Nearest Level Control", *IEEE Trans on Power Electr*, pp. 1–1, mar. 2021.

- [25] K. Ma, S. Jiang, E. Li, X. Cai, "Three-Phase Mission Profile Emulator for Multiple Submodules in Modular Multilevel Converter", *IEEE Trans on Power Electr*, vol. 36, no. 5, pp. 5213–5222, oct. 2021.

- [26] L. Harnefors, A. Antonopoulos, S. Norrga, L. Angquist, H.-P. Nee, "Dynamic Analysis of Modular Multilevel Converters", *IEEE Trans on Industrial Electr*, vol. 60, no. 7, pp. 2526–2537, jul. 2013.

- [27] S. K. Chaudhary, A. F. Cupertino, R. Teodorescu, J. R. Svensson, "Benchmarking of Modular Multilevel Converter Topologies for ES-STATCOM Realization", *Energies*, vol. 13, no. 13, jul. 2020.

- [28] D. G. Holmes, T. Lipo, B. Mcgrath, W. Kong, "Optimized Design of Stationary Frame Three Phase AC Current Regulators", *IEEE Trans on Power Electron*, vol. 24, pp. 2417–2426, nov. 2009.

- [29] R. Peña-Alzola, M. Liserre, F. Blaabjerg, M. Ordonez, Y. Yang, "LCL-Filter Design for Robust Active Damping in Grid-Connected Converters", *IEEE Trans* on Ind Informatics, vol. 10, no. 4, pp. 2192–2203, oct. 2014.

### BIOGRAPHIES

William Caires Silva Amorim, received the B.S. degree in electrical engineering from the Universidade Federal de Viçosa (UFV), Viçosa, Brazil, in 2018. He received the M.S. degree in electrical engineering from Federal Center for Technological Education of Minas Gerais, Belo Horizonte, Brazil, in 2019. In this institution, he carried out research in the area of information theory, with emphasis on Coding Theory by the PICME Program. He has been an EBTT Professor with the Advanced Campus Itabirito, IFMG, since 2022. He was a Substitute Professor with the Department of Electrical Engineering in UFV and a Researcher Assistant with Gerência de Especialistas em Eletrônica de Potência (GESEP). His research interests include power electronics and electrical power systems, with focus in the modular multilevel cascade converters and BESS.

João Victor Guimarães França, Graduating in Electrical Engineering from the Federal University of Viçosa (UFV). He has high school and technical education in Electrotechnics at the Federal Center for Technological Education of Minas Gerais (CEFET-MG). He is currently a Researcher Assistant with Gerência de Especialistas em Eletrônica de Potência (GESEP). He held an internal internship in the Materials Strength laboratory of the civil engineering department for a year, where he developed prototypes for practical classes using electrical strain gauges and Arduino plates.

Allan Fagner Cupertino, received the B.S. degree in electrical engineering from the Federal University of Viçosa, Viçosa, Brazil, in 2013, the M.S. and Ph.D. degrees in electrical engineering from the Federal University of Minas Gerais, Belo Horizonte, Brazil, in 2015 and 2019, respectively. He was a guest Ph.D. with the Department of Energy Technology, Aalborg University from 2018 to 2019. Since 2014, he has been with the Electric Engineering Department, Federal Center of Technological Education of Minas Gerais, where he is currently an Assistant Professor in the area of electric machines and power electronics. His main research interests include renewable power generation systems, multifunctional inverters, MMC and reliability of power electronics based systems. Dr. Cupertino was the recipient of the President Bernardes Silver Medal in 2013. He is a member of the Brazilian Power Electronics Society, IEEE Power Energy, IEEE Power Electronics, and IEEE Industry Applications Society.

<u>Victor Flores Mendes</u>, received the B.E.E. degree in control and automation engineering from the Federal University of Minas Gerais (UFMG), Belo Horizonte, Brazil, in 2008, and the M.E.E. and Ph.D. degrees in electrical engineering from UFMG in 2009 and 2013, respectively. In 2010, he developed part of his thesis with the Dresden University of Technology, Dresden, Germany. He is currently a Professor with UFMG. His main research interests include wind and photovoltaic energy conversion systems, applications and control of power electronics, and power quality aspects of distributed generation grid integration.

Heverton Augusto Pereira, received the B.S. degree from the Federal Federal University of Viçosa (UFV), Viçosa, Brazil, in 2007, the M.Sc. degree from the University of Campinas, Campinas, Brazil, in 2009, and the Ph.D. degree from the Federal University of Minas Gerais, Belo Horizonte, Brazil, in 2015, all in electrical engineering. He was a visiting Researcher from the Department of Energy Technology, Aalborg University, Denmark, in 2014. He has been an Adjunct Professor with the Electric Engineering Department, UFV, since 2009. His main research interests include grid-connected converters for PV and wind power systems, and high-voltage dc/flexible ac transmission systems.