# A SOFT SWITCHING HALF-BRIDGE DOUBLER BOOST CONVERTER OPERATING WITH UNITY POWER FACTOR

Roberto Mendes Finzi Neto<sup>1</sup>, Enes Gonçalves Marra<sup>1</sup>, Fernando Lessa Tofoli<sup>2</sup>, Luiz Carlos de Freitas<sup>2</sup>

Universidade Federal de Goiás<sup>1</sup> Escola de Engenharia Elétrica e de Computação Praça Universitária s/n, Setor Universitário 74605-220 – Goiânia-GO – Brasil Fone/Fax: +55 62 5211806 E-mail: <u>finzi@eee.ufg.br</u>, <u>enes@eee.ufg.br</u>

*Abstract* – This paper proposes a half-bridge doubler boost converter associated with an active commutation cell in order to minimize commutation losses. The converter operates with unity power factor and is able to provide high output voltages. The voltages across the semiconductor devices are low and approximately equal to the output voltage, as doubled output voltages and reduced high frequency ripple can be achieved. A detailed mathematical analysis concerning its operation is presented, since simulation and experimental results describe the converter performance.

*Keywords* – Doubler boost converters, half-bridge converters, PFC, soft switching.

# I. INTRODUCTION

In order to meet the requirements in the proposed standards such as IEC 61000-3-2 and IEEE Std 519 on the quality of the input current that can be drawn by low-power equipment, a power factor correction (PFC) circuit is typically added to the utility interface of an AC–DC switch-mode power supply. The boost PFC circuit operating in continuous conduction mode (CCM) is by far the popular choice for medium and high power (400W to a few kilowatts) application. This is because the continuous nature of the boost converter's input current results in low electromagnetic interference (EMI) compared to other active PFC topologies such as buck-boost and buck converters.

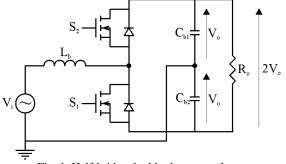

The half-bridge boost topology shown in Fig. 1 requires an additional switch and a additional capacitor, but does not need a diode rectification bridge at the input. Only one semiconductor device conducts at any instant of time, as opposed to three in the boost rectifier, which should lead to higher efficiency. However, the voltage across each semiconductor device is equal to twice the output voltage. An additional advantage is the adjustable power factor, which can vary from -1.0 to +1.0 [1]-[3].

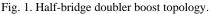

If four diodes are added, the improved topology in Fig. 2 results, as reduced voltages across the semiconductor devices are obtained. This converter is recommended for telecom applications [4] [5] and rectifier/inverter drive systems [6]. It is also employed as PFC front-end stage in a battery charger circuit, associated with a double forward converter [7]. Since the conduction losses in the primary side of isolated converters are inversely proportional to the input voltage, the application of this topology seems prominent.

Universidade Federal de Uberlândia<sup>2</sup> Faculdade de Engenharia Elétrica Campus Santa Mônica – Bloco "3N" Av. João Naves de Ávila, 2160 38400-902 – Uberlândia-MG – Brasil Fone/Fax: +55 34 32394166 E-mail: fernandolessa@pop.com.br, freitas@ufu.br

The requirement of high frequency operation is evident to reduce of the audible noise, the volume and the weight of magnetic elements, as well as to improve output voltage quality. However, at high frequency operation, switching losses and electromagnetic interference (EMI) become significant and must be analyzed in detail. Soft switching aim is to reduce the overlap between voltage and current during the commutation, in order to reduce switching losses, enabling high frequency operation and achieving higher power density.

Within this context, this paper presents a soft-switched half-bridge doubler boost converter, which has prominent advantages e.g. the voltage across each semiconductor is equal to  $V_o$  and the voltage ripple across capacitors  $C_{b1}$  and  $C_{b2}$  is reduced. An active commutation circuit is also described, as soft switching is obtained.

## II. HALF BRIDGE DOUBLER BOOST CONVERTER WITHOUT COMMUTATION LOSSES

Many lossless switching schemes have been proposed so far in order to minimize commutation losses, and they are classified as active or passive.

with reduced voltage stresses.

Manuscript received on February 22, 2005; revised April 19, 2005. Recommended by the Editor José Antenor Pomilio.

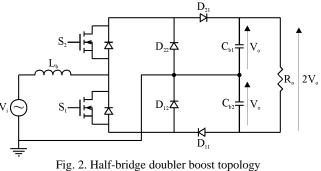

Fig. 3. Half-bridge doubler boost converter associated with the soft commutation circuit.

The work developed in [8] shows results on a boost converter employing passive and active methods, which are eventually compared. It can be seen that passive methods are better recommended for high power application, while active methods present better performance at low power levels. However, the results could not be generalized, and one is supposed to determine which method is more adequate for this topology.

A complete analysis to establish the better choice for this case is rather extensive and is not the scope of the paper. This is the main reason why the resonant circuit proposed by one of the authors in [9] and [10], which demonstrated satisfactory performance in the achievement of soft switching, was adapted to this converter.

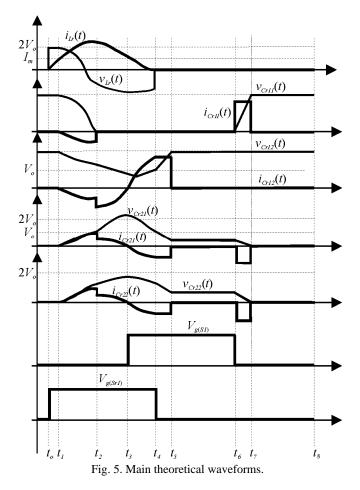

Fig. 3 illustrates the half-bridge doubler boost converter associated with the active auxiliary commutation cell. It is composed of four resonant capacitors  $C_{r11}$ ,  $C_{r12}$ ,  $C_{r21}$  and  $C_{r22}$ , one resonant inductor  $L_r$ , two auxiliary switches  $S_{r1}$  and  $S_{r2}$ , and also two diodes  $D_{r1}$  and  $D_{r2}$ , so that the zero voltage transition in main switches  $S_1$  and  $S_2$  can be obtained. Switches  $S_{r1}$  and  $S_{r2}$  are turned on under ZCS condition. Passive snubbers are associated with the auxiliary diodes in order to minimize parasitic oscillation.

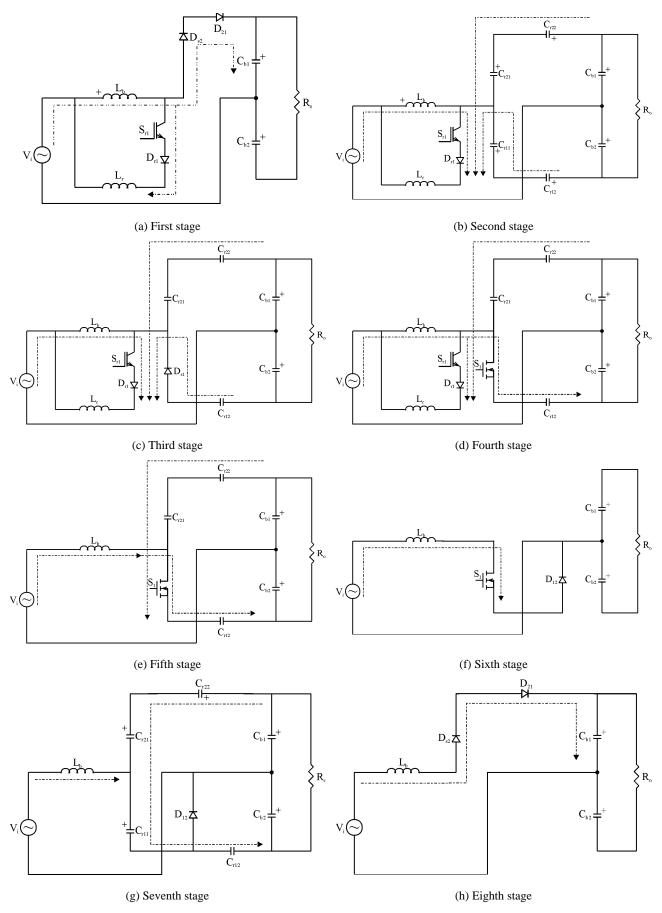

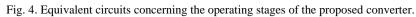

The operating stages are presented in Fig. 4. The analysis focuses only on the positive semicycle of the input voltage, where switches  $S_1$  and  $S_{r1}$  are involved in process, but switches  $S_2$  and  $S_{r2}$  remain turned off. The operation in the negative semicycle is analogous, although the opposite occurs. Fig. 5 shows the main theoretical waveforms necessary to the analysis of the converter operation.

## A. Description of Operating Stages

#### • First stage $[t_0-t_1]$ (Fig. 4 (a)) – First linear stage.

Before instant  $t=t_0$ , diodes  $D_{S2}$  and  $D_{21}$  conduct the boost current  $I_b$  and capacitor  $C_{b1}$  keeps charging. At  $t=t_0$ , switch  $S_{r1}$  is turned on under ZCS mode due to resonant inductor  $L_r$ . The voltage across  $L_r$  remains constant and equal to  $2 \cdot V_o$ , and the current through  $L_r$  increases linearly from null to  $I_m$ , where  $I_m$  is the constant current through the boost inductor. The current through  $D_{S2}$  and  $D_{21}$  decreases linearly as well. This stage finishes when  $i_{Lr}$  equals  $I_m$ , what can be described mathematically according to expression (1).

$$i_{Lr}(t) = \left(V_o - V_i\right) \cdot \frac{1}{L_r} \cdot t \tag{1}$$

The time interval that defines this stage is:

$$\Delta t_1 = \frac{I_m}{\left(V_o - V_i\right)} \cdot L_r \tag{2}$$

#### • Second stage [*t*<sub>1</sub>-*t*<sub>2</sub>] (Fig. 4 (b)) – First resonant stage.

The resonance involving all the resonant capacitors begins when the current through inductor  $L_r$  becomes greater than  $I_m$ . The resonant current  $i_{Lr}(t)$  is divided equally between two resonant networks, which are formed by two capacitor sets i.e.  $C_{r11}$ - $C_{r12}$  and  $C_{r21}$ - $C_{r22}$ . In order to assure the analogous operation of the converter in the negative semicycle, the following assumptions are made:

$$C_{r11} = C_{r21} \tag{3}$$

$$C_{r12} = C_{r22}$$

(4)

$$K = \frac{C_{r11}}{C_{r12}} = \frac{C_{r21}}{C_{r22}}$$

(5)

The behavior of the voltages across the resonant capacitors is:

- $v_{Cr11}(t)$  decreases from  $2 \cdot V_o$  to null;

- $v_{Cr21}(t)$  increases from null to  $V_o$ ;

- $v_{Cr12}(t)$  decreases from  $2 \cdot V_o$  to  $v_{Cr12}(t_2)$ ;

- $v_{Cr22}(t)$  increases from null to  $v_{Cr22}(t_2)$ .

The resonant frequency and the characteristic impedance are given by (6) and (7), respectively.

$$f_o = \frac{1}{2\pi} \cdot \sqrt{\frac{1}{2 \cdot L_r \cdot C_r}} \tag{6}$$

$$Z_o = \sqrt{\frac{L_r}{2 \cdot C_r}} \tag{7}$$

where:

$$C_r = C_{r11} + C_{r12} = C_{r21} + C_{r22}$$

(8)

This stage finishes when the voltage across  $C_{rll}$  is null, and it can be defined according to expressions (9) to (13).

$$i_{Lr}(t) = \frac{2 \cdot (V_o - V_i)}{Z_o} \sin\left(2\pi \cdot f_0 \cdot t\right) + I_m \tag{9}$$

$$v_{Cr11}(t) = V_o - (V_o - V_i) \cdot \frac{K}{1 + K} \cdot [1 - \cos(2\pi \cdot f_0 \cdot t)]$$

(10)

$$v_{Cr12}(t) = V_o - (V_o - V_i) \cdot \frac{1}{1 + K} \cdot \left[1 - \cos(2\pi \cdot f_0 \cdot t)\right]$$

(11)

$$v_{Cr21}(t) = \left(V_o - V_i\right) \cdot \frac{K}{1 + K} \cdot \left[1 - \cos\left(2\pi \cdot f_0 \cdot t\right)\right] \quad (12)$$

$$v_{Cr22}(t) = \left(V_o - V_i\right) \cdot \frac{1}{1 + K} \cdot \left[1 - \cos\left(2\pi \cdot f_0 \cdot t\right)\right]$$

(13)

According to the complete mathematical study of the converter developed in [7], the time interval that defines the second stage is:

$$\Delta t_2 = \frac{1}{2\pi \cdot f_0} \cdot \arccos\left(1 - V_o \cdot \frac{K+1}{K(V_o - V_i)}\right) \quad (14)$$

From (14), it can be seen that the maximum value for  $\Delta t_2$  is  $\pi$  rad. It means that the voltage across resonant capacitor  $C_{r11}$  must decrease to null within this interval to assure soft switching. Therefore the following condition, stated in [7], must be observed:

$$V_o = 2 \cdot V_i + V_x \tag{15}$$

where  $V_x$  is about 10% to 20% of the input voltage.

Additionally, parameter *K* must be greater enough so that the second stage finishes before  $\pi$  rad [7].

$$K > \frac{2 \cdot V_i + V_x}{V_x} \tag{16}$$

## • Third stage [t<sub>2</sub>-t<sub>3</sub>] (Fig. 4 (c)) – Second resonant stage.

When the voltage across capacitor  $C_{r11}$  is null and remains clamped, switch  $S_1$  can be turned on under ZVS condition. Diode  $D_{S1}$  starts conducting and the current through capacitor  $C_{r12}$  increases almost instantly. Since the current through  $C_{r12}$ increases, both currents through  $C_{r21}$  and  $C_{r22}$  must decrease almost instantly. Once resonant inductor  $L_r$  conducts the entire boost current  $I_b$ , switch  $S_1$  is turned on in ZCS mode as well. The behavior of the voltages across the resonant capacitors is:

-  $v_{Cr21}(t)$ : increases from  $V_o$  to  $v_{Cr21}(t_3)$ ;

-  $v_{Cr12}(t)$ : decreases from  $v_{Cr12}(t_2)$  to  $v_{Cr12}(t_3)$ ;

-  $v_{Cr22}(t)$ : increases from  $v_{Cr22}(t_2)$  to  $v_{Cr22}(t_3)$ .

In this stage, there are low voltage stresses across switch  $S_2$ , and it finishes when  $i_{Cr12}(t)=i_{Cr21}(t)=i_{Cr22}(t)=0$  and  $i_{Lr}(t)=I_b$ .

A new resonant frequency and a new characteristic impedance are defined in this stage, according to (17) and (18), respectively.

$$Z_1 = \sqrt{\frac{L_r}{\left(2+K\right) \cdot C_r}} \tag{17}$$

$$f_1 = \frac{1}{2\pi} \cdot \sqrt{\frac{1}{\left(2+K\right) \cdot C_r \cdot L_r}} \tag{18}$$

The expressions that describe this stage mathematically are as follows:

$$i_{Lr}(t) = \begin{bmatrix} \frac{\left(V_o - V_i\right)}{Z_o} \cdot \sqrt{1 - \left(\frac{V_o \cdot \left(K + 1\right)}{K\left(V_o - V_i\right)} - 1\right)^2} \\ + I_m \end{bmatrix} \cdot \cos\left(2 \cdot \pi \cdot f_1 \cdot t\right) \quad (19)$$

$$\frac{-\frac{1}{Z_{1}} \cdot \left(\frac{Y_{o}}{K} + V_{i}\right) \cdot \sin\left(2 \cdot \pi \cdot f_{1} \cdot t\right)}{\left[\frac{\sqrt{4 + 2 \cdot K}}{2 + K} \cdot \right]}$$

(20)

$$v_{Cr12}(t) = \left(V_o - \frac{V_o}{K}\right) - \left[ \left(\frac{(V_o - V_i)}{2} \cdot \sqrt{1 - \left(\frac{V_o \cdot (K+1)}{K \cdot (V_o - V_i)} - 1\right)^2}\right) \right]$$

$$\cdot \sin\left(2 \cdot \pi \cdot f_1 \cdot t\right) + \left(\frac{V_o}{K} + V_{in}\right) \cdot \left(1 - \cos\left(2 \cdot \pi \cdot f_1 \cdot t\right)\right)$$

$$v_{Cr21}(t) = V_o + \left[ \frac{\frac{K\sqrt{4+2\cdot K}}{(2+K)\cdot(1+K)}}{2} \cdot \sqrt{1 - \left(\frac{V_o\cdot(K+1)}{K(V_o - V_{in})} - 1\right)^2} \right] \cdot \sin\left(2\cdot\pi\cdot f_1\cdot t\right) + \frac{K}{K+1} \cdot \left(\frac{V_o}{K} + V_i\right) \cdot \left(\cos\left(2\cdot\pi\cdot f_1\cdot t\right) - 1\right) \right]$$

(21)

$$v_{Cr22}(t) = V_o + \begin{bmatrix} \frac{K\sqrt{4+2\cdot K}}{(2+K)\cdot(1+K)} \\ \frac{(V_o - V_i)}{2} \cdot \sqrt{1 - \left(\frac{V_o \cdot (K+1)}{K(V_o - V_{in})} - 1\right)^2} \\ + \frac{K}{K+1} \cdot \left(\frac{V_o}{K} + V_i\right) \cdot \left(\cos\left(2\cdot\pi \cdot f_1 \cdot t\right) - 1\right) \end{bmatrix}$$

(22)

The time interval that defines this stage is:

$$\Delta t_{3} = \arctan\left(\frac{\frac{K\sqrt{4}+2\cdot K}{(2+K)\cdot(1+K)}}{\frac{\left(\frac{(V_{o}-V_{i})}{2}\cdot\sqrt{1-\left(\frac{V_{o}\cdot(K+1)}{K(V_{o}-V_{i})}-1\right)^{2}}\right)}{\frac{K}{K+1}\cdot\left(\frac{V_{o}}{K}+V_{i}\right)}\right)$$

(23)

## • Fourth stage $[t_3-t_4]$ (Fig. 4 (d)) – Third resonant stage.

Diode  $D_{SI}$  is reverse biased and switch  $S_I$  conducts the current through capacitor  $C_{rI2}$ . The relevant resonant circuit is the same one presented in the third stage. This stage finishes when  $i_{Lr}$  is null so that switch  $S_{rI}$  can be turned off, and the time interval that defines it is:

$$\Delta t_4 = \arctan\left(\frac{\left(I_m + \frac{(V_o - V_i)}{2 \cdot Z_o}\right)}{\sqrt{1 - \left(\frac{V_o \cdot (K+1)}{K (V_o - V_i)} - 1\right)^2}}\right)}{\frac{K}{K+1} \cdot \left(\frac{V_o}{K} + V_i\right) \cdot \frac{1}{Z_1}}\right)$$

(24)

## • Fifth stage [*t*<sub>4</sub>-*t*<sub>5</sub>] (Fig. 4 (e)) – Second linear stage.

Since the current through the resonant inductor is null when this stage begins, switch  $S_{rl}$  is turned off in ZCS mode at instant  $t_4$ . As diodes  $D_{2l}$ ,  $D_{22}$  and  $D_{12}$  are reverse biased, the boost current  $I_b$  flows through capacitors  $C_{rl2}$ ,  $C_{r2l}$  and  $C_{r22}$ . The behavior of the voltages across the resonant capacitors is:

-  $v_{Cr2I}(t)$  decreases linearly from  $V_o$  to  $v_{Cr2I}(t_5)$ ;

- $v_{Cr12}(t)$  increases linearly from  $v_{Cr12}(t_4)$  to  $V_o$ ;

- $v_{Cr22}(t)$  decreases linearly from  $v_{Cr22}(t_4)$  to  $v_{Cr22}(t_5)$ .

This stage finishes when diode  $D_{12}$  starts conducting and the currents through capacitors  $C_{r12}$ ,  $C_{r21}$  and  $C_{r22}$  become null instantly. It can be mathematically described according to expressions (25) to (27).

$$v_{Cr12}(t) = v_{Cr12}(t_4) + \left(\frac{1+K}{2+K}\right) \cdot \frac{I_m}{C_{r12}} \cdot t$$

(25)

$$v_{Cr21}(t) = v_{Cr21}(t_4) - \left(\frac{1}{2+K}\right) \cdot \frac{I_m}{C_{r21}} \cdot t$$

(26)

$$v_{Cr22}(t) = v_{Cr22}(t_4) - \left(\frac{1}{2+K}\right) \cdot \frac{I_m}{C_{r22}} \cdot t$$

(27)

The time interval that defines this stage is:

$$\Delta t_5 = \left(V_o - v_{Cr12}(t_4)\right) \cdot \left(\frac{2+K}{1+K}\right) \cdot \frac{C_{r12}}{I_m}$$

(28)

# • Sixth stage $[t_5 - t_6]$ (Fig. 4 (f)) – First constant stage.

In this stage, the whole variables set remains constant, as the control circuit defines time interval  $\Delta t_6$ . This stage finishes when switch  $S_1$  is turned off.

• Seventh stage  $[t_6-t_7]$  (Fig. 4 (g)) – Third linear stage.

When switch  $S_I$  is turned off in ZVS mode, capacitor  $C_{r11}$  is charged linearly by current  $I_b$ , as capacitors  $C_{r21}$  and  $C_{r22}$  discharge completely. This stage finishes when  $v_{Cr11}(t_7)=2\cdot V_o$  and  $v_{Cr21}(t_7)=v_{Cr22}(t_7)=0$ , what can be mathematically described according to expressions (29) to (31).

$$v_{Cr11}(t) = \left(\frac{K+1}{2 \cdot K+1}\right) \cdot \frac{I_m}{C_{r11}} \cdot t$$

(29)

$$v_{Cr21}(t) = \left[ v_{Cr21}(t_4) - \frac{K}{1+K} \cdot \left( V_o - v_{Cr12}(t_4) \right) \right]$$

$$- \left( \frac{K}{2 \cdot K + 1} \right) \cdot \frac{I_m}{C_{r21}} \cdot t$$

(30)

$$v_{Cr22}(t) = \left[ v_{Cr22}(t_4) - \frac{1}{1+K} \cdot \left( V_o - v_{Cr12}(t_4) \right) \right]_{(31)} - \left( \frac{K}{2 \cdot K + 1} \right) \cdot \frac{I_L}{C_{r22}} \cdot t$$

This stage is defined by:

$$\Delta t_7 = \left(\frac{2 \cdot K + 1}{K + 1}\right) \cdot \frac{C_{r11}}{I_m} \cdot V_o \tag{32}$$

### • Eighth stage $[t_7-t_8]$ (Fig. 4 (h)) – Second constant stage.

The controller defines time interval  $\Delta t_8$ , and this stage finishes when switch  $S_{rl}$  is turned on, and the next switching cycle begins.

If the current through the boost inductor is low, the voltage across  $C_{r11}$  does not reach  $V_o$  during the seventh stage, and the voltages across  $C_{r21}$  and  $C_{r22}$  do not become null. Hence diodes  $D_{21}$  and  $D_{s2}$  remain blocked during the eighth stage, which is not considered in the analysis of the converter operation. When the control circuit enables switch  $S_{r1}$  to be turned on, the first stage begins. During the second stage, capacitors  $C_{r11}$  and  $C_{r12}$  are fully discharged, while capacitors  $C_{r21}$  and  $C_{r22}$  are charged until the voltage across  $C_{r21}$  equals  $V_o$ . Since the remaining resonant stages occur independently on the current through the boost inductor, resonance is not influenced and, consequently, turning on and turning off of the switches are not affected when such current is low.

## B. Influence of The Soft Switching Cell in The Duty Cycle

Considering the positive semicycle of the current through the boost inductor, an expression for the maximum duty cycle can be obtained according to the analysis presented below.

During the first and second stages, switch  $S_I$  is turned off due to the resonance, and capacitor  $C_{rII}$  remains charged. In the third stage,  $v_{CrII}$  becomes null, and switch  $S_I$  is enabled to be turned on when  $C_{rII}$  is fully discharged. Since the current through  $C_{rI2}$  is negative, it flows through diode  $D_{sI}$ and resonant inductor  $L_r$ .

In the fourth stage, the current through  $C_{r12}$  becomes positive, and  $S_1$  is turned on. The boost current is constant and flows through the path defined by  $S_1$ - $C_{r12}$ - $C_{b2}$ - $C_{b1}$ - $C_{r22}$ - $C_{r21}$ .

Since the voltage across  $C_{r12}$  is not equal to the output voltage in the fifth stage,  $D_{12}$  is reverse biased. Part of the boost inductor current charges  $C_{r11}$  and discharges  $C_{r21}$  and  $C_{r22}$ , and switch  $S_1$  is on. In the sixth stage,  $S_1$  remains turned on, and the current flows through diode  $D_{12}$ .

During the seventh stage, switch  $S_1$  is turned off under ZVS condition, and it remains off as well in the next stage.

In front of the aforementioned assumptions, the following expression becomes valid.

$$D_{\max} = \frac{\Delta t_5 + \Delta t_6}{T_s} = \frac{\Delta t_5 + \Delta t_6}{\sum_{i=1}^8 \Delta t_i}$$

(33)

#### C. Some Aspects Regarding The Input Current

The resonant circuit employed in the converter imposes an undesirable effect to the input current, which is in discontinuous mode. In order to solve this problem, a small LC filter is applied to the input of the converter, where a cutoff frequency  $f_c$  equal to about 5% to 10% of the switching frequency is set. Therefore, expression (34) is valid, where  $C_f$  must not be big enough to cause a displacement between the input current and the input voltage.

$$L_f = \frac{1}{\left(2 \cdot \pi \cdot f_c\right)^2 \cdot C_f} \tag{34}$$

## III. CONTROL SYSTEM

The strategy employed in the proposed topology is the average current mode control, which can be implemented with a PFC integrated circuit [11]. The closed-loop diagram is presented in Fig. 6.

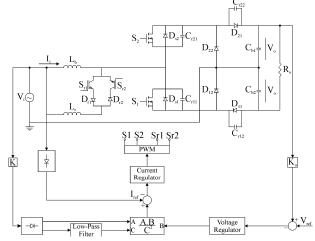

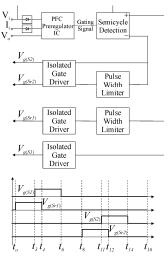

The half-bridge doubler boost converter operates with isolated gate drivers, adding complexity to the control system, since different circuits are used for the main and auxiliary switches. Auxiliary switches use optocouplers and dedicated gate driver IC [7]. Main switches are driven with dual thyristor schemes [7] [12]. A diagram representing the gating signals applied to the switches is shown in Fig. 7.

Fig. 6. Half-bridge doubler boost converter operating with average current mode control.

Fig. 7. Gating signals applied to main and auxiliary switches.

#### IV. DESIGN PROCEDURE

From the study developed in [7], the following expressions for the calculation of the circuit parameters could be obtained.

The boost inductance is given by:

$$L_b = 2 \cdot \frac{25000 \cdot P_o}{f_s \cdot \eta} \tag{35}$$

where  $P_o$  is the output power,  $f_s$  is the switching frequency and  $\eta$  is the efficiency of the converter.

The output capacitors are calculated according to (36).

$$C_{b1} = C_{b2} = 2 \cdot \frac{P_o}{2 \cdot \pi \cdot (2 \cdot N \cdot f) \cdot V_o \cdot \Delta V_o}$$

(36)

where N is the number of phases, f is the line frequency and  $\Delta V_o$  is the maximum output voltage ripple.

The first step to calculate the resonant elements lies is the choice of the resonant frequency, which must be at least ten times the switching frequency to assure the accurate operation of the circuit. If the resonant inductor is chosen arbitrarily (typically a few microhenries), expression (6) can be used to determine parameter  $C_r$ , defined in (8). Additionally, if parameter *K* is calculated according to (16), the resonant capacitors are then obtained from (37) and (38).

$$C_{r11} = C_{r21} = \frac{K+1}{K} \cdot C_r \tag{37}$$

$$C_{r12} = C_{r22} = (1+K) \cdot C_r \tag{38}$$

## V. ANALYTICAL RESULTS

In order to validate the study developed above, evaluation tests of the proposed converter were performed using the parameters set presented in Table I.

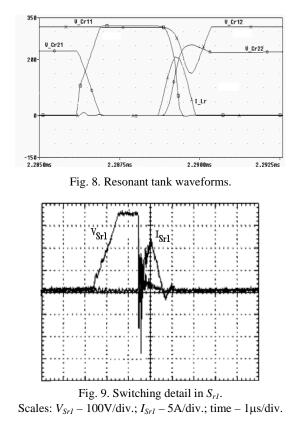

Fig. 8 shows the voltages across the resonant capacitors and the current through the resonant inductor. It can be seen that the maximum voltage peaks across the resonant capacitors do not exceed half of the output voltage in any circumstances. The aforementioned results were obtained using software OrCAD release 9.2, and demonstrate the validity of the theoretical analysis.

Furthermore, an experimental prototype of the converter was implemented. Fig. 9 shows the switching detail in auxiliary switch  $S_{rl}$ , where it can be seen that it is turned on with null current and turned off with null current and null voltage.

Fig. 10 corresponds to the switching detail in main switch S1, where the soft switching is achieved with reduced dv/dt rates, without current and/or voltage stresses.

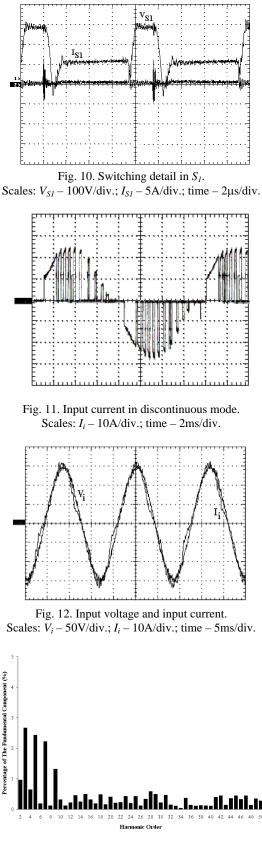

Fig. 11 shows the input current in discontinuous mode, without the low-pass filter.

Fig. 12 evidences power factor correction, where it can be seen that the total harmonic distortion is low and a high power factor is achieved i.e. current THD is 5.5% and power factor is 0.990. Fig. 13 represents the harmonic content of the input current.

Table I Parameters set employed in the tests

| i arameters set employed in the tests    |                                      |

|------------------------------------------|--------------------------------------|

| Parameter                                | Description                          |

| Line frequency                           | <i>f</i> =60Hz                       |

| Switching frequency                      | $f_s=50 \text{kHz}$                  |

| Rms input voltage                        | $V_i=110V$                           |

| Output voltage                           | $V_o=300V$                           |

| Maximum output voltage ripple            | $\Delta V_o = 5\% \cdot V_o$         |

| Output power                             | $P_{o} = 800 \text{W}$               |

| Efficiency                               | η=97%                                |

| Boost inductor                           | <i>L</i> <sub>b</sub> =380µH         |

| Resonant inductor                        | <i>L<sub>r</sub></i> =4.9µH          |

| Resonant capacitors                      | $C_{r11} = C_{r21} = 3.3$ nF         |

| Resonant capacitors                      | $C_{r12} = C_{r22} = 18.8 \text{nF}$ |

| Output capacitors                        | $C_{bl} = C_{b2} = 1000 \mu F$       |

| Input filter inductor                    | <i>L<sub>f</sub></i> =80µH           |

| Input filter capacitor                   | $C_f=10\mu\mathrm{F}$                |

| Diodes                                   | MUR1560                              |

| Main switches $S_1$ and $S_2$            | MOSFET – IRFP460                     |

| Auxiliary switches $S_{rl}$ and $S_{r2}$ | IGBT – IRG4BC30U                     |

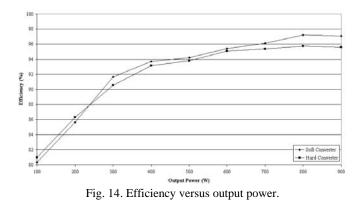

Finally, Fig. 14 presents the converter efficiency as a function of the output power. Hard-switching and softswitching topologies shown in Fig. 2 and Fig. 3 are compared, as both them operate at 100kHz with the parameters set detailed in Table I. It can be seen that the use of the soft commutation cell becomes interesting at a few hundreds of watts, and efficiency is about 97% at nominal load.

Fig. 13. Harmonic spectrum of the input current.

(%)

#### VI. ABOUT THE PROPOSED TOPOLOGY

The half-bridge structure shown in Fig. 1 is a prominent alternative if compared with the conventional boost converter, since conduction losses are drastically reduced. However, the voltage stresses across the switches are twice the output voltage. An improvement results if the topology depicted in Fig. 2 is adopted, because the voltages across the switches are equal to the output voltage instead.

If an active auxiliary circuit is added, complexity is supposed to increase and reliability is affected, because four capacitors, one inductor, two auxiliary switches, and two diodes are employed in this case. Furthermore, conduction losses increase as well, but they are mainly due to the components existent in the hard-switched topology presented in Fig. 2.

Soft switching is a desired feature in power converters because it reduces the overlap between voltage and current, enabling high frequency operation, minimizing switching losses and giving a longer life for the switch. The choice between passive and active soft switching methods depends on a series of conditions [8]. This is not the scope of the paper, which aims to analyze the performance of the soft switching cell associated with the half-bridge doubler boost converter. Possibly, improved soft switching schemes can be proposed for this topology, as the one described here is not a definitive solution.

Possible advantages of the proposed configuration are:

- The voltages across the semiconductor devices are reduced and approximately equal to the output voltage;

- Doubled output voltages can be achieved;

- Reduced high frequency ripple of the output voltage is obtained due to diodes  $D_{12}$  and  $D_{22}$ ;

- Switching losses are negligible;

- In Fig. 14, one can see that the efficiency increases about 2% at nominal power.

## VII. CONCLUSION

This paper has reported the study of a soft-switched halfbridge doubler boost converter that can be used in PFC applications. The main purpose of this work deals with the development of a structure without commutation losses so that higher output voltages and reduced voltage stresses across the semiconductor devices can be achieved, as high power factor and low harmonic content are obtained. The results show that the main advantages of the proposed topology are the reduced voltages across the semiconductor devices, achievement of doubled output voltages, reduced high frequency ripple and also lossless commutation of the switches. As drawbacks, one can mention the complexity added to control system and drivers due to the cell, and also increased number of components.

#### REFERENCES

- R. Srinivasan, R. Oruganti, "A Unity Power Factor Converter Using Half Bridge Boost Topology", IEEE Transactions on Power Electronics, vol. 13, No. 3, pp. 487-500, May, 1998.

- [2] D. Maksimovic, R. Erickson, "Universal-Input, High-Power-Factor, Boost Doubler Rectifiers". IEEE Applied Power Electronics Conference and Exposition – APEC '95, 1995, Dallas, TX, USA, pp. 459-465.

- [3] D. Shmilovitz, Z. Shoubou; Ž. Zabar, D. Czarkowski, "A Simplified Controller for A Half Bridge Boost Controller", IEEE Applied Power Electronics Conference and Exposition – APEC 2000, 2000, New Orleans, LA, USA, pp. 452-455.

- [4] C.M.T. Cruz, I. Barbi, "Unit Power Factor Active Clamping Single Phase Three Level Rectifier", IEEE Applied Power Electronics Conference and Exposition, 2001, pp. 331-336.

- [5] J.C. Salmon, "Reliable 3-Phase Boost Rectifiers Employing A Stacked Dual Boost Converter Subtopology", IEEE Transactions on Industrial Applications, Vol. 32, No 3, May/June 1996, pp. 542-551.

- [6] K. Thiyagarajah, V.T. Ranganathan, B.S.R. Iyengar, "A High Switching Frequency IGBT PWM Rectifier/Inverter System for AC Motor Drives Operating from Single Phase Supply", IEEE Transactions on Power Electronics, vol. 6, issue 4, Oct. 1991, pp. 576-584.

- [7] R.M. Finzi Neto, "Um Carregador de Baterias Inteligente, Alta Potência, Usando Tecnologia de Fontes Chaveadas com Comutação Não Dissipativa e Correção do Fator de Potência", Uberlândia-MG, Brazil, 2003. PhD Thesis – UFU – in Portuguese.

- [8] I. Matsuura, K.M. Smith Jr., K.M. Smedley, "A Comparison of Active and Passive Switching Methods for PWM Converters", 29th Annual IEEE Power Electronics Specialists Conference – PESC '98, 1998, vol. 1, May 1998, pp. 94-100.

- [9] L.C. Freitas, J.B. Vieira Jr., V.J. Farias, H.L. Hey, P.S. Caparelli, D.F. Cruz, "An Optimum ZVS PWM DC to DC Converter Family: Analysis, Simulation and Experimental Results", IEEE Power Electronics Specialists Conference – PESC '92, 1992, Toledo, Spain, pp. 229-235.

- [10] L.C. Freitas, D.F. Cruz, V.J. Farias, "A Novel ZCS-ZVS PWM DC-DC Buck Converter for High Switching Frequency: Analysis, Simulation and Experimental Results", IEEE Applied Power Electronics Conference and Exposition – APEC '93, 1993, San Diego, CA, USA, pp. 693-699.

- [11] P.C. Todd "UC3854 Controlled Power Factor Correction Circuit Design", UNITRODE Application Note U-134.

- [12] D.S. Oliveira Jr., C.A. Bissochi Jr., J.B. Vieira Jr., V.J. Farias, L.C. Freitas, "A Lossless Commutation PWM Two Level Forward Converter Operating Like A Full-Bridge", IEEE Applied Power Electronics Conference and Exposition – APEC 2000, 2000, pp. 334-339.

## BIOGRAPHIES

**Roberto Mendes Finzi Neto** was born in Goiânia, Goiás, Brazil, on January 31<sup>st</sup>, 1974. He received the BSc, MSc and PhD degrees in Electrical Engineering from the Federal University of Uberlândia, Brazil, in 1997, 1999 and 2003, respectively. His research interest areas include highfrequency power conversion, modeling and control of converters, power factor correction circuits, and new converters topologies.

**Enes Gonçalves Marra** was born in Brazil on 1966. He received the B.S. and M.S. degrees in Electrical Engineering from the Federal University of Uberlândia, Uberlândia, Brazil, and the Doctoral degree in electrical engineering from the State University of Campinas, Campinas, Brazil, in 1989, 1993, and 1999, respectively. Since 1993, he has been a Lecturer in the School of Electrical Engineering, Federal University of Goiás, Goiânia, Brazil. His research interests include electrical drives, power electronics applications, and renewable energy sources.

**Fernando Lessa Tofoli** was born on March 11<sup>th</sup>, 1976, in São Paulo, São Paulo, Brazil. He received the BSc and MSc degrees in Electrical Engineering from the Federal University of Uberlândia, Brazil, in 1999 and 2002, respectively. Nowadays he is PhD student at the Power Electronics Research Group of the same university. His research interests include power quality related issues, high power factor rectifiers and soft switching techniques applied to static power converters.

**Luiz Carlos de Freitas** was born in Prata, Minas Gerais, Brazil, on April 1<sup>st</sup>, 1952. He received the BSc degree in Electrical Engineering from the Federal University of Uberlândia, Brazil, in 1975, and the MSc and PhD degrees from the Federal University of Santa Catarina, Brazil, in 1985 and 1992, respectively. Nowadays he is with Department of Electrical Engineering of the Federal University of Uberlândia, Brazil. His research interests include high-frequency power conversion, modeling and control of converters, power factor correction circuits and novel converters topologies.