## UMA TÉCNICA BASEADA NO MÉTODO DE CIRCUITO DISCRETO ASSOCIADO PARA SIMULAÇÃO EM TEMPO REAL DE CONVERSORES DE POTÊNCIA

Oscar Solano Rueda<sup>1</sup>, Cesar J. Bandim<sup>1</sup>, Luís Guilherme B. Rolim<sup>2</sup>

<sup>1</sup>Centro de Pesquisas de Energia Elétrica (CEPEL), Rio de Janeiro – RJ, Brasil

<sup>2</sup>Universidade Federal do Rio de Janeiro (UFRJ), Rio de Janeiro – RJ, Brasil

e-mail: oscar@cepel.br, bandim@cepel.br, rolim@poli.ufrj.br

Resumo – Este artigo apresenta um simulador em tempo real para aplicações de eletrônica de potência no qual um módulo FPGA (Field Programmable Gate Arrav) com representação numérica por ponto fixo soluciona as equações do sistema elétrico modelado, utilizando um passo discreto de 1 µs. A principal contribuição deste trabalho é a proposição de uma técnica para modelagem chaveada de conversores controláveis, baseada no método G-ADC (Generalized Associated Discrete Circuit), que emprega um algoritmo de inicialização para a fonte de corrente em paralelo de cada modelo de chave, de forma a obter uma representação acurada e com uso reduzido dos recursos de cálculo da FPGA. A validação da técnica proposta é realizada mediante a comparação de seus resultados com os obtidos por um software off-line de benchmark, para três sistemas elétricos independentes com conversores fonte de tensão (VSC). Adicionalmente, uma bancada experimental HIL (Hardware in the Loop), na qual um processador digital de sinais (DSP) é conectado através de sinais analógicos e digitais ao simulador em tempo real, é desenvolvida. Esta bancada mostra a aplicabilidade do simulador proposto na avaliação de controladores embarcados para conversores de potência.

Palavras-Chave – Circuito discreto associado, FPGA, Geração distribuída, Hardware-in-the-loop, Simulação em tempo real, VSC.

## A TECHNIQUE BASED ON THE ASSOCIATE DISCRETE CIRCUIT METHOD FOR REAL-TIME SIMULATION OF POWER CONVERTERS

Abstract – This paper presents a real-time simulator for power electronics application in which a FPGA (Field Programmable Gate Array) with fixed-point numerical representation solves the equations of the modeled electrical system using a discrete time-step of 1 µs. The main contribution of this work is the proposition of a switched modelling technique for controlled converters, based in the G-ADC (Generalized Associate Discrete Circuit) method, which uses an initialization algorithm for the current source in parallel of each switch model, in order to obtain an accurate representation with reduced

Artigo submetido em 31/07/2019. Primeira revisão em 17/09/2019. Aceito para publicação em 16/03/2020 por recomendação do Editor Marcello Mezaroba. http://dx.doi.org/10.18618/REP.2020.1.0057

use of the calculation resources of the FPGA. The validation of the proposed approach is performed by comparing its results with those obtained by an off-line benchmark software for three independent electrical systems with voltage source converters (VSC). In addition, an experimental Hardware-in-the-loop (HIL) bench, in which a Digital Signal Processor (DSP) is connected through analog and digital signals to the simulator in real-time, is developed. This workbench shows the applicability of the proposed simulator for the evaluation of embedded controllers for power converters.

*Keywords* – Associate discrete circuit, Distributed generation, FPGA, HIL, Real-time simulation, VSC.

### I - INTRODUÇÃO

A simulação digital em tempo real pode ser definida como a reprodução instantânea dos sinais de saída (tensões e correntes) que são representativos do comportamento do sistema de potência real que está sendo modelado [1]. Para isto, o simulador precisa solucionar, no domínio do tempo, as equações que definem o sistema com um tempo de execução  $(t_e)$  igual ao passo discreto de solução empregado na modelagem ( $\Delta t$ ). De modo mais exato,  $t_e$  pode ser também menor do que  $\Delta t$  desde que um tempo ocioso seja adicionado no algoritmo de solução, de forma a manter sincronismo entre  $\Delta t$  e o início do próximo passo de solução, como descreve a Figura 1.

Fig. 1. Representação da simulação em tempo real.

A principal motivação para o surgimento da simulação digital em tempo real foi o desejo de testar hardware de controle interagindo com um sistema elétrico digital representativo do sistema real [2]. Este tipo de ensaio é conhecido como *Hardware-in-the-Loop* (HIL). Os ensaios HIL têm ganhado notoriedade uma vez que tem sido mostrado que podem apresentar vantagens sobre as simulações totalmente computacionais, bem como sobre os ensaios experimentais em laboratório [3]. No contexto das redes elétricas modernas, que se caracterizam por maior penetração de geração distribuída (GD) com conversores eletrônicos para sua conexão com a rede, os ensaios HIL são

uma excelente ferramenta para desenvolvimento, teste e customização dos controladores embarcados utilizados nesses conversores [4].

A simulação digital em tempo real de modelos chaveados de conversores eletrônicos apresenta como principal desafio a necessidade de um passo de solução suficientemente pequeno para representar, com um número satisfatório de pontos temporais, cada período de chaveamento, de forma a minimizar o erro causado pelos eventos de chaveamento entre passos de simulação (*inter-simulation time-step switching* (ITS), em inglês) [5]. Segundo Matar et al. em [6], uma relação entre o inverso do passo de simulação ( $1/\Delta t$ ) e a frequência de chaveamento ( $f_{ch}$ ) superior a 100 garante que os erros relacionados a ITS sejam desprezíveis no conversor tipo fonte de tensão (VSC) trifásico de dois níveis. Na prática, isto implica que a simulação deste conversor, utilizando um chaveamento PWM de 10 kHz, requer um passo de solução igual ou inferior a 1  $\mu$ s.

Atingir tais tempos de execução tem se mostrado desafiador para dispositivos de processamento baseados em operações sequenciais, como são as CPUs. Assim, o das paralelismo e determinismo **FPGAs** (Field Programmable Gate Array) têm sido aproveitados, tanto por equipamentos comerciais quanto por trabalhos acadêmicos, para realizar a simulação em tempo real de conversores eletrônicos [1], [6]–[10]. Na maioria dos casos, a solução do sistema é obtida utilizando uma técnica de análise nodal baseada no algoritmo de Dommel [11] e as chaves são modeladas pelo método de circuito discreto associado (ADC) [12].

Neste trabalho é proposto um simulador digital em tempo real (SDTR) de transitórios eletromagnéticos baseado em um módulo FPGA. Esse desenvolvimento procura demonstrar a aplicabilidade de plataformas genéricas, com representação numérica por ponto fixo (FXP) e de menor custo do que SDTR comerciais, neste campo de aplicação. A contribuição do presente trabalho, em relação a desenvolvimentos similares disponíveis na literatura [13]–[15], é a proposição de uma técnica para a modelagem das chaves, a qual se baseia no método ADC Generalizado (G-ADC), descrito na Seção II. As análises das Seções V e VI mostram que a técnica proposta permite obter resultados com nível de exatidão similar ao método G-ADC, porém com menor uso dos recursos de cálculo do módulo FPGA.

A estrutura do artigo é a seguinte: na Seção II é apresentado um sucinto resumo teórico das técnicas de simulação de transientes eletromecânicos para sistemas com conversores eletrônicos de potência. Na Seção III são descritas as características de hardware do simulador proposto, bem como a metodologia utilizada para sua programação. A Seção IV descreve os sistemas elétricos modelados na validação do simulador proposto, bem como o sistema HIL experimental desenvolvido, junto com os resultados dos ensaios experimentais realizados. Na Seção V é feita uma avaliação comparativa da técnica proposta. As conclusões são apresentadas na Seção VI.

# II - SIMULAÇÃO EM TEMPO DISCRETO DE SISTEMAS COM CONVERSORES ELETRÔNICOS

#### A. Análise Nodal Matricial

Uma das técnicas amplamente utilizadas para realizar a simulação de transientes eletromagnéticos é o método de análise nodal matricial, baseado no artigo clássico de Dommel [11]. Neste método, os indutores e capacitores da rede elétrica são representados por uma condutância em paralelo com uma fonte de corrente, que representa o armazenamento de energia destes componentes. A magnitude desta fonte depende dos valores de corrente ou/e de tensão em passos anteriores de simulação, respectivamente, bem como do método de integração numérica utilizado. A virtude desta técnica é que permite transformar as equações diferenciais do sistema elétrico em equações algébricas, de forma a obter uma formulação de solução como a apresentada em (1):

$$Hx^{n+1} = b^{n+1}. (1)$$

Onde H é a matriz do sistema, formada pela representação em tempo discreto dos elementos do sistema;  $\boldsymbol{x}^{n+1}$  é o vetor de variáveis desconhecidas (tensões ou correntes) no instante discreto de simulação n+1; e  $\boldsymbol{b}^{n+1}$  é um vetor formado pelas fontes independentes, bem como pelas fontes de corrente da representação dos componentes armazenadores de energia, cujas magnitudes no instante n+1 são conhecidas. Esta técnica é implementada no simulador proposto neste trabalho.

#### B. Modelagem de Conversores Eletrônicos

De modo geral, a representação de um conversor eletrônico como um componente de um sistema elétrico pode ser realizada mediante um modelo chaveado ou um modelo de valor médio. Em estudos nos quais exista interesse em avaliar os componentes dinâmicos de altas e baixas frequências é necessário utilizar uma técnica de modelagem chaveada [16]. Nestas, os valores instantâneos das variáveis do conversor são calculados considerando o estado de chaveamento das chaves existentes.

O principal método utilizado por simuladores off-line para representação chaveada de conversores eletrônicos é o de resistência variável ( $resistive\ switching$ ), técnica na qual cada chave é representada por um par de valores de resistências: um valor "pequeno" no estado fechado ( $R_{on}$ ) e um valor "grande" no estado aberto ( $R_{off}$ ). Isto faz com que a mudança de estado em qualquer chave modifique a matriz representativa do sistema (H). Assim, essa matriz é atualizada e invertida durante a simulação, quando algum chaveamento acontecer [17]. Esta abordagem, no entanto, é restritiva para SDTR, pois a carga computacional nos instantes de reformulação de H é significativamente maior do que nos outros instantes de simulação [12], [14].

Em contrapartida, o método de representação chaveada mais comumente utilizado em SDTR é o de circuito discreto associado (ADC), descrito a seguir junto com os outros métodos objeto de estudo neste trabalho:

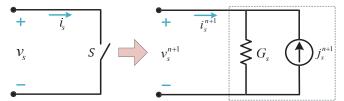

1) Método ADC: Nesta abordagem, proposta em [12], cada chave é substituída por uma condutância em paralelo com uma fonte de corrente, conforme mostrado pela Figura 2.

Fig. 2. Modelagem de uma chave controlável pelo método ADC, proposto em [12].

Uma vez que a condutância  $G_s$  é constante, a matriz H se mantém invariante para qualquer estado de chaveamento. O valor instantâneo da fonte de corrente  $j_s^{n+1}$ , por outro lado, representa o estado de comutação da chave e depende também do método de integração numérica. Neste trabalho é utilizado o método Euler Backward que se caracteriza por ser de fâcil implementação e mais estável numericamente do que método Trapezoidal [6], [12]. Com este método, o valor de  $j_s^{n+1}$  é dado por:

$$j_s^{n+1} = \begin{cases} -i_s^n & \text{se chave fechada } (s^{n+1} = 1) \\ G_s \cdot v_s^n & \text{se chave aberta } (s^{n+1} = 0) \end{cases} . \tag{2}$$

Uma vez que a matriz H não precisa ser recalculada, a técnica ADC simplifica e acelera a solução do sistema, em contraste com a técnica de resistência variável. Em contrapartida, introduz perdas de potência virtuais, bem como transientes numéricos irreais nos instantes de chaveamento, que podem comprometer a validade dos resultados [6], [14], [18]. Com o intuito de atenuar tais fenômenos indesejados, alguns trabalhos têm proposto metodologias para a escolha dos parâmetros utilizados na modelagem ADC ( $G_s$  e  $\Delta t$ ) [18], [19]. No entanto, mudanças nas condições operacionais ou nos parâmetros do restante da rede modelada podem desajustar a referida atenuação.

2) Método G-ADC: Esta técnica, proposta por Wang et al. em [14], pode ser interpretada como uma visão generalizada da técnica ADC tradicional, orientada a melhorar sua característica dinâmica. Nesta modelagem também é utilizada a representação da Figura 2; no entanto, o valor da fonte de corrente em paralelo é definido utilizando as expressões de (3):

$$j_s^{n+1} = \begin{cases} \alpha_{on} \cdot v_s^n + \beta_{on} \cdot i_s^n & \text{se chave fechada} \\ \alpha_{off} \cdot v_s^n + \beta_{off} \cdot i_s^n & \text{se chave aberta} \end{cases}$$

(3)

Assim, esta representação também mantém a matriz  $\boldsymbol{H}$  constante para qualquer estado de chaveamento. Observa-se, entretanto, que utiliza cinco parâmetros de ajuste para o modelo da chave  $(G_s, \alpha_{on}, \alpha_{off}, \beta_{on}, \beta_{off})$ , cujos valores ótimos dependem da topologia do conversor utilizado. A determinação de tais parâmetros para o caso do conversor fonte de tensão trifásico de dois níveis é realizada em [14] utilizando a abordagem de "melhor amortecimento", que dá como resultado as seguintes definições:

$$\alpha_{on} = (-1 - \sqrt{2}) \cdot G_s; \quad \beta_{on} = -1; \alpha_{off} = G_s; \quad \beta_{off} = (1 - \sqrt{2}).$$

(4)

Adicionalmente, no algoritmo de simulação utilizado por Wang et al. [14] é proposta a lógica mostrada na Figura 3, cujo objetivo é inicializar a fonte de corrente após uma ação

de chaveamento, de forma a reduzir a amplitude dos transientes numéricos originados. Nela, o valor de  $j_s^{n+1}$  no primeiro passo de simulação após uma mudança para o estado "ON" toma o valor que essa fonte tinha no último instante com estado "ON". Uma alocação correspondente é feita no caso do estado "OFF".

```

\begin{array}{c} \text{if } (s^{n+1}=s^n) \\ j_s^{n+1} = \text{computar } (3) \text{ considerando } s^{n+1} \\ \text{if } (s^{n+1}=1) \qquad j_{s-ON}^{memoria} = j_s^{n+1}; \\ \text{else} \qquad j_{s-OFF}^{memoria} = j_s^{n+1}; \\ \text{end} \end{array} else \begin{array}{c} \text{if } (s^{n+1}=1) \qquad j_s^{n+1} = j_{s-ON}^{memoria}; \\ \text{else} \qquad j_s^{n+1} = j_{s-OFF}^{memoria}; \\ \text{end} \end{array} end end

```

Fig. 3. Lógica para determinação do valor numérico da corrente em paralelo no método G-ADC.

3) Técnica proposta: Ao generalizar o cálculo da corrente  $i_s^{n+1}$  o método G-ADC aumenta o número de operações matemáticas requeridas para representar cada chave em cada instante de simulação (ver (2) e (3)). Isto pode se tornar um limitante para a implementação de um modelo digital no SDTR, em função da relação entre o número de chaves do sistema e a capacidade de computação da FPGA utilizada. Neste contexto, este artigo objetiva analisar o desempenho da segunda inovação do método G-ADC (lógica de inicialização das correntes da Figura 3) de forma individual, atividade não realizada pelo trabalho de Wang et al. [14]. Para isto, é proposta a técnica ADC com memória (ADC-M) na qual a corrente  $j_s^{n+1}$  é calculada por um algoritmo de inicialização similar ao apresentado na Figura 3, porém com uso da equação (2) em vez da (3). Esta técnica constitui uma abordagem semelhante à "inicialização cruzada" proposta pela patente de Dufour [20], entretanto se diferencia pelo fato de não requerer informações de grandezas elétricas em outras chaves do conversor para determinar as correntes em paralelo nos instantes de chaveamento.

#### C. Algoritmo de Solução Adotado Neste Trabalho

- O SDTR proposto neste trabalho realiza o seguinte algoritmo de solução de forma iterativa, cada 1 µs:

- Amostra os pulsos de chaveamento de entrada;

- Atualiza os valores do vetor b<sup>n+1</sup>, a partir dos valores anteriores de tensão/corrente nos elementos do sistema e do estado de chaveamento;

- Soluciona (1);

- Atualiza valores anteriores de tensões/correntes.

#### III - DESENVOLVIMENTO EM FPGA DE UM SIMULADOR DIGITAL EM TEMPO REAL

#### A. Configurações do Hardware Utilizado

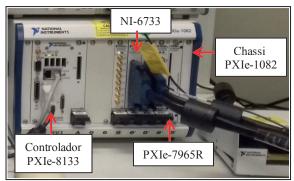

O módulo FPGA usado neste trabalho é o PXIe-7965R da *National Instruments*, cujas especificações são apresentadas na Tabela I. Este módulo é uma placa periférica de um sistema modular PXI que utiliza como chassi e controlador as referências PXIe-1082 e PXIe-8133, respectivamente. Conforme mostrado, o módulo FPGA carece de canais de

saída analógica. Estes sinais, porém, são necessários para fazer a interface entre o simulador em tempo real e os equipamentos reais de controle, em uma bancada HIL. Para contornar esta limitação, um módulo periférico de conversão digital/analógica (D/A), referência NI 6733, é acoplado ao sistema PXI. Constituindo o simulador mostrado na Fig. 4

TABELA I Principais Características do Módulo PXIe-7965R

| Timelpais Caracteristicas do Modulo 1 Arc-7703K            |                               |                            |                         |  |  |

|------------------------------------------------------------|-------------------------------|----------------------------|-------------------------|--|--|

| Parâmetro                                                  | Valor                         | Parâmetro                  | Valor                   |  |  |

| FPGA                                                       | Virtex-5 SX95T                | FPGA slices                | 14720                   |  |  |

| FPGA DSP slices                                            | 640                           | FPGA Memory<br>(Block RAM) | 8784 kbit               |  |  |

| Onboard Memory<br>(DRAM)                                   | 512 MB                        | LUTs/Flip-Flops            | 58880                   |  |  |

| Entrada analógica                                          | 16 canais<br>(2 Vpp, 14-bits) | Entrada digital            | 8 canais (0 a<br>3.5 V) |  |  |

| Saída analógica Não dispõe                                 |                               | Saída digital              | 8 canais (0 a<br>3.5 V) |  |  |

| Processamento de dados utilizando aritmética de ponto fixo |                               |                            |                         |  |  |

Fig. 4. Simulador PXI em tempo real utilizado neste trabalho.

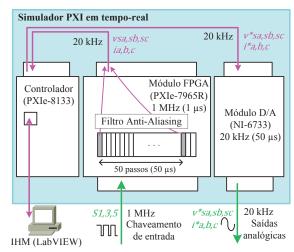

1) Operação do simulador PXI: A Figura 5 procura representar a função de cada um dos componentes do simulador PXI em tempo real proposto. O módulo FPGA realiza continuamente o algoritmo de solução descrito na Seção II.C, utilizando como entradas os pulsos digitais de chaveamento. O módulo D/A transforma as grandezas digitais calculadas pela FPGA em tensões analógicas representativas, utilizando uma subamostragem digital (não sincronizada) com passo de 50 µs. As magnitudes destas grandezas são ajustadas pela placa controladora para estar dentro da faixa de operação do conversor D/A ou do equipamento conectado a ele, o que for mais restritivo. Além de coordenar a transferência de dados entre o módulo FPGA e o módulo D/A, o controlador PXIe-8133 armazena e transmite as variáveis de interesse a um computador de interface e monitoramento.

Conforme mostra a Figura 5 um filtro digital passa baixas foi introduzido na programação do módulo FPGA para atenuar o fenômeno de *Aliasing* associado à subamostragem realizada pelo conversor D/A. Tal filtro, de tipo Butterworth de segunda ordem com frequência de corte de 5 kHz, é aplicado nas variáveis chaveadas a serem exportadas; o mesmo apresenta atenuação nula e atraso de 1° na frequência de 60 Hz. Outro componente acrescentado na programação do módulo FPGA é um registro FIFO, no qual são armazenadas as variáveis de interesse durante 0,75 s, utilizando uma resolução temporal de 1 µs. Isto permite a análise off-line detalhada das formas de onda chaveadas.

Fig. 5. Operação dos componentes do simulador PXI.

#### B. Implementação no Módulo FPGA.

A solução numérica da equação (1) é programada neste trabalho como uma multiplicação matricial no software LabVIEW FPGA, onde os coeficientes da matriz inversa de *H* são constantes e determinados antes da execução da simulação. O cálculo das correntes em paralelo (através de (2) ou (3), segundo o tipo de representação) e a lógica da Figura 3 são programados utilizando funções básicas matemáticas e estruturas do tipo *case*. Finalizada a programação, o código é compilado de forma a criar o arquivo *bitstream* com as informações das interconexões do módulo FPGA.

Destaca-se que a metodologia de implementação utilizada origina iguais tempos de execução ( $t_e$ ) para cada circuito modelado, independentemente do método de representação de chaves considerado em cada caso (ADC, ADC-M ou G-ADC).

## IV - VALIDAÇÃO DO SIMULADOR PROPOSTO

#### A. Primeiro Sistema Elétrico

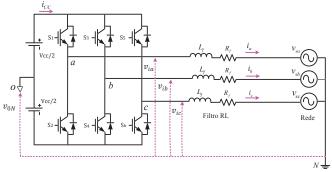

O sistema inicialmente utilizado é apresentado na Figura 6. Trata-se de um conversor trifásico VSC de dois níveis conectado a uma fonte CC no seu barramento de corrente contínua e à rede elétrica no lado CA. Este conversor utiliza um filtro RL para atenuar os componentes de alta frequência nas ondas de corrente ( $i_a$ ,  $i_b$  e  $i_c$ ). A rede elétrica equivalente é considerada como um ponto de conexão ideal, representado por um conjunto de três fontes senoidais balanceadas (sequência negativa e sequência zero nulas).

Fig. 6. Sistema elétrico utilizado no caso de estudo.

Os parâmetros deste sistema são:

TABELA II Parâmetros do Sistema Elétrico do Caso de Estudo

| Grandeza                     | Símbolo   | Valor                   |

|------------------------------|-----------|-------------------------|

| Tensão nominal elo CC        | $V_{ncc}$ | 800 V                   |

| Tensão fase-fase rede eficaz | $V_{sn}$  | 440 Vrms                |

| Frequência do sistema        | $f_{nom}$ | 60 Hz                   |

| Potência Nominal             | $S_n$     | 250 kVA                 |

| Resistência filtro           | $R_f$     | $4,65~\mathrm{m}\Omega$ |

| Indutância filtro            | $L_f$     | 308.12 μH               |

| Frequência de chaveamento    | $f_{ch}$  | 10 kHz                  |

Neste trabalho é considerado que as chaves superior e inferior de cada braço são ambas ideais e operam de forma complementar, ou seja, no instante em que uma destas é fechada a outra é aberta. Com esta consideração, os três sinais de controle das chaves superiores  $(S_1, S_3 \in S_5)$  são suficientes para comandar a operação do conversor, interpretando os sinais de chaveamento inferiores como o inverso lógico do sinal superior (operação lógica NOT). Um quarto sinal  $S_{chav}$  é utilizado também para indicar quando todas as seis chaves têm lógica negativa, ou seja, instantes em que o chaveamento do conversor é interrompido. O valor de  $G_s$  foi ajustado em 0,94 pu (nas bases de tensão e corrente de 400 V e 500 A, respectivamente).

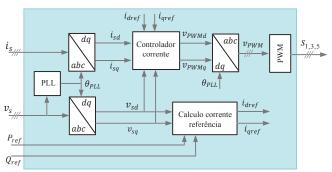

1) Estrutura de controle: Um diagrama esquemático do algoritmo de controle utilizado nos ensaios de validação é mostrado na Figura 7. Neste, o sinal trifásico de tensão no ponto de conexão comum  $(v_s)$  é utilizado como entrada para um bloco de rastreamento de fase (PLL- Phase-Locked Loop), baseado em [21], que determina o ângulo de sincronismo com a rede ( $\theta_{PLL}$ ). O referido ângulo é utilizado para transformar as grandezas do sistema das coordenadas abc para o referencial girante dq, utilizando a transformada de Park [22]. Após os componentes  $v_{sd}$  e  $v_{sq}$  serem calculados, o uso da expressão (5) determina as correntes de referência necessárias para atingir os valores desejados de potências ativa e reativa de referência ( $P_{ref}$  e  $Q_{ref}$ ). Um controlador em laço fechado tipo PI, baseado em [16], é utilizado para definir os sinais de modulação  $v_{PWM}$ . Estes são aplicados como entrada para o bloco PWM (Pulse Width Modulation), que estabelece os pulsos de disparo das chaves  $S_1$ ,  $S_3$  e  $S_5$ .

Fig. 7. Diagrama de blocos do controle utilizado.

$$\begin{bmatrix} i_{dref} \\ i_{qref} \end{bmatrix} = \frac{1}{v_{sd}^2 + v_{sq}^2} \cdot \begin{bmatrix} v_{sd} & v_{sq} \\ v_{sq} & -v_{sd} \end{bmatrix} \times \begin{bmatrix} P_{ref} \\ Q_{ref} \end{bmatrix}.$$

(5)

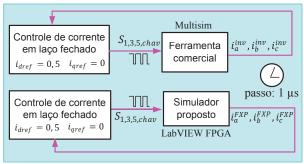

#### B. Validação Off-line

Para verificar a exatidão dos métodos de representação de chaves descritos na Seção II é utilizado o esquema conceitual da Figura 8. Nele, idênticos controladores em laço fechado baseados no esquema da Figura 7, nos quais as referências de corrente nos eixos dq são mantidas constantes e iguais, comandam, de forma independente, o sistema elétrico da Figura 6, que é modelado por duas ferramentas de simulação: i) O simulador com aritmética em ponto fixo proposto neste trabalho, desenvolvido no software LabVIEW FPGA e ii) o software comercial de benchmark Multisim. simplicidade, nesta validação a dinâmica de geração dos sinais analógicos pelo conversor D/A, bem como a filtragem anti-aliasing não são modelados.

Fig. 8. Esquema de validação off-line da exatidão do simulador.

Nesta validação as duas ferramentas rodam no PC de desenvolvimento, em modo off-line. Isto é possível uma vez que o software LabVIEW FPGA oferece um modo de simulação, que tem um comportamento idêntico ao conseguido quando os cálculos são efetuados em hardware pelo módulo FPGA [23]. A metodologia descrita pela Figura 8 é utilizada para os três tipos de representação de chaves descritas na Seção II, bem como para o método de resistência variável, que serve para identificar o erro introduzido pela falta de precisão da representação com ponto fixo, uma vez que o software de *benchmark* utiliza também a modelagem de resistência variável.

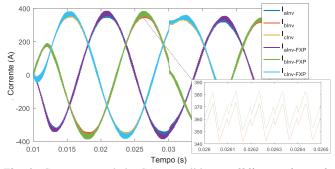

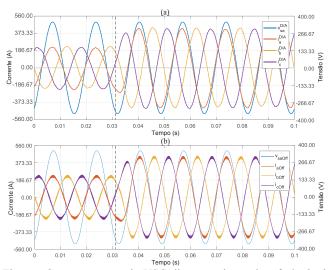

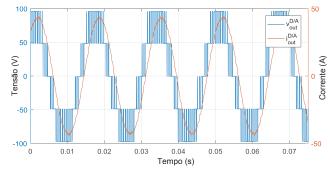

A Figura 9 mostra de forma gráfica a comparação entre as correntes do lado CA do inversor, para as duas ferramentas de simulação diante um evento de variação instantânea de frequência (de 60 Hz para 57,5Hz). Este resultado é relativo à técnica ADC-M, proposta. Visualiza-se um conjunto de ondas com comportamento bastante semelhante, o que indica a exatidão da ferramenta desenvolvida.

Fig. 9. Correntes no lado CA na validação off-line, variação de frequência da rede, modelagem pelo método ADC-M.

De forma a obter um indicador numérico do grau de proximidade deste conjunto de formas de onda, foi calculado o erro  $(\varepsilon_x)$ , definido como a média da magnitude das diferenças entre os vetores espaciais obtidos em cada ferramenta, divididas pela magnitude do vetor espacial calculado pelo software de *benchmark*, conforme mostra (6):

$$\varepsilon_{x} = \sum_{1}^{n} \frac{\left| \overline{\iota^{inv}} - \overline{\iota_{x}^{FXP}} \right|}{\left| \overline{\iota^{inv}} \right|} / n. \tag{6}$$

A definição de vetor espacial é dada por:

$$\vec{\iota^{inv}} = i_a^{inv} + i_b^{inv} \cdot e^{\frac{j2\pi}{3}} + i_c^{inv} \cdot e^{-\frac{j2\pi}{3}};$$

$$\vec{\iota_x^{FXP}} = i_a^{FXP} + i_b^{FXP} \cdot e^{\frac{j2\pi}{3}} + i_c^{FXP} \cdot e^{-\frac{j2\pi}{3}}.$$

(7)

Onde n corresponde ao número de amostras instantâneas consideradas (40000 no período de 40 ms apresentado na Figura 9) e x é a abordagem de representação de chaves utilizada. O resultado da avaliação de (6), para três ensaios, é apresentado na Tabela III, onde se observa que a modelagem G-ADC é a mais acurada e o método ADC tradicional é o menos exato. Observa-se também que a performance da estratégia ADC-M é próxima à obtida pelo método G-ADC.

TABELA III Avaliação do Indicador de Erro  $\varepsilon_x$ na Validação Off-line

| Abordagem               | Rede<br>constante | Afundamento tensão (80%) | Variação freq.<br>(-2,5 Hz) |

|-------------------------|-------------------|--------------------------|-----------------------------|

| Resistência<br>variável | 0,33 %            | 0,50%                    | 0,35%                       |

| ADC<br>tradicional      | 3,73%             | 3,25%                    | 3,68%                       |

| G-ADC                   | 2,24%             | 2,02%                    | 2,49%                       |

| ADC-M<br>(proposta)     | 2,27%             | 2,13%                    | 2,55%                       |

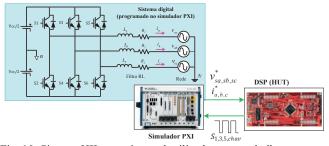

## C. Validação em Tempo Real com Bancada Experimental HIL

1) Descrição da bancada: A bancada HIL utilizada neste trabalho, mostrada na Figura 10, está composta pelo simulador PXI em tempo real e por um DSP, modelo TMS320F28337S da Texas Instruments, que faz o papel de equipamento sob ensaio (ESE). Este DSP controla o conversor eletrônico modelado no simulador PXI. Para isto, recebe sinais analógicos representativos das grandezas do sistema e executa a função de controle da Figura 7 de forma a determinar os pulsos de chaveamento do conversor (S<sub>1,3,5,chav</sub>). O simulador PXI em tempo real, por sua vez, recebe estes pulsos de chaveamento e recalcula o comportamento das grandezas do sistema.

Fig. 10. Sistema HIL experimental utilizado neste trabalho.

2) Resultados obtidos: A Figura 11.a mostra as formas de onda ajustadas das variáveis exportadas pelo SDTR (tensão no PCC para a fase a ( $v_{sa}^{D/A}$ ) e as três correntes do lado CA do inversor ( $i_a^{D/A}$ ,  $i_b^{D/A}$  e  $i_c^{D/A}$ )). O referido ajuste consiste em subtrair, das ondas medidas pelo osciloscópio, um nível CC de 1,5 V e multiplicar o resultado por um fator de escala (560/1,5 para as ondas de corrente, e 400/1,5 para a onda de tensão). No ensaio da Figura 11.a é realizada uma mudança na referência de potência ativa  $(P_{ref})$ , passando de 0,5 pu para 0,85 p.u com fator de potência unitário. A figura mostrada é relativa à modelagem pela técnica ADC-M, os resultados obtidos com as outras abordagens são similares e não foram apresentados por simplicidade. Pode ser visto um comportamento satisfatório do controlador, no qual o ponto de operação é modificado, conforme desejado, em menos de meio ciclo, mantendo o fator de potência próximo ao unitário. Destaca-se que a resolução temporal destas ondas é de 50 µs, razão pela qual não é possível ver o ripple de chaveamento nas ondas de corrente.

Fig. 11. Comportamento do VSC diante mudança de referência de potência ativa. (a) Resultados experimentais do SDTR - chaves modeladas com a técnica ADC-M, (b) resultados de simulação off-line.

A Figura 11.b, por sua parte, corresponde aos resultados obtidos com o simulador off-line Simulink®, considerando o mesmo evento e a mesma estrutura de controle. Destaca-se que as escalas de tensão (direita) e de corrente (esquerda) nesta figura foram escolhidas de tal forma que permitissem uma comparação direta com as medições da bancada HIL. Comparação que mostra comportamentos dinâmicos muito semelhantes (erro equivalente  $\varepsilon_{ADC-M}$  de 3,8% nas ondas de corrente), que validam a ferramenta desenvolvida na operação em laço fechado com o microcontrolador.

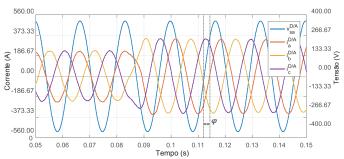

De modo similar, na Figura 12 são apresentadas as mesmas formas de onda ajustadas experimentais quando o inversor é controlado para injetar potência ativa e reativa, neste caso a potência  $Q_{ref}$  foi modificada de 0 pu para -0,5 pu, mantendo  $P_{ref} = 0,5$  pu, o que representa um FP  $(\cos(\varphi))$  de 0,707 ao final do evento. Ponto de operação que eventualmente pode ser utilizado para contribuir no controle de tensão do sistema de distribuição ao qual o inversor esteja

conectado. Observa-se novamente um comportamento satisfatório do controlador.

Fig. 12. Resultados experimentais do SDTR diante mudança da potência reativa. Chaves modeladas com a técnica ADC-M.

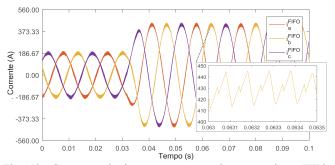

Na Figura 13 são mostradas as correntes armazenadas no registro FIFO no ensaio de fator de potência unitário, destacando uma visão ampliada, com duração de 500 μs, para uma das fases. Isto permite observar o detalhamento do *ripple* de corrente do modelo chaveado do conversor.

Fig. 13. Correntes do inversor armazenadas no registro FIFO. Chaves modeladas com a técnica ADC-M.

#### D. Sistemas Elétricos Adicionais

Com o intuito de verificar a aplicabilidade da técnica ADC-M para topologias de conversores diferentes da apresentada na Figura 6, dois sistemas elétricos adicionais foram modelados no SDTR: i) um conversor CC/CC buck, conforme topologia apresentada em [5] e ii) um conversor CC/CA multinível PUC5 monofásico conectado a carga RL, conforme topologia definida em [24]. Sucintas descrições destes sistemas, seus controladores e os principais resultados obtidos são realizadas nesta subseção.

1) Conversor buck: Seus parâmetros são: tensão de entrada  $(V_a)=100$  V; resistência da carga (R)=4,7 Ω; indutância (L)=1,8 mH; capacitância (C)=4,7 μF; passo de solução  $(\Delta t)=1$  μs; frequência de chaveamento  $(f_{ch})=20$  kHz e  $G_s=1$  pu. O controle programado no DSP para comando deste conversor consiste em um controlador PI que utiliza como entrada o erro entre a referência e o valor atual da tensão de saída, e dá como saída o ciclo de trabalho da onda PWM da chave. Por outro lado, (8) mostra a expressão utilizada para determinar o estado de comutação  $(S_D^{n+1})$  do diodo em antiparalelo, característico desta topologia.

$$S_D^{n+1} = S_D^n \cdot (i_D^n \ge 0) + \overline{S_D^n} \cdot (v_D^n \ge 0)$$

(8)

Onde  $i_D^n$  e  $v_D^n$  são a corrente e tensão no instante anterior de simulação, respectivamente.

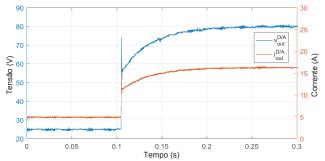

A Figura 14 mostra o resultado obtido na bancada experimental para a tensão de saída do conversor quando é

aplicada uma mudança de referência, de 25 V para 80 V. Observa-se que o sistema tem um tempo de estabelecimento de 110 ms. A comparação deste resultado com o obtido mediante simulação off-line dá como resultado um indicador de erro de tensão de 1,2%.

Fig. 14. Resultado experimental para uma mudança de tensão de referência no conversor *buck*, técnica ADC-M.

2) Conversor PUC5 monofásico: Esta topologia, proposta por Vahedi et al. [24], consiste em um conversor CC/CA de três níveis composto, na sua versão monofásica, por dois elos CC e seis chaves controláveis. Os parâmetros utilizados no modelo programado no SDTR são: tensão  $CC_1(V_1) = 100 \text{ V}$ ; tensão  $CC_2(V_2) = 50 \text{ V}$ ; carga  $(R) = 1,8 \Omega$  e (L) = 2,31 mH; passo de solução  $(\Delta t) = 1$  µs; frequência do controlador  $(f_c) = 20$  kHz; frequência de chaveamento  $(f_{ch}) = 2$  kHz e  $G_s = 1$  pu. Por simplicidade é utilizado um controle em laço aberto que aplica o esquema PWM proposto em [24], no qual são utilizadas quatro portadoras deslocadas verticalmente e uma lógica especial de chaveamento, para sintetizar a tensão de referência na saída do conversor.

A Figura 15 mostra os resultados experimentais da bancada HIL para a tensão e corrente na carga quando a referência de tensão senoidal de 60 Hz com valor de pico de 90 V. Uma vez que neste caso os instantes de chaveamento coincidem com os instantes de execução do controlador é possível observar de forma detalhada a onda chaveada da tensão de saída, bem como o *ripple* da corrente da carga. O indicador de erro  $\varepsilon_x$  entre o resultado experimental e de simulação off-line para a corrente de carga foi de 2,7%.

Fig. 15. Resultado experimental das variáveis de saída do conversor PUC5 em estado estável, técnica ADC-M.

#### V - AVALIAÇÃO COMPARATIVA DA TÉCNICA PROPOSTA

#### A. Uso de Recursos do Módulo FPGA

A Tabela IV mostra as principais características de compilação do módulo FPGA para cada um dos sistemas elétricos e métodos de representação de chaves utilizados

neste trabalho. Destaca-se que, como consequência da metodologia de implementação utilizada, os tempos de execução de cada sistema são iguais para todos os métodos: 730 ns para o sistema da Figura 6, 683 ns para o conversor PUC5 e 600 ns para o conversor buck. Observa-se que, para todos os sistemas, o método G-ADC é aquele que apresenta maior tempo de compilação e que faz maior uso de recursos de hardware. Destaca-se que os métodos que utilizam (2) em vez de (3) para calcular  $j_s^{n+1}$  (ADC e ADC-M) requerem menos recursos das unidades de DSP48 da FPGA (37% para o sistema da Figura 6, 38% para o conversor PUC5 e 29% para o conversor buck). Ao comparar a Tabela IV com o resultado da análise de exatidão da Tabela III, observa-se que a técnica ADC-M cumpre o objetivo de oferecer um nível de exatidão similar ao método G-ADC, porém com menor uso de recursos. Por outras palavras, essa técnica é capaz de representar maior quantidade de elementos de circuito com o mesmo hardware de simulação.

TABELA IV Características de Compilação do Módulo FPGA

| Características de Compilação do Modulo FFGA                 |                   |                        |                      |  |

|--------------------------------------------------------------|-------------------|------------------------|----------------------|--|

| Sistema<br>elétrico                                          | Método            | Tempo de<br>compilação | Uso de recursos FPGA |  |

| Conversor<br>CC/CA trifăsico<br>conectado à<br>rede (Fig. 6) | ADC               | 29 min.                | FPGA slices: 50,4%   |  |

|                                                              |                   |                        | DSP slices: 16,1%    |  |

|                                                              | G-ADC             | 37 min.                | FPGA slices: 52,2%   |  |

|                                                              |                   |                        | DSP slices: 25,5%    |  |

|                                                              | ADC -M            | 32 min.                | FPGA slices: 51,7%   |  |

|                                                              | (Proposta)        | 32 IIIII.              | DSP slices: 16,1%    |  |

| Conversor<br>CC/CC buck                                      | ADC               | 22 min.                | FPGA slices: 33,8%   |  |

|                                                              |                   |                        | DSP slices:6,2 %     |  |

|                                                              | G-ADC             | 24 min.                | FPGA slices: 34,4%   |  |

|                                                              |                   |                        | DSP slices: 8,8%     |  |

|                                                              | ADC -M            | 22 min.                | FPGA slices: 34,2%   |  |

|                                                              | (Proposta)        | 22 111111.             | DSP slices: 6,2%     |  |

| Conversor<br>CC/CA PUC 5                                     | ADC               | 32 min.                | FPGA slices: 39,6%   |  |

|                                                              |                   |                        | DSP slices: 12,2%    |  |

|                                                              | G-ADC             | 38 min.                | FPGA slices: 44,0%   |  |

|                                                              |                   |                        | DSP slices: 19,7%    |  |

|                                                              | ADC -M            | 36 min.                | FPGA slices: 43,6%   |  |

|                                                              | (Proposta) 36 mm. | 30 IIIII.              | DSP slices: 12,2%    |  |

#### B. Desempenho dinâmico

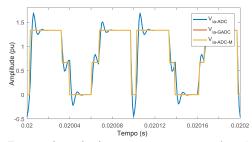

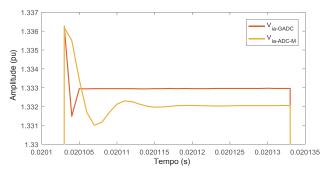

Na Figura 16 são comparadas as formas de onda da tensão na saída do inversor do sistema da Figura 6 (sinal  $v_{ia}$ ) para os três métodos ADC de modelagem utilizados neste trabalho, considerando um período equivalente a dois ciclos PWM. Nela resultam evidentes os transientes numéricos originados após um evento de chaveamento no caso da representação ADC tradicional. Além de significar erros de modelagem, estes transientes são responsáveis por consideráveis perdas de potência virtuais, um defeito conhecido deste método.

Fig. 16. Formas de onda da tensão  $v_{ia}$  para os três métodos de modelagem de chaves utilizados neste trabalho.

O desempenho das técnicas G-ADC e ADC-M, por outro lado, é aprimorado, sendo útil a Figura 17, com uma visão *zoom*, para avaliar seus transientes numéricos póschaveamento. Conforme mostrado, o método G-ADC proporciona de fato o transiente com melhor amortecimento, sendo necessários apenas dois passos de simulação após a mudança de estado para que a onda chegue ao seu valor final. O método ADC-M apresenta uma atenuação mais lenta, no entanto, os valores absolutos dos erros numéricos são suficientemente pequenos para não comprometer a exatidão da representação, como mostra a Tabela III.

Fig. 17. Visão *zoom* das formas de onda da tensão  $v_{ia}$  para os métodos G-ADC e ADC-M.

#### VI - CONCLUSÕES

Neste artigo foi proposta uma técnica para modelagem de chaves semicondutoras para simulação em tempo real, baseada no método generalizado de Wang et al. (G-ADC) [14]. A utilização desta técnica na modelagem em tempo real de três sistemas elétricos, utilizando uma plataforma desenvolvida experimentalmente a partir de hardware genérico como SDTR, permitiu avaliar suas características de desempenho. As análises comparativas apresentadas mostraram que o uso de um algoritmo para inicialização, a cada instante de chaveamento, da corrente  $j_s^{n+1}$  é uma alternativa eficiente para obter uma satisfatória relação entre a exatidão da representação e o uso de recursos de hardware. Assim, a técnica proposta (ADC-M) mostrou um nível de exatidão similar ao método G-ADC, ou seja, melhor do que o obtido pelo método ADC, porém com menor uso dos recursos de hardware do módulo FPGA do que no método G-ADC. Esta comprovação faz da técnica proposta uma abordagem vantajosa quando a capacidade do hardware empregado como simulador seja um limitante.

#### **AGRADECIMENTOS**

Os autores agradecem o apoio do Centro de Pesquisas de Energia Elétrica – Cepel. O presente trabalho foi realizado com apoio da Coordenação de Aperfeiçoamento de Pessoal de Nível Superior Brasil (CAPES) - Código de Financiamento 001.

## REFERÊNCIAS

[1] M. D. Omar Faruque *et al.*, "Real-Time Simulation Technologies for Power Systems Design, Testing, and Analysis," *IEEE Power Energy Technol. Syst. J.*, vol. 2, no. 2, pp. 63–73, Jun. 2015.

- [2] A. Isaacs, "Simulation Technology: The Evolution of the Power System Network [History]," *IEEE Power Energy Mag.*, vol. 15, no. 4, pp. 88–102, Jul. 2017.

- [3] X. Guillaud *et al.*, "Applications of Real-Time Simulation Technologies in Power and Energy Systems," *IEEE Power Energy Technol. Syst. J.*, vol. 2, no. 3, pp. 103–115, Sep. 2015.

- [4] R. Brundlinger *et al.*, "Lab tests: Verifying that smart grid power converters are truly smart," *IEEE Power and Energy Magazine*, vol. 13, no. 2, IEEE, pp. 30–42, Feb. 2015.

- [5] N. Mohan, T. M. Undeland, and W. P. Robbins, *Power Electronics Converters, Applications, and Design*, 2nd ed. New York: John Willey & Sons, Inc, 1995.

- [6] M. Matar and R. Iravani, "FPGA Implementation of the Power Electronic Converter Model for Real-Time Simulation of Electromagnetic Transients," *IEEE Trans. Power Deliv.*, vol. 25, no. 2, pp. 852–860, Apr. 2010.

- [7] M. S. Vekić, S. U. Grabić, D. P. Majstorović, I. L. Čelanović, N. L. Čelanović, and V. A. Katić, "Ultralow Latency HIL Platform for Rapid Development of Complex Power Electronics Systems," *IEEE Trans. Power Electron.*, vol. 27, no. 11, pp. 4436–4444, Nov. 2012.

- [8] Wei Li, G. Joos, and J. Belanger, "Real-Time Simulation of a Wind Turbine Generator Coupled With a Battery Supercapacitor Energy Storage System," *IEEE Trans. Ind. Electron.*, vol. 57, no. 4, pp. 1137–1145, Apr. 2010.

- [9] Y. Chen and V. Dinavahi, "FPGA-Based Real-Time EMTP," *IEEE Transactions on Power Delivery*, vol. 24, no. 2, pp. 892–902, Apr. 2009.

- [10] E. Fernandes, D. Huller, A. Oliveira, M. Corrêa, and W. Santos, "Real-time Simulator of Permanent-magnet Synchronous Motor Based on Programmable Logical Devices," *Eletrônica de Potência*, vol. 20, no. 3, pp. 244–253, Jun./Aug. 2015.

- [11] H. Dommel, "Digital Computer Solution of Electromagnetic Transients in Single-and Multiphase Networks," *IEEE Trans. Power Appar. Syst.*, vol. PAS-88, no. 4, pp. 388–399, Apr. 1969.

- [12] P. Pejovic and D. Maksimovic, "A method for fast time-domain simulation of networks with switches," *IEEE Trans. Power Electron.*, vol. 9, no. 4, pp. 449–456, Jul. 1994

- [13] R. Razzaghi, M. Paolone, and F. Rachidi, "A general purpose FPGA-based real-time simulator for power systems applications," *IEEE PES ISGT Eur. 2013*, pp. 1–5, Oct. 2013.

- [14] K. Wang, J. Xu, G. Li, N. Tai, A. Tong, and J. Hou, "A Generalized Associated Discrete Circuit Model of Power Converters in Real-Time Simulation," *IEEE Trans. Power Electron.*, vol. 34, no. 3, pp. 2220–2233, Mar. 2019.

- [15] W. Ji, K. Wang, G. Li, J. Zhuang, S. Li, and J. Li, "A real-time simulation algorithm for power electronics circuit considering multiple switching events and its application on PXI platform," 2016 IEEE 16th Int. Conf. Environ. Electr. Eng., pp. 1–6, Jun. 2016.

- [16] A. Yazdani and R. Iravani, *Voltage-sourced converters in power systems: modeling, control, and applications.* Wiley Online Library, 2010.

- [17] PSCAD, "EMTDC Users Guide V4.6.0." Manitoba Hydro International Ltd., 2017.

- [18] R. Razzaghi, C. Foti, M. Paolone, and F. Rachidi, "A novel method for the optimal parameter selection of discrete-time switch model," *Proc. 10th Int. Conf. Power Syst. Transients (IPST 2013)*, no. EPFL-CONF-188222, pp. 1–7, Jul. 2013.

- [19] T. Maguire and J. Giesbrecht, "Small time-step (< 2us)

- VSC model for the real time digital simulator," *Int. Conf. Power Syst. Transients*, Jun. 2005.

- [20] C. Dufour, "Method and system for reducing power losses and state-overshoots in simulators for switched power electronic circuit," US 2016/0314230 A1, 2016.

- [21] L. G. B. Rolim, D. R. da Costa, and M. Aredes, "Analysis and software implementation of a robust synchronizing PLL circuit based on the pq theory," *IEEE Trans. Ind. Electron.*, vol. 53, no. 6, pp. 1919–1926, Nov. 2006.

- [22] R. H. Park, "Abridgment of two-reaction theory of synchronous machines generalized method of analysis Part I," *J. A.I.E.E.*, vol. 48, no. 3, pp. 194–194, Mar. 1929.

- [23] National Instruments, "Testando e depurando o código do LabVIEW FPGA," *Tutoriais*, 2014. [Online]. Available: http://www.ni.com/tutorial/51862/pt/. [Accessed: 30-May-2019].

- [24] H. Vahedi, P.-A. Labbé, and K. Al-Haddad, "Sensor-less five-level packed U-cell (PUC5) inverter operating in stand-alone and grid-connected modes," *IEEE Trans. Ind. Informatics*, vol. 12, no. 1, pp. 361–370, Oct. 2015.

#### DADOS BIOGRÁFICOS

Oscar Solano Rueda é engenheiro eletricista (2011) pela Universidad Industrial de Santander (UIS) e mestre em Engenharia Elétrica (2014) pela Universidade Federal do Rio de Janeiro (UFRJ). Atualmente é estudante de doutorado na UFRJ na área de simulação de conversores em tempo real. Desde 2014 é pesquisador do Centro de Pesquisas de Energia Elétrica — Cepel. Suas áreas de interesse são redes elétricas inteligentes, simulação em tempo real, ensaios hardware-in-the-loop e controle de conversores eletrônicos de potência.

Cesar J. Bandim possui graduação em Engenharia Eletrônica (1988) e mestrado em Engenharia Elétrica (1991) pela Universidade Federal do Rio de Janeiro. Pesquisador do Centro de Pesquisas de Energia Elétrica — Cepel desde 1989, atuando nos seguintes temas: medição de energia elétrica, desenvolvimento de soluções para redução de perdas elétricas, medição sincrofasorial e redes elétricas inteligentes. Participa do comitê técnico CE-003:013.001 para modificação/elaboração de normas técnicas ABNT relacionadas a medidores de energia elétrica e de grupos de trabalho a convite do Inmetro.

<u>Luís Guilherme B. Rolim</u> nasceu em Niterói, RJ em 1966. É formado em Engenharia Elétrica com Graduação e Mestrado pela Universidade Federal do Rio de Janeiro (UFRJ) em 1989 e 1993, respectivamente. Recebeu o título de Dr.-Ing. pela Technical University Berlin, Alemanha, em 1997. Desde 1990 é professor do curso de Engenharia Elétrica na UFRJ, nas áreas de eletrônica de potência, acionamentos e controle com microprocessadores. Tem cerca de 100 artigos publicados em conferências e revistas técnicas nacionais e internacionais.