Received July 09, 2024; accepted August 01, 2024; Date of publication August 19, 2024. The review of this paper was arranged by Associate Editor Allan F. Cupertino and Editor-in-Chief Heverton A. Pereira. Digital Object Identifier http://doi.org/10.18618/REP.e202428

# Estudo e Proposta de um Conversor Boost de Elevado Ganho e Reduzida Tensão nas Chaves

Lucas Romeiro 1, Lúcio dos Reis Barbosa 1, Newton da Silva 1, Leonimer Flávio de Melo<sup>1</sup>

> <sup>1</sup>Universidade Estadual de Londrina, Departamento de Engenharia Elétrica, Londrina – PR, Brasil. e-mail: lucas.romeiro96@uel.br, lbarbosa@uel.br, newton.silva@uel.br, leonimer@uel.br.

**RESUMO** Elevado ganho de tensão é comumente necessário em aplicações que envolvem fontes alternativas de energia. Contudo, nesses casos, os conversores elevadores básicos apresentam limitações devidas, essencialmente, à necessidade de operação sob razões cíclicas extremas. Nesse contexto, o presente artigo apresenta a proposta e estudo de uma nova topologia não isolada de elevado ganho, obtida a partir da integração de estruturas. A máxima tensão de bloqueio suportada pelas chaves semicondutoras corresponde à metade da tensão de saída, possibilitando a utilização de componentes com menor resistência de condução. Ainda, a estratégia de comando utilizada para o acionamento das chaves, baseada em pulsos defasados, possibilita a utilização de componentes magnéticos compactos. Tais características possibilitam a operação do conversor com elevado ganho, eficiência e densidade de potência. A validação experimental é realizada a partir de um protótipo de 250 W, através do qual o conversor obteve um ganho de aproximadamente seis vezes, com um rendimento em plena de carga superior à 89%.

PALAVRAS-CHAVE Baixo esforço de tensão, conversor CC-CC, conversor multiestágio, conversor multinível.

## A Novel High-gain Boost Converter with Reduced Switch Voltage Stress

**ABSTRACT** A high voltage gain is commonly required in applications involving alternative energy sources. However, in these situations, basic converters present limitations mainly due to the need for operation under extreme duty ratios. In this context, this paper presents the proposal and study of a new non-isolated topology with high gain, obtained from the integration of structures. The maximum blocking voltage supported by the semiconductor switches corresponds to half of the output voltage, allowing the use of components with lower conduction resistance. Additionally, the control strategy used for switching the switches, based on phased pulses, enables the use of compact magnetic components. These characteristics enable the converter to operate with high gain, efficiency, and power density. Experimental validation is carried out using a 250 W prototype, through which the converter achieved a gain of approximately six times, with a full load efficiency exceeding 89%.

**KEYWORDS** DC-DC converter, multi-level converter, multi-stage converter, reduced voltage stress.

## I. INTRODUÇÃO

O uso eficiente de fontes alternativas de energia, dentre as quais se destacam a energia solar fotovoltaica (do inglês, photovoltaic - PV), energia eólica e células a combustível, é um tópico cada vez mais urgente impulsionado pela necessidade de diversificação da matriz energética global, além de questões ambientais [1]. Devido às suas características, a energia solar fotovoltaica apresenta crescimento acelerado, sendo especialmente empregada na configuração de conversores integrados ao módulo (module-integratedconverter - MIC) uma vez que, deste modo, possibilita a extração da máxima potência de cada módulo PV [1], [2]. Contudo, nesta configuração, a utilização de conversores de elevado ganho operando em médias e baixas potências é indispensável para a adequação dos baixos níveis de tensão provenientes dos módulos solares àqueles necessários para a correta alimentação do barramento CC de inversores CC-CA conectados à rede elétrica [1]-[3].

Tratando-se de aplicações onde um elevado ganho de tensão se faz necessário, a utilização de conversores com acoplamento magnético se mostra como uma escolha óbvia, uma vez que o ganho estático pode ser ajustado não apenas pelo ciclo de trabalho, mas também pela relação de espiras do transformador [4], [5]. Entretanto, nestas estruturas, os semicondutores são submetidos a elevados picos de tensão durante as comutações devidos à indutância de dispersão. Sobretensões também podem ocorrer em conversores que empregam indutores acoplados, porém, o compartilhamento do núcleo magnético leva a uma redução do volume, elevando a densidade de potência da estrutura [2], [6].

Em aplicações nas quais a isolação galvânica não se faz necessária, o conversor boost convencional é comumente utilizado para elevar a tensão devido à sua simples estrutura e reduzido número de componentes. No entanto, na prática, o conversor não é capaz de fornecer elevado ganho estático devido às não idealidades dos componentes e necessidade de operação com ciclos de trabalho extremos [1], [2], [7], [8]. Em vista disso, inúmeras técnicas foram propostas para ampliar o ganho estático fornecido pelo conversor convencional, conforme a vasta revisão realizada em [6], as quais incluem indutores chaveados [9], capacitores chaveados [10] e indutores acoplados [11].

Ganhos estáticos mais significativos podem ser obtidos a partir da associação sequencial de estruturas, resultando nos conversores em cascata ou ainda, integrados com uma única chave resultando nos comumente chamados conversores quadráticos [12], [13]. Esta é uma solução notável uma vez que o ganho estático total é obtido através da multiplicação entre o ganho estático de cada estágio quem compõe a estrutura. Todavia, esforcos significativos de tensão são observados sobre as chaves semicondutoras, tornando indispensável a utilização de componentes mais robustos e de elevada resistência de condução (Drain-to-source-onresistance -  $R_{DS(on)}$ ) [7], [12].

Reduzidos esforços de tensão são obtidos a partir da utilização de conversores multiníveis, possibilitando a divisão dos esforços de tensão impostos aos semicondutores de saída [13], [14]. Além disso, recentemente, conversores três-níveis, baseados em estruturas multiníveis, têm sido propostos como parte integrante do condicionamento de fontes alternativas de energia de baixa e média potência, a fim de aliviar os esforços de tensão nos semicondutores e reduzir o volume dos elementos reativos. Em [15], a célula de comutação de três-níveis (*Three-level-switching-cell - TLSC*) é integrada ao conversor boost quadrático a fim de se obter um conversor de elevado ganho com reduzido esforço de tensão suportado pelas chaves. Não obstante, [12] detalha uma técnica utilizada para obtenção de estruturas derivadas de conversores multiníveis.

Por outro lado, [16] propõe uma nova abordagem para a obtenção de conversores de elevado ganho a partir da combinação de células em cascata e multinível, com a finalidade de integrar as características de ambas as estruturas em um único conversor. Ganhos estáticos mais significativos foram obtidos em [5] e [17] a partir da integração dos conversores boost quadrático e flyback, resultando em um conversor de elevado ganho, ideal para aplicações de elevada potência. De modo similar, em [2] uma família de conversores concebidos a partir da conexão diferencial de dois conversores, com a integração, ou não, de células de ganho, é proposta.

Conversores de elevado ganho derivados da estrutura buck-boost foram recentemente estudas nos trabalhos [18] e [19] dentre os quais buscam reduzir a tensão suportada pelas chaves e as ondulações na corrente de entrada. Ainda, destacam-se topologias bidirecionais utilizadas no condicionamento de fontes alternativas de energia, conforme [20].

A partir do exposto, o presente artigo propõe uma nova topologia de conversor CC-CC obtida a partir da integração da célula de comutação de três-níveis (TLSC) ao conversor boost quadrático modificado estudado em [21]. A estrutura resultante alcança elevado ganho estático, reduzido esforço de tensão nas chaves semicondutoras, reduzidos esforços de tensão sobre os semicondutores intermediários, além de uma reduzida tensão média sobre o capacitor intermediário. A utilização da TLSC possibilita, ainda, a utilização de componentes magnéticos compactos sem que as perdas de comutação nas chaves sejam agravadas.

Na Seção II a estrutura proposta, seu princípio de funcionamento em modo de condução contínua (MCC), ganho estático, principais formas de onda e projeto dos componentes é abordada. Uma análise de desempenho e performance é realizada nas Seções III e IV. Para o fim, as Seções V e VI apresentam, respectivamente, os resultados experimentais e considerações finais a respeito do estudo realizado.

## II. PRINCÍPIO DE OPERAÇÃO

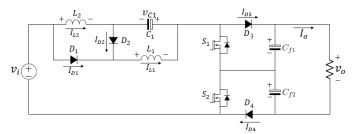

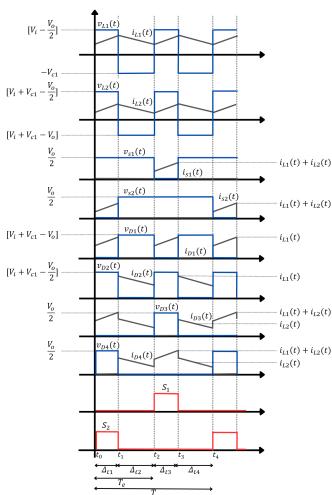

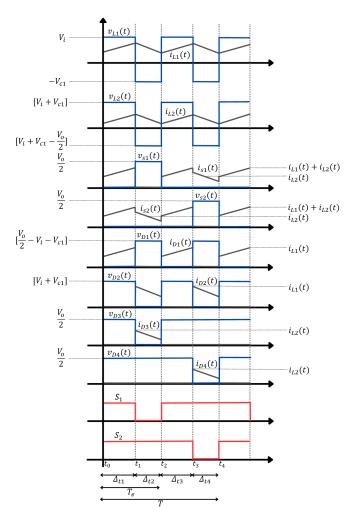

O conversor proposto é apresentado na Figura 1 e é composto por duas chaves  $(S_1 \ e \ S_2)$ , quatro diodos  $(D_1 \ a \ D_4)$ , dois indutores ( $L_1$  e  $L_2$ ), um capacitor de acoplamento ( $C_1$ ), além de dois capacitores de filtro ( $C_{f1}$  e  $C_{f2}$ ). A estratégia de comando adotada para a comutação das chaves é baseada em dois sinais modulados por largura de pulso (do inglês, pulse width modulation - PWM) simétricos, de mesma razão cíclica e frequência, e defasados de meio período entre si. Tal estratégia impõe ao circuito a possibilidade de operar em duas regiões distintas, dependendo se o ciclo de trabalho (D)é maior ou menor que 50%, definidas por Região 1 (D <(0,50) e Região 2 (D>0,50). Os sinais de comando são apresentados nas duas primeiras formas de onda das Figuras

FIGURA 1. Conversor quadrático multinível proposto.

O princípio de operação e dimensionamento dos componentes é realizado para ambas as regiões de operação e considera que o conversor opera no modo de condução contínua e que os componentes são ideais. Ainda, adota-se que  $C_{f1} = C_{f2}$ .

## A. Operação com D < 0,50

Abaixo são descritas as etapas de operação, principais formas de onda e ganho estático ideal para o conversor operando na

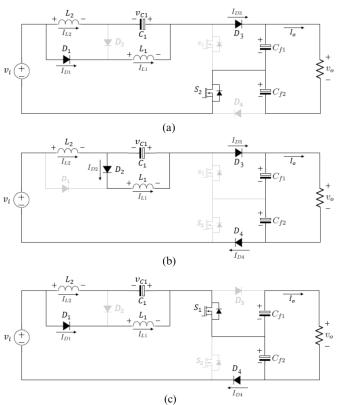

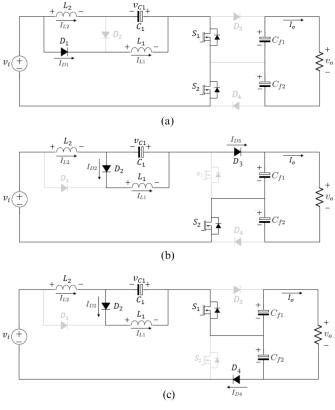

FIGURA 2. Etapas de operação com D < 0,50. (a) Primeira etapa. (b) Segunda e quarta etapa. (c) Terceira etapa.

Região 1. As etapas de operação são ilustradas na Figura 2 enquanto que a Figura 3 apresenta as principais formas de onda.

- Primeira etapa de operação ( $\Delta_{t1}$ ) (Figura 2.a): Nesta etapa, a chave  $S_2$  está em condução enquanto que  $S_1$  e os diodos  $D_2$  e  $D_4$  estão bloqueados. A corrente dos indutores cresce linearmente, conforme indica a Figura 3.  $C_{f2}$  é descarregado fornecendo parte da energia consumida pela carga.

- **Segunda etapa de operação**  $(\Delta_{t2})$  (Figura 2.b): Durante esta etapa, ambas as chaves estão bloqueadas e os indutores passam a fornecer a energia previamente armazenada, vide Figura 3. O indutor  $L_1$  fornece energia ao capacitor  $C_1$ , já o indutor  $L_2$  e os capacitores de filtro alimentam a carga.

- Terceira etapa de operação ( $\Delta_{t3}$ ) (Figura 2.c): Esta etapa tem início no instante que a chave  $S_1$  entra em condução com  $S_2$  ainda em bloqueio. Os indutores voltam a armazenar energia. O capacitor de acoplamento é descarregado pela corrente do indutor  $L_2$ , enquanto o capacitor  $C_{f1}$  é descarregado fornecendo energia à carga.

- Quarta etapa de operação ( $\Delta_{t4}$ ) (Figura 2.b): A última etapa de operação tem início com o bloqueio da chave  $S_1$  e é análoga à segunda etapa.

FIGURA 3. Principais formas de onda com D < 0,50.

Com base nos sinais de comando, obtêm-se os intervalos de tempo de cada etapa de operação em função do ciclo de trabalho conforme (1) e (2).

$$\Delta_{t1} = \Delta_{t3} = DT, \tag{1}$$

$$\Delta_{t2} = \Delta_{t4} = \frac{(1 - 2D)T}{2},\tag{2}$$

em que:

T - período de chaveamento,

$T_e$  - período efetivo de operação ( $T=2T_e$ ).

O ganho estático do conversor operando na Região 1 pode ser obtido partindo do princípio de que, em regime permanente, dentro de um período completo de comutação, a tensão média sobre os indutores é nula. Com base na Figura 3, a tensão média sobre os indutores  $L_1$  e  $L_2$  é dada por (3) e (4), respectivamente. Resolvendo para  $V_{C1}$  e igualando ambas as expressões, obtém-se o ganho estático dado por (5).

$$2(V_i - \frac{V_o}{2})\Delta_{t1} - 2V_{C1}\Delta_{t2} = 0, (3)$$

FIGURA 4. Etapas de operação com D > 0,50. (a) Primeira e terceira etapa. (b) Segunda etapa. (c) Quarta etapa.

$$2(V_i + V_{C1} - \frac{V_o}{2})\Delta_{t1} + 2(V_i + V_{C1} - V_o)\Delta_{t2} = 0, \quad (4)$$

$$G_{D<0,50} = \frac{V_o}{V_i} = \frac{1}{2D^2 - 2D + 1}.$$

(5)

### B. Operação com D > 0,50

O princípio de operação do conversor operando na Região 2 é descrito abaixo. As etapas de operação são apresentas na Figura 4 e as principais formas de onda na Figura 5.

- Primeira etapa de operação ( $\Delta_{t1}$ ) (Figura 4.a): Nesta etapa, ambas as chaves estão em condução e os diodos  $D_3$  e  $D_4$  ficam reversamente polarizados pelas tensões dos capacitores de filtro, assim como ilustra a Figura 5. Ambos os indutores armazenam energia, e a carga é alimentada pela associação em série dos capacitores  $C_{f1}$  e  $C_{f2}$  que descarregam-se.

- Segunda etapa de operação ( $\Delta_{t2}$ ) (Figura 4.b): Esta etapa inicia-se com o bloqueio de  $S_1$ . O indutor  $L_1$ passa a fornecer energia ao capacitor  $C_1$ , enquanto  $L_2$ fornece energia ao capacitor  $C_{f1}$  e à carga.

- Terceira etapa de operação ( $\Delta_{t3}$ ) (Figura 4.a): A terceira etapa é análoga à primeira, e refere-se a etapa de armazenamento de energia pelos indutores, vide Figura 5.

FIGURA 5. Principais formas de onda com D > 0,50.

**Quarta etapa de operação** ( $\Delta_{t4}$ ) - (Figura 4.c): A última etapa de operação corresponde ao bloqueio de  $S_1$ . Com isso,  $L_1$  volta a fornecer energia ao capacitor intermediário, enquanto que  $L_2$  fornece energia para a carga e ao capacitor  $C_{f2}$ .

Das formas de onda apresentadas na Figura 5, definem-se os intervalos de tempo de duração de cada etapa de operação em função do ciclo de trabalho, como expressa (6) e (7).

$$\Delta_{t1} = \Delta_{t3} = \frac{(2D-1)T}{2},$$

(6)

$$\Delta_{t2} = \Delta_{t4} = (1 - D)T. \tag{7}$$

Novamente, sabendo que em regime permanente a tensão média sobre os indutores é nula, é possível determinar a expressão que quantifica o ganho do conversor para a segunda região de operação. A tensão média sobre os indutores é dada por (8) e (9), respectivamente.

$$2V_i \Delta_{t1} - 2V_{C1} \Delta_{t2} = 0, (8)$$

$$2(V_i + V_{C1})\Delta_{t1} + 2(V_i + V_{C1} - \frac{V_o}{2})\Delta_{t2} = 0.$$

(9)

Resolvendo para  $V_{C1}$  e simplificando obtém-se

$$G_{D>0,50} = \frac{V_o}{V_i} = \frac{1}{2(1-D)^2},$$

(10)

que representa o ganho estático ideal do conversor proposto para a Região 2.

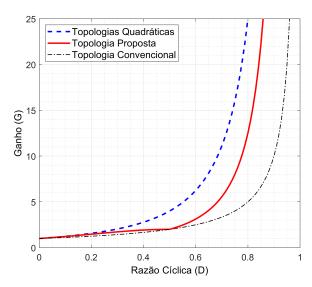

Para ambas as regiões de operação o conversor apresenta uma característica de ganho quadrático, possibilitando a obtenção de tensões mais elevadas que àquelas fornecidas pelo conversor boost convencional. Tal característica é evidenciada a partir da Figura 6, na qual um comparativo entre o ganho estático do conversor proposto, convencional e quadrático é apresentado.

FIGURA 6. Comparativo entre o ganho estático dos conversores proposto, convencional e quadrático.

Evidencia-se ainda, a partir das Figuras 3 e 5, que o período de operação dos indutores corresponde à metade do período total de chaveamento. Tal característica possibilita a utilização de componentes de menor indutância e de menor volume físico, elevando a densidade de potência da estrutura.

#### C. Esforcos de Tensão Sobre os Semicondutores

Os esforços de tensão nas chaves e diodos em função da tensão de saída  $V_o$ , para a primeira região de operação, são calculados por:

$$\begin{cases} V_{S1} = V_{S2} = \frac{V_o}{2} \\ V_{D1} = V_o D \\ V_{D2} = \frac{V_o}{2} (1 - 2D) \\ V_{D3} = V_{D4} = \frac{V_o}{2}. \end{cases}$$

(11)

Já para a segunda região de operação:

$$\begin{cases} V_{S1} = V_{S2} = \frac{V_o}{2} \\ V_{D1} = \frac{V_o}{2} (2D - 1) \\ V_{D2} = V_o (1 - D) \\ V_{D3} = V_{D4} = \frac{V_o}{2}. \end{cases}$$

(12)

#### D. Escolha das Indutâncias

As indutâncias  $L_1$  e  $L_2$  são calculadas a partir da relação tensão-corrente do indutor e são obtidas, em função de uma determinada ondulação de corrente ( $\Delta_{IL}$ ), conforme:

$$L_{1(D<0,50)} = \frac{V_o(4D^3 - 4D^2 + D)}{2\Delta_{IL1}f},$$

(13)

$$L_{1(D>0,50)} = \frac{V_o(1-D)^2(2D-1)}{\Delta_{IL1}f},$$

(14)

$$L_{2(D<0,50)} = \frac{V_o D(1-2D)}{2\Delta_{IL2} f},$$

(15)

$$L_{2(D>0,50)} = \frac{V_o(1-D)(2D-1)}{2\Delta_{II,2}f},$$

(16)

onde:

f - frequência de comutação.

A corrente dos indutores se relaciona com a corrente de carga  $I_o$  conforme (17)-(20).

$$I_{L1(D<0,50)} = \frac{I_o}{2D^2 - 2D + 1},\tag{17}$$

$$I_{L1(D>0,50)} = \frac{I_o}{2(1-D)^2},$$

(18)

$$I_{L2(D<0,50)} = \frac{I_o(1-2D)}{2D^2 - 2D + 1},\tag{19}$$

$$I_{L2(D>0,50)} = \frac{I_o}{(1-D)}. (20)$$

#### E. Ondulações de Tensão

As ondulações de tensão sobre os capacitores são devidas às variações de carga que ocorrem durante cada etapa de operação e podem ser mensuradas, em função de uma dada capacitância, pelas expressões (21)-(24).

$$\Delta_{V_{C1(D<0,50)}} = \frac{I_o D(1-2D)}{(2D^2-2D+1)C_1 f}, \qquad (21)$$

$$\Delta_{V_{C1(D>0,50)}} = \frac{I_o(2D-1)}{2(1-D)C_1 f},\tag{22}$$

$$\Delta_{V_{Cf1,2(D<0,50)}} = \frac{I_o D[(\frac{2-2D}{2D^2-2D+1})-1]}{C_{f1}f}, \qquad (23)$$

$$\Delta_{V_{Cf1,2(D>0,50)}} = \frac{I_o D}{C_{f1} f}.$$

(24)

#### III. COMPARAÇÃO DE PERFORMANCE

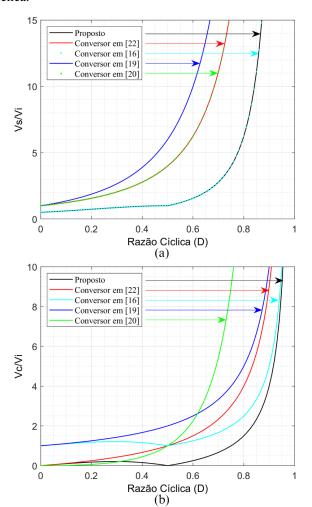

Com o objetivo de avaliar suas principais características, o conversor proposto é comparado com outras estruturas semelhantes de ganho quadrático presentes na literatura em termos de ganho estático, máxima tensão nas chaves e número de componentes, conforme apresentado na Tabela 1. Já na Figura 7 as tensões normalizadas na chave e sobre o capacitor intermediário são plotadas em função da razão cíclica.

FIGURA 7. Comparativo de performance. (a) Máxima tensão na chave. (b) Tensão média no capacitor intermediário

Inicialmente, observa-se que as estruturas analisadas demonstram uma relação quadrática para o ganho estático, possibilitando a obtenção de tensões mais significativas sem a necessidade de operação com uma razão cíclica extrema. O conversor proposto, bem como o estudado em [15], apresentam a menor tensão suportada pela chave, como evidencia a Figura 7.a, correspondendo à metade da tensão de saída, viabilizando a utilização de semicondutores com menor resistência de condução. A Figura 7.b mostra que o conversor proposto obtém a menor tensão sobre o capacitor de acoplamento, elo de conexão entre os estágios, em comparação com os demais. Além disso, embora compartilhe semelhanças

com [15], o conversor proposto impõe uma tensão significativamente menor ao capacitor de acoplamento. Essa característica viabiliza o uso de um componente com menor robustez, custo e volume. Finalmente, em relação ao número de componentes, [21] apresenta o menor valor, totalizando 8 componentes. [19] vem em seguida com 10 componentes, no entanto, utilizando 3 indutores para aumentar o ganho. Por fim, [15], [18] e a proposta utilizam 11 componentes cada, com 2 chaves e 2 indutores.

## IV. DISTRIBUIÇÃO DE PERDAS

Os cálculos e métodos utilizados para mensurar a potência dissipada nos componentes do conversor são baseados em [22] e apresentados a seguir. As correntes média e eficaz através dos componentes são obtidas a partir das Figuras 3 e 5 e considerando as expressões (17)-(20).

As perdas nos dispositivos semicondutores se dividem em duas parcelas referentes às perdas em condução  $(P_{on})$  e perdas durante a comutação  $(P_{sw})$ . As perdas nas chaves são estimadas conforme:

$$\begin{cases}

P_{S(on)} = R_{DS(on)} I_{S(rms)^2} \\

P_{S(sw)} = \frac{1}{2} [V_{DS} I_S f(t_r + t_f)]

\end{cases}$$

(25)

em que,  $V_{DS}$  é a tensão de bloqueio,  $I_S$  a corrente média em condução, f a frequência de chaveamento e  $t_r$  e  $t_f$  denotam, respectivamente, os tempos de entrada e saída de condução. Já as perdas nos diodos são calculadas por:

$$\begin{cases}

P_{D(on)} = V_{to}I_D + r_t I_{D(rms)}^2 \\

P_{D(sw)} = Q_{rr}V_D f

\end{cases}$$

(26)

com  $V_D$  sendo a tensão reversa máxima e  $Q_{rr}$  a carga de recuperação reversa, obtida a partir da folha de dados do fabricante.

As perdas nos elementos magnéticos subdividem-se em perdas ôhmicas  $(P_W)$  e perdas no núcleo  $(P_C)$ , estimadas por:

$$\begin{cases} P_W = r_L I_{rms}^2 \\ P_C = \Delta B_m^{2,4} (K_H f + K_E f^2) V_e \end{cases}$$

(27)

onde  $V_e$ ,  $K_H$  e  $K_E$  são coeficientes fornecidos pelo fabricante, e  $\Delta B_m$  é a excursão da densidade de fluxo.

Por fim, as perdas resistivas nos capacitores podem ser calculadas com base na resistência série equivalente  $(R_{SE})$ :

$$P_{cap} = R_{SE} I_{C(rms)}^2. (28)$$

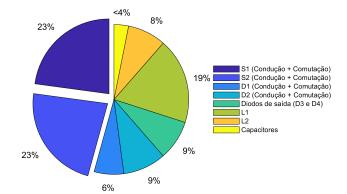

Para o dimensionamento teórico das perdas, os parâmetros dependentes da temperatura são obtidos a partir da folha de dados, para 125 °C, e considerados constantes. Deste modo, com base nos parâmetros de projeto apresentados na Tabela 2, o conversor obtém um rendimento teórico esperado de aproximadamente 91%. A dissipação de potência se distribui entre os componentes do circuito conforme ilustra o gráfico da Figura 8. Na qual fica evidente que as maiores

TABELA 1. Comparativo Entre Topologias.

| Topologia | Ganho Estático $(V_o/V_i)$ | Máxima Tensão<br>nas Chaves | Número de<br>Chaves | Número de<br>Diodos | Número de<br>Indutores | Número de<br>Capacitores |

|-----------|----------------------------|-----------------------------|---------------------|---------------------|------------------------|--------------------------|

| [21]      | $\frac{1}{(1-D)^2}$        | $V_o$                       | 1                   | 3                   | 2                      | 2                        |

| [15]      | $\frac{1}{2(1-D)^2}$       | $\frac{V_o}{2}$             | 2                   | 4                   | 2                      | 3                        |

| [18]      | $\frac{(1+D)}{(1-D)^2}$    | $V_o$                       | 2                   | 3                   | 2                      | 3                        |

| [19]      | $\frac{D^2}{(1-D)^2}$      | $\frac{V_o}{D^2}$           | 2                   | 2                   | 3                      | 3                        |

| Proposta  | $\frac{1}{2(1-D)^2}$       | $\frac{V_o}{2}$             | 2                   | 4                   | 2                      | 3                        |

FIGURA 8. Distribuição teórica de perdas.

perdas ocorrem nas chaves semicondutoras e são devidas, essencialmente, às elevadas correntes que circulam por estes elementos, característica essa, comumente observada em conversores sequenciais - obtidos a partir da associação em cascata de estruturas. Assim, é possível inferir que a magnitude da corrente que circula através da resistência de canal das chaves é um fator determinante para o desempenho do conversor e exerce uma influência significativa em sua curva de rendimento. Evidenciando que a redução nos esforços de tensão suportados por estes componentes é indispensável para a operação do conversor com significativa eficiência uma vez que possibilita a utilização de componentes com menor resistência de condução.

## V. RESULTADOS EXPERIMENTAIS

Para verificação do estudo teórico realizado, um protótipo experimental de 250 W foi montado. Os parâmetros nominais de projeto estão apresentados na Tabela 2. As tensões de entrada e saída correspondem a valores típicos encontrados em aplicações de fontes alternativas de energia conectadas à rede elétrica de 127 V. Já a frequência de operação é tomada levando em conta o dimensionamento dos elementos reativos, além das perdas de comutação. Os sinais de comando são gerados através do controlador digital de sinais (DSC), modelo TMS320F28335. O circuito é projetado para operar com D > 0,50, onde é capaz de obter ganhos estáticos significativos. Os componentes que compõem a estrutura, escolhidos com base em sua tensão nominal, máxima capacidade de corrente e disponibilidade, também são apresentados na Tabela 2. Os ensaios experimentais são conduzidos em malha aberta para o conversor operando no modo de condução contínua.

TABELA 2. Parâmetros de projeto.

| Parâmetro                 | Valor                                              |  |  |  |

|---------------------------|----------------------------------------------------|--|--|--|

| Tensão de entrada         | 35~V                                               |  |  |  |

| Tensão de saída           | 200 V                                              |  |  |  |

| Potência de saída         | 250~W                                              |  |  |  |

| Frequência de chaveamento | 50~kHz                                             |  |  |  |

| Indutor $L_1$             | EE 42/21/15 @ (200 $\mu$ H) @ 85 mΩ                |  |  |  |

| Indutor $L_2$             | EE 42/21/15 @ (572 $\mu$ H) @ 108 m $\Omega$       |  |  |  |

| Capacitor de acoplamento  | B41693 (1000 $\mu\mathrm{H})$ @ 27 m $\Omega$      |  |  |  |

| Capacitores de filtro     | B43624 (680 $\mu$ H) @ 55 m $\Omega$               |  |  |  |

| Chaves semicondutores     | IRFP260N @ 40 m $\Omega$                           |  |  |  |

| Diodos $D_1$ e $D_2$      | MBR10100 @ $V_{to} \approx$ 0,39 V / 18 m $\Omega$ |  |  |  |

| Diodos $D_3$ e $D_4$      | MUR820G @ $V_{to} \approx$ 0,62 V / 25 m $\Omega$  |  |  |  |

O protótipo de bancada pode ser visto na Figura 9.

Com base nos parâmetros do projeto, calcula-se o ciclo de trabalho, utilizando a relação (10), obtendo-se um valor de aproximadamente 70%. Este valor é relativamente baixo, considerando o elevado ganho de tensão.

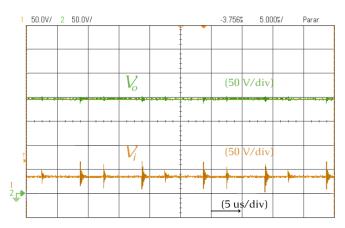

A Figura 10 mostra os sinais de tensão na entrada  $v_i$ e na saída  $v_o$  para a operação em plena carga. Nota-se que o conversor obteve um ganho de tensão próximo de 6, fornecendo em sua saída uma tensão em torno de 200 V a partir de uma tensão de 35 V, conforme previsto pela equação (10).

FIGURA 9. Protótipo experimental.

FIGURA 10. Tensão de entrada  $v_i$  e tensão de saída  $v_o$ .

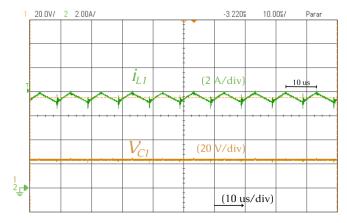

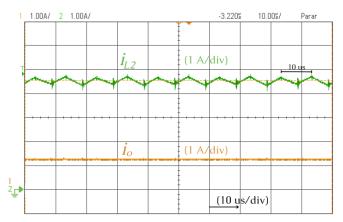

A tensão intermediária sobre o capacitor  $C_1$  apresenta valor médio em torno de 24 V, conforme mostrado na Figura 11. Ao contrário dos demais conversores quadráticos, esse nível de tensão é significativamente baixo e possibilita a utilização de componentes com menor tensão nominal. Na mesma figura, é mostrado o sinal de corrente através do indutor  $L_1$ , destacando sua frequência, que é o dobro da frequência de chaveamento. Essa mesma característica é observada na corrente do indutor  $L_2$ , Figura 12. A componente média da corrente nos indutores 1 e 2, para operação em potência nominal, apresenta valores de 7,4 e 4,7 A, respectivamente, em conformidade com (18) e (20). Também na Figura 12, é apresentada a corrente na carga, com valor médio próximo de 1,26 A.

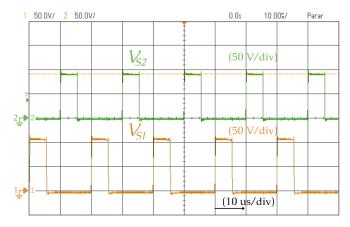

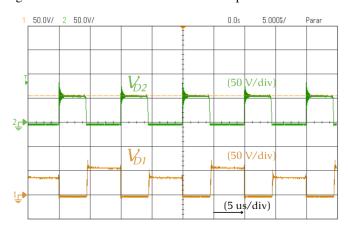

Fica claro a partir da Figura 13 que a tensão nas chaves  $S_1$  e  $S_2$  corresponde a, aproximadamente, metade da tensão

FIGURA 11. Tensão intermediária  $v_{C1}$  e corrente no indutor  $L_1$ .

FIGURA 12. Corrente na carga  $i_o$  e corrente no indutor  $L_2$ .

de saída, validando o principal atributo deste conversor. É possível observar uma diferença de cerca de 15 V entre a máxima tensão sobre cada chave. Tal disparidade deve-se às diferenças intrínsecas entre os componentes que compõem a célula de comutação, especialmente os capacitores de filtro, e denotam a operação em malha aberta. Contudo, não afeta o correto funcionamento da topologia.

FIGURA 13. Tensão de bloqueio nas chaves  $S_1$  e  $S_2$ .

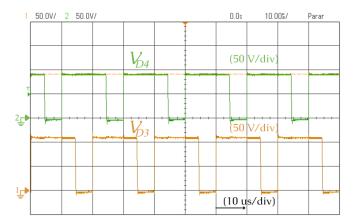

A Figura 14 mostra que a tensão de bloqueio sobre os diodos de saída  $D_3$  e  $D_4$  também equivale à apenas metade

da tensão total de saída  $(v_o)$ . Viabilizando a utilização de componentes mais rápidos e de menor tensão direta, aliviando as perdas de condução e comutação.

FIGURA 14. Tensão de bloqueio nos diodos  $D_3$  e  $D_4$ .

Baixos esforcos de tensão também são observados sobre os diodos do primeiro estágio, conforme mostrado na Figura 15. Observa-se que a máxima tensão suportada pelos diodos  $D_1$  e  $D_2$  é de 57 V e 55 V, respectivamente. A tensão máxima suportada pelo diodo  $D_1$  é de cerca de 16 V maior que o previsto por (12). Tal fato deve-se à divisão não igualitária da tensão de saída entre os capacitores de filtro.

FIGURA 15. Tensão de bloqueio nos diodos  $D_1$  e  $D_2$ .

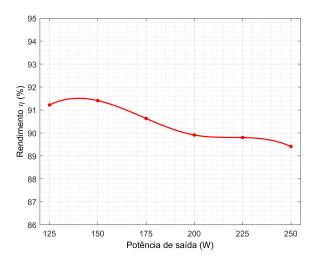

Com o intuito de verificar o desempenho experimental da topologia, a potência na carga foi variada na faixa de 125 a 250 W, mantendo a tensão de saída fixa em 200 V, resultando na curva de rendimento em função da potência, obtida pela razão entre as potências de saída e entrada, apresentada na Figura 16. Inicialmente, é possível verificar que o conversor apresenta bom desempenho para toda a faixa de potência ensaiada, ainda, a estrutura apresentou boa performance para baixas potências, alcançando um rendimento máximo próximo de 92% para uma potência de 150 W. Em plena carga, o conversor obteve um rendimento superior à 89%, sendo este um valor satisfatório dada sua característica quadrática. Deste modo, fica evidente que a redução no esforço de tensão suportada pelos componentes

FIGURA 16. Curva de rendimento experimental.

semicondutores, especialmente pelas chaves, é um fator determinante para a operação de estruturas quadráticas com elevada eficiência.

## VI. CONCLUSÕES

Neste artigo, foi realizado o estudo e proposta de um novo conversor CC-CC não isolado de elevado ganho, derivado do conversor boost convencional. A estrutura estudada possui características interessantes, dentre as quais se destacam a relação quadrática para o ganho estático, baixo esforço de tensão nas chaves, reduzida tensão sobre o capacitor intermediário e diminuição no volume dos elementos magnéticos. Tais pontos possibilitam que o conversor opere com alto ganho, eficiência e densidade de potência.

A máxima tensão suportada pelas chaves semicondutoras não é maior do que a metade da tensão de saída, permitindo a utilização de componentes com menor tensão nominal e baixa resistência de condução, reduzindo as perdas de condução. Baixos níveis de tensão de bloqueio também são observados sobre os diodos. Além disso, a célula de comutação de três-níveis impõe aos elementos reativos uma frequência de operação duas vezes maior que a frequência de chaveamento, tornando viável a utilização de componentes compactos.

Para operação em plena carga, o conversor obteve um ganho de aproximadamente 6, com uma eficiência superior à 89%. Esses valores são significativos, considerando que a estrutura é baseada em conversores quadráticos.

Portanto, o conversor apresentado mostra-se como forte alternativa para aplicações conectadas à rede elétrica, nas quais um elevado ganho de tensão é necessário para elevar os baixos níveis de tensão fornecidos por painéis solares, por exemplo, àqueles exigidos para a correta alimentação do estágio CC-CA, sem que o rendimento e volume da estrutura se tornem pontos limitantes.

#### **AGRADECIMENTOS**

O presente trabalho foi realizado com apoio da Coordenação de Aperfeiçoamento de Pessoal de Nível Superior - Brasil (CAPES) - Código de Financiamento 001.

## **CONTRIBUIÇÕES DOS AUTORES**

ROMEIRO, L.: Conceitualização, Curadoria de dados, Análise de dados, Recebimento de financiamento, Pesquisa, Metodologia, Administração do projeto, Desenvolvimento, implementação e teste de software, Validação de dados e experimentos, Design da apresentação de dados, Redação do manuscrito original, Redação - revisão e edição; BAR-BOSA, L.R.: Supervisão, Redação - revisão e edição; DA SILVA, N.: Disponibilização de ferramentas, Desenvolvimento, implementação e teste de software, Redação - revisão e edição; DE MELO, L.F.: Administração do projeto, Supervisão, Redação - revisão e edição;

#### PLÁGIO E SIMILARIDADE

O artigo foi submetido para verificação de similaridade no sistema Crossref Similarity Check (iThenticate).

## REFERÊNCIAS

- [1] A. A. Dionizio, L. P. Sampaio, S. A. O. da Silva, S. d. J. M. Machado, "Grid-Tied Single-Phase Integrated Zeta Inverter for Photovoltaic Applications", *Energies*, vol. 16, no. 9, April 2023, doi:10.3390/en16093622.

- [2] J. M. de Andrade, M. A. Salvador, R. F. Coelho, T. B. Lazzarin, "General Method for Synthesizing High Gain Step-Up DC-DC Converters Based on Differential Connections", IEEE Transactions on Power Electronics, vol. 35, no. 12, pp. 13239-13254, May 2020, doi:10.1109/TPEL.2020.2996501.

- [3] B. Andres, L. Romitti, A. M. S. S. Andrade, L. Roggia, L. Schuch, "A High Step-Up Isolated DC-DC Converter Based on Cascaded Greinacher Voltage Multiplier", Eletrônica de Potência, vol. 28, no. 1, pp. 52-62, March 2023, doi:https://doi.org/10.18618/REP.2023.1.0038.

- [4] F. Tofoli, D. Tavares, J. Saldanha, "Survey on Topologies Based on The Three-State and Multi-State Switching Cells", IET Power Electronics, vol. 12, no. 5, pp. 967-982, May 2019, doi:https://doi.org/10.1049/ietpel.2018.6003.

- [5] M. F. Guepfrih, G. Waltrich, T. B. Lazzarin, "Comparação Entre Três Conversores CC-CC Não-Isolados de Elevado Ganho Estático Derivados do Conversor Boost", Eletrônica de Potência, vol. 28, no. 3, pp. 216–227, Sept. 2023, doi:https://doi.org/10.18618/REP.2023.3.0006.

- [6] M. Forouzesh, Y. P. Siwakoti, S. A. Gorji, F. Blaabjerg, B. Lehman, "Step-Up DC-DC Converters: A Comprehensive Review of Voltage-Boosting Techniques, Topologies, and Applications", IEEE Transactions on Power Electronics, vol. 32, no. 12, pp. 9143-9178, March 2017, doi:10.1109/TPEL.2017.2652318.

- [7] M. F. Guepfrih, G. Waltrich, T. B. Lazzarin, "Unidirectional Step-Up DC-DC Converter Based on Interleaved Phases, Coupled Inductors, Built-In Transformer, and Voltage Multiplier Cells", IEEE Transactions on Industrial Electronics, vol. 70, no. 3, pp. 2385-2395, May 2023, doi:10.1109/TIE.2022.3170639.

- [8] M. R. S. de Carvalho, E. A. O. Barbosa, F. Bradaschia, L. R. Limongi, M. C. Cavalcanti, "Soft-Switching High Step-Up DC-DC Converter Based on Switched-Capacitor and Autotransformer Voltage Multiplier Cell for PV Systems", IEEE Transactions on Industrial Electronics, vol. 69, no. 12, pp. 12886-12897, Jan. 2022, doi:10.1109/TIE.2022.3142432.

- [9] S. M. Fardahar, M. Sabahi, "New Expandable Switched-Capacitor/Switched-Inductor High-Voltage Conversion Bidirectional DC-DC Converter", IEEE Transactions Power Electronics, vol. 35, no. 3, pp. 2480-2487, Aug. 2020, doi:10.1109/TPEL.2019.2932325.

- [10] Y. Zhang, Y. Gao, L. Zhou, M. Sumner, "A Switched-Capacitor Bidirectional DC-DC Converter With Wide Voltage Gain Range for Electric Vehicles With Hybrid Energy Sources", IEEE Transactions on Power Electronics, vol. 33, no. 11, pp. 9459-9469, Jan. 2018, doi:10.1109/TPEL.2017.2788436.

- [11] M. Forouzesh, Y. Shen, K. Yari, Y. P. Siwakoti, F. Blaabjerg, "High-Efficiency High Step-Up DC-DC Converter With Dual Coupled Inductors for Grid-Connected Photovoltaic Systems", IEEE Transactions on Power Electronics, vol. 33, no. 7, pp. 5967-5982, Aug. 2018, doi:10.1109/TPEL.2017.2746750.

- [12] J. M. de Andrade, M. A. Salvador, R. F. Coelho, T. B. Lazzarin, "Metodologia para derivação de conversores cc-cc elevadores de alto ganho baseados em conexões diferenciais", Eletrônica de Potência, vol. 29, p. e202409, Apr. 2024, doi:10.18618/REP.2024.1.0003.

- [13] M. Rasouli, M. Mehrasa, A. Ganjavi, M. S. Sadabadi, H. Ghoreishy, A. Ale Ahmad, "Lyapunov-Based Control Strategy for a Single-Input Dual-Output Three-Level DC/DC Converter", IEEE Transactions on Industrial Electronics, vol. 70, no. 10, pp. 10486-10495, Nov. 2023, doi:10.1109/TIE.2022.3217610.

- [14] I. A. Ayad, E. Elwarraki, S. U. Ali, S. M. Qaisar, A. Waqar, M. Baghdadi, A. Alzahrani, "Optimized Nonlinear Integral Backstepping Controller for DC-DC Three-Level Boost Converters", IEEE Access, vol. 11, pp. 49794-49805, May 2023, doi:10.1109/ACCESS.2023.3274773.

- [15] J. B. R. F. Cabral, S. V. Oliveira, Y. R. Novaes, "Conversor cc-cc boost quadrático para aplicações em fontes alternativas", Eletrônica de Potência, vol. 18, no. 3, pp. 1064 - 1072, Aug. 2013, doi:https://doi.org/10.18618/REP.2013.3.10641072.

- [16] A. M. S. S. Andrade, M. L. d. S. Martins, "Quadratic-Boost With Stacked Zeta Converter for High Voltage Gain Applications", IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 5, no. 4, pp. 1787-1796, May 2017, doi:10.1109/JESTPE.2017.2706220.

- [17] M. F. Guepfrih, G. Waltrich, T. B. Lazzarin, "Quadratic-boost-doubleflyback converter", IET Power Eletronics, vol. 12, no. 12, pp. 3166-3177, Sept. 2019, doi:https://doi.org/10.1049/iet-pel.2019.0340.

- [18] S. V. K. Naresh, S. Peddapati, M. L. Alghaythi, "Non-Isolated High Gain Quadratic Boost Converter Based on Inductor's Asymmetric Input Voltage", IEEE Access, vol. 9, pp. 162108-162121, Dec. 2021, doi:10.1109/ACCESS.2021.3133581.

- M. Veerachary, M. R. Khuntia, "Design and Analysis of Two-Switch-Based Enhanced Gain Buck-Boost Converters", IEEE Transactions on Industrial Electronics, vol. 69, no. 4, pp. 3577–3587, April 2022, doi:10.1109/TIE.2021.3071696.

- [20] F. G. Nimitti, A. M. S. S. Andrade, "Análise e Desenvolvimento de um Conversor Bidirecional Não Isolado Baseado no Conversor Boos/Buck CC-CC", Eletrônica de Potência, vol. 27, no. 4, pp. 325-334, Oct. 2023, doi:10.18618/REP.2022.4.0006.

- [21] R. Kadri, J.-P. Gaubert, G. Champenois, M. Mostefaï, "Performance analysis of transformless single switch quadratic boost converter for grid connected photovoltaic systems", The XIX International Conference on Electrical Machines - ICEM 2010, pp. 1-7, 2010, doi:10.1109/ICELMACH.2010.5608092.

- [22] I. Barbi, D. C. Martins, Conversores cc-cc básicos não isolados, 4 ed., Dos autores., Florianópolis, 2012.

## DADOS BIOGRÁFICOS

Lucas Romeiro nasceu em Londrina, Paraná. Recebeu o título de Bacharel e Mestre em Engenharia Elétrica pela Universidade Estadual de Londrina, em 2021. Atualmente é aluno do programa de mestrado em Engenharia Elétrica pela mesma instituição. Suas áreas de interesse incluem conversores estáticos de potência, conversores de elevado ganho e fontes alternativas de

Lúcio dos Reis Barbosa possui graduação (1993), mestrado (1996) e doutorado (1999) em Engenharia Elétrica pela Universidade Federal de Uberlândia. Em 2011, realizou pós-doutorado sênior junto ao Núcleo de Pesquisa em Eletrônica de Potência (NUPEP-UFU). Atualmente, é Professor Titular do Departamento de Engenharia Elétrica na Universidade Estadual de Londrina.

## **Original Paper**

Newton da Silva possui doutorado (2012) pela Universidade Estadual de Campinas, mestrado (1994) pela Universidade Federal de Santa Catarina e bacharelado (1991) pela Universidade Federal de Santa Maria, em Engenharia Elétrica. Atualmente é professor da Universidade Estadual de Londrina na Graduação e Pós-graduação. Suas áreas de interesse são eletrônica de potência, qualidade de energia, sistemas de energia conectados à rede elétrica e controle digital de conversores.

Leonimer Flávio de Melo possui graduação (1985) e mestrado em Engenharia Elétrica (2002) e doutorado em Engenharia Mecânica pela Universi-

dade Estadual de Campinas (2007). Atualmente é professor associado da Universidade Estadual de Londrina (UEL) na graduação e pós-graduação Engenharia Elétrica (UEL) e do programa de Doutorado Associado em Engenharia Elétrica (UEL/UTFPR-CP). Tem experiência na área de Engenharia Elétrica e Engenharia Mecatrônica, atuando principalmente nas seguintes áreas: automação industrial, engenharia de produção, aprendizado de máquina, deep learning e redes neurais artificiais.